13395 682

Изобретение относится к вь гчисли-проверяемом блоке 1 на выходные (состельной технике и автоматике и можеттояние О триггеров 11) и входные

быть использовано для проверки логи-(состояние 1 триггеров 11).

ческих схем цифровых узлов ЭВМ. При установке в разрядах поля упЦель изобретения - расширение фун-управление блока 7 команды II (едикциональных возможностей за счет pea-ничный сигнал на входе 2 дешифратора

лизации возможности задания любой9) сигналом переполнения счетчика 8

временной диаграммы сигналов возбуж-осуществляется возбуждение через эледения входных контактов контролируе-ю мент И 19 счетных входов счетчиков

мого блока.27 в каналах 2 входных воздействий,

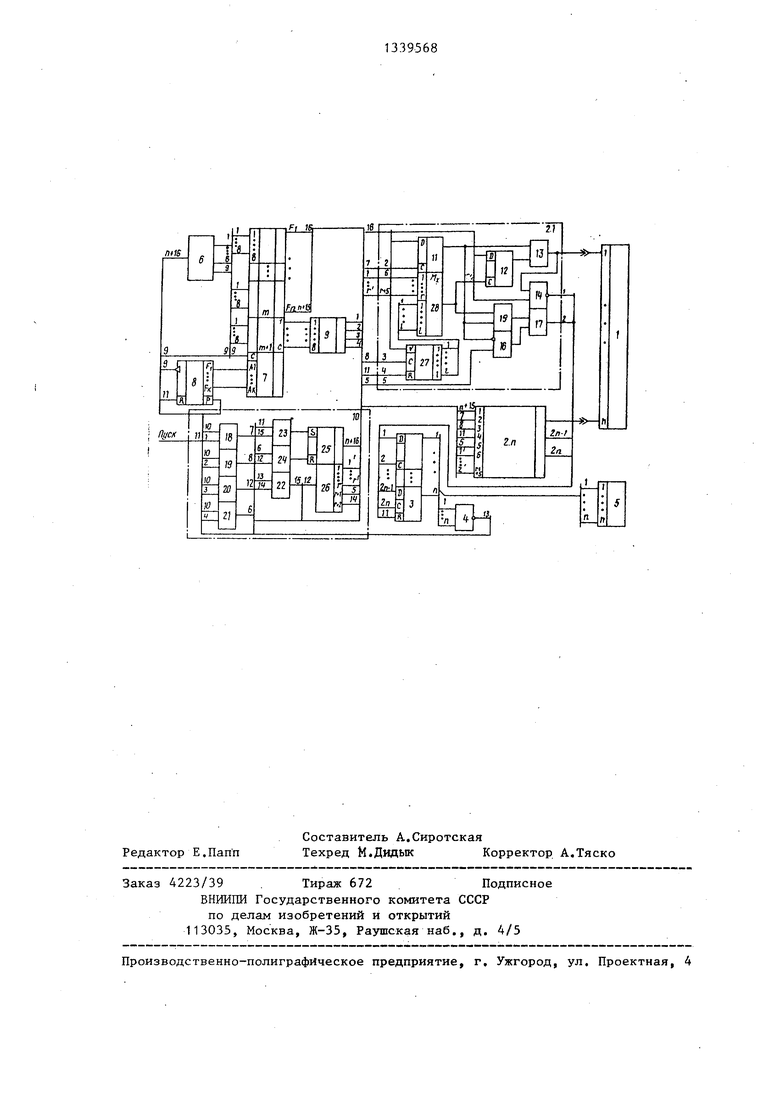

На чертеже представлена функцио-и, в случае наличия на каких-либо нальная схема устройства.выходах поля тестов блока 7 единичных Устройство содержит контролируе-сигналов, счетчики 27 в соответствую- мый блок 1, каналы 2,...,2п входных15 щих каналах 2 входных воздействий воздействий, группу 3 триггеров оши-изменяют свое состояние на 1. бок, элемент ИЛИ-НЕ 4, блок 5 инди-С целью задания различных времен- наций, генератор 6 тестов, блок 7 па- ных задержек в каналах 2 входных мяти тестов, счетчик В байтов, дешиф-воздействий команда II должна повто- ратор 9, блок 10 управления, триггеры20 ряться г раз. После окончания послед- 11 и 12., элемент ИЛИ 13, элемент 14 .ней команды II каналы 2 входных воз- сравнения, элементы И 15 и 16,, эле-действий подготовлены для выполнения мент ИЛИ 17, элементы И 18 - 22, эле-команд III.

менты ИЛИ 23 и 24, триггер 25, блокПри установке в разрядах управле- 26 хранения временных задаржек, счет-25 ния блока 7 команды III (единичный чик 27, мультиплексор 28.сигнал на выходе 3 дешифратора 9) Устройство включается в работу присигналом переполнения счетчика 8 поступлении сигнала Пуск. Данныйпроизводится открытие элемента И 20, сигнал осуществляет сброс счетчиковсигнал с выхода которого производят 8 и 27 и устанавливает через элемент30 запуск блока 26 хранения временных ИЛИ 23 триггер 25 в единичное состоя-задержек и устанавливает через эле- ние. Сигнал с выхода триггера 25мент ИЛИ 24 триггер 25 в нулевое сос- включает в работу генератор 6. Сигна-,тояние. Последним осуществляется ослы с выходов генератора 6 возбуждаюттанов генератора 6. информационные входы блока 7 (выходы35

1,...,8) и его синхровход (выход 9).Сигналы с выходов (1,...,г) блока

Под управлением сигналов с выходов26 хранения временных задержек поссчетчика 8 производится последова-ледовательно возбуждают информацион-

тельное побайтовое занесение информа-ные входы мультиплексоров 28. Время

ции в блок 7. Байт (п+1) является40 появления сигналов на выходе мультипбайтом команд.лексоров 28 определяется кодами,

В устройстве реализуется выполне-установленными на соответствующих ние следуюш;их команд: задания выход-счетчиках 27. Сигналы с выходов муль- ных контактов проверяемого блока (ко-типлексоров 28 устанавливают триггеры манда I), задания временных задержек45 12 в состояние, соответствующее тес- сигналов на контактах проверяемоготовому коду, установленному на блоке блока (команда II), тестового контро- 7, тем самым производится через эле- ля проверяемого блока (команда III)мент ИЛИ 13 возбуждение соответствую- и окончания контроля (команда IV).щими сигналами входных контактов про-

При установке в разрядах поля50 веряемого блока 1. Одновременно сиг- управления блока 7 команды I (единич- налами с выходов мультиплексоров 28

ный сигнал на входе 1 дешифратора 9)возбуждаются соответствующие элементы сигналом переполнения счетчика 8 осу- И 15 и через элемент ИЛИ 17 произвоществляется открытие элемента И 18дится установка соответствующих триги в каналах 2 входных воздействий55 геров ошибок 3 в состояние 1 при триггеры 11 устанавливаются в состоя- несравнении на схемах 14 сигналов на

ние, соответствующее коду в разрядахконтактах блока 1 с сигналами на вы(F,,...,F) блока 7. Таким образом,ходах соответствующих разрядов блока

производится разделение контактов в7 памяти тестов.

Сигналом с выхода (г+1) блока 26 хранения временных задержек открываются элементы И 16 в каналах 2, обслуживающих входные контакты проверяемого блока 1. Сигналы с выходов элементов И 16 через элемент ИЛИ 17 устанавливают в единичное состояние соответствующие триггеры ошибок, при несравнении сигналов на входных контактах проверяемого блока 1 и сигналов на выходах соответствующих разрядов блока 7 памяти тестов.

Сигналом с выхода (г+2) блока 26 хранения временных задержек на элементе И 22 осуществляется анализ состояния триггеров 3 ощибок и, в случа отсутствия ощибок, сигналом с выходы элемента И 22 производится установка через элемент ИЛИ 23 триггера 25 в единичное состояние, т.е. производится запуск генератора 6 для вьщачи последующей информации тестовой проверки. При установке в разрядах поля управления блока 7 команды IV (еди- ничный сигнал на выходе 4 дешифратора 9) сигналом переполнения счетчика 8 осуществляется возбуждение элемент И 21, сигнал с выхода которого через элемент ИЛИ 24 устанавливает в нулевое состояние триггер 25, и генератор 6 останавливается, что соответствует окончанию работы по контролю блока 1.

Формула изобретения

Устройство для контроля логических блоков, содержащее генератор тестов, блок памяти тестов, счетчик байтов, дешифратор, группу триггеров ощибки, элемент ИЛИ-НЕ , блок индикации, п каналов входных воздействий (п - число входов) выходов контролируемого логического блока, блок упра- 45 йены с входами блока индикации и элевления, который содержит блок хранения временных задержек, три элемента И, триггер, два элемента ИЛИ, а каждый i-й канал входных воздействий (,...,п) содержит два триггера, два элемента И, два элемента ИЛИ, элемент сравнения, причем информационные входы блока памяти тестов соединены с выходами генератора тестов.

выход признака синхронизации которого gg дами элементов сравнения одноименных соединен с синхровходом блока памяти каналов входных воздействий и являются выходами устройства для подключения к входам-выходам контролируемого

тестов и счетным входом счетчика байтов, разрядные выходы которого соединены с адресными входами блока памяти

логического блока, выходы элементов

5

0

тестов, ВЫХОДИ поля управления которого соединены с информационными входами дешифратора, первый и второй выходы которого соединены с первыми входами первого и второго элементов И блока управления соответственно, выход второго элемента И блока управления соединен с первым входом перво- 0 го элемента ИЛИ блока управления выход которого соединен с входом сброса триггера блока управления, выход которого соединен с входом разрешения генератора тестов, вход пуска устройства -соединен с первым входом второго элемента ИЛИ блока управления, входом сброса счетчика байтов и входами сброса триггеров ошибки группы, выход второго элемента ИЛИ блока управления соединен с входом установки триггера блока управленияJ выход переполнения счетчика байтов соединен с JBTO- рым входом первого элемента И блока управления, выходы поля тестов блока памяти тестов соединен с D-входами первых и вторых триггеров соответствующих каналов входных воздействий, выход первого элемента И блока управления соединен с вторым входом первого элемента ИЛИ блока управления и с входом синхронизации блока хранения временных задержек, выход признака начала регистрации.отрезка которого соединен с прямьми входами первых элементов И всех каналов входных воздействий, выходы первых и вторых элементов И всех каналов входных воздействий соединены с первыми и вторыми входами первых элементов ИЛИ соответствующих каналов входных воздействий, выходы первых элементов ИЛИ всех каналов входных воздействий соединены с входами соответствующих триггеров ошибки группы, выходы которых соеди5

0

5

0

0

мента ИЛИ-НЕ, выход которого соединен с первым входом третьего элемента И блока управления, выходы вторых триггеров всех каналов входных воздействий соединены с первыми входами вторых элементов ИЛИ одноименных каналов входных воздействий, выходы вторых элементов ИЛИ всех каналов входных воздействий соединены с первыми зхологического блока, выходы элементов

сравнения всех каналов входньпс воздействий соединены с D-входами соот- в етствуюпщх триггеров группы, выход третьего элемента И блока управления соединен с вторым входом второго элемента ИЛИ блока управления, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации возможности задания любой временной диаграммы сигналов возбуждения входных контактов контролируемого блока, блок управления содержит четвертый и пятый

элементы И, а каждый из каналов вход- 15 дами вторых триггеров и вторыми вхоных воздействий содержит мультиплекнения счетчика байтов соединен с вторым входом второго элемента И, с первыми входами четвертого и пятого эле- ментов И блока управления, вторые входы которых соединены с четвертым и пятым выходами дешифратора соответственно, выход четвертого элемента И блока управления соединен с С-входа- ми первых триггеров всех каналов входных воздействий, выходы первых триггеров всех каналов входных воздействий соединены с вторым входом второго элемента ИЛИ первым входом второго элемента И и инверсным входом

первого элемента И одноименных каналов входных воздействий, вторые входы элементов сравнения всех каналов входных воздейств.ий соединены с соответствующими выходами поля тестов блока памяти тестов и с входами разрешения счетчиков одноименных каналов входных воздействий, разрядные выходы которых соединены с адресными входами мультиплексоров соответствующих каналов входных воздействий, выходы мультиплексоров всех каналов входных воздействий соединены с С-вхо

дами вторых элементов И одноименных каналов входных воздействий, информационные входы мультиплексоров всех каналов входньпс воздействий соединены с группой выходов поля времени задания подачи входных воздействий блока хранения временных задаржек, выход признака начала контроля которого соединен с вторым входом третьего эле- мента И блока управления, выход пятого элемента И блока управления соединен со счетным входом счетчиков всех каналов входных воздействий, входы сброса этих счетчиков соединены с входом пуска устройства.

Редактор Е,Папп

Составитель А,Сиротская

Техред М.Дидык Корректор А.Тяско

Заказ 4223/39 . Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1228109A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1111171A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1280396A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано для проверки логических схем цифровых узлов ЭВМ. Целью изобретения является расширение функциональных возможностей за счет возможности задания любой временной диаграммы сигналов возбуждения входных контактов проверяемого блока. Цель достигается путем введения в блок управления устройства узла временных задержек, а в каждый блок формирования входных воздействий - мультиплексора, информационные входы которого подключены к выходам узла временных задержек, а адресные входы - к выходам счетчика, код на котором определяет время появления сигнала в соответствии с временной диаграммой работы проверяемого узла. 1 ил. (Л со 00 со ел О5 00

| Распределитель импульсов с обнаружением ошибок | 1980 |

|

SU955074A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1228109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-02-04—Подача