1

Изобретение относится к импульсной технике и может быть использовано в вычислительной технике и в автоматике.

Цель изобретения - повышение надежности регистра.

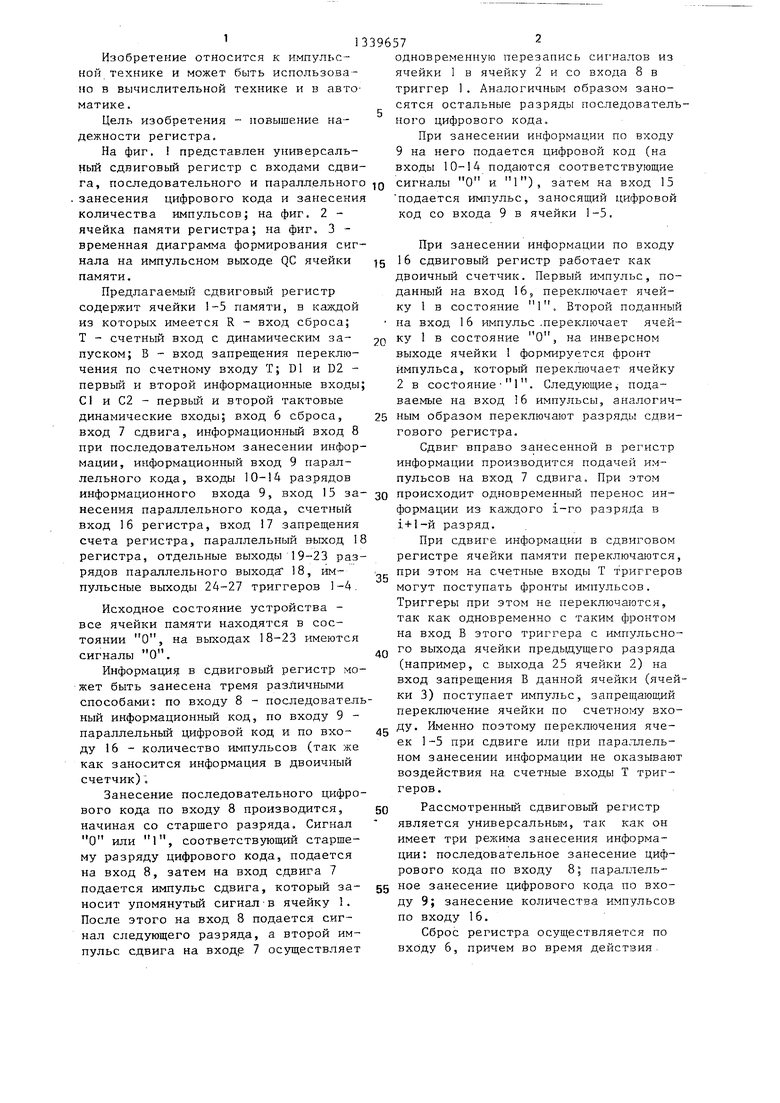

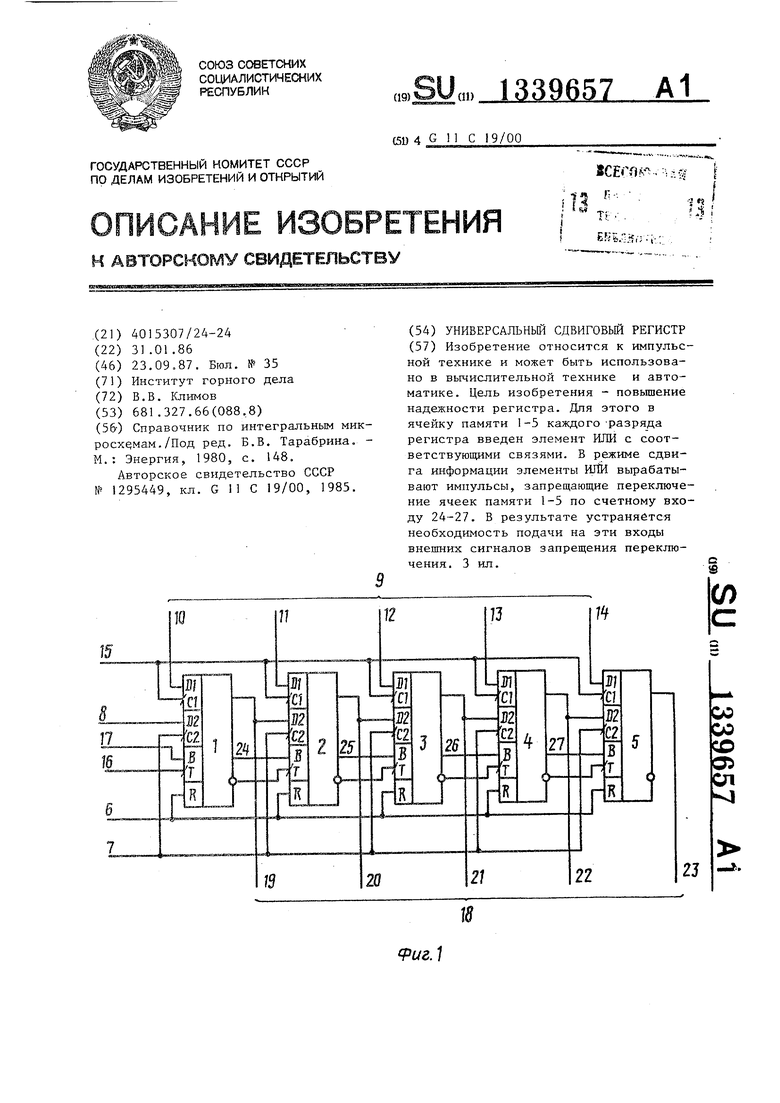

На фиг. представлен универсальный сдвиговый регистр с входами сдвига, последовательного и параллельного Q сигналы О и 1), затем на вход 15

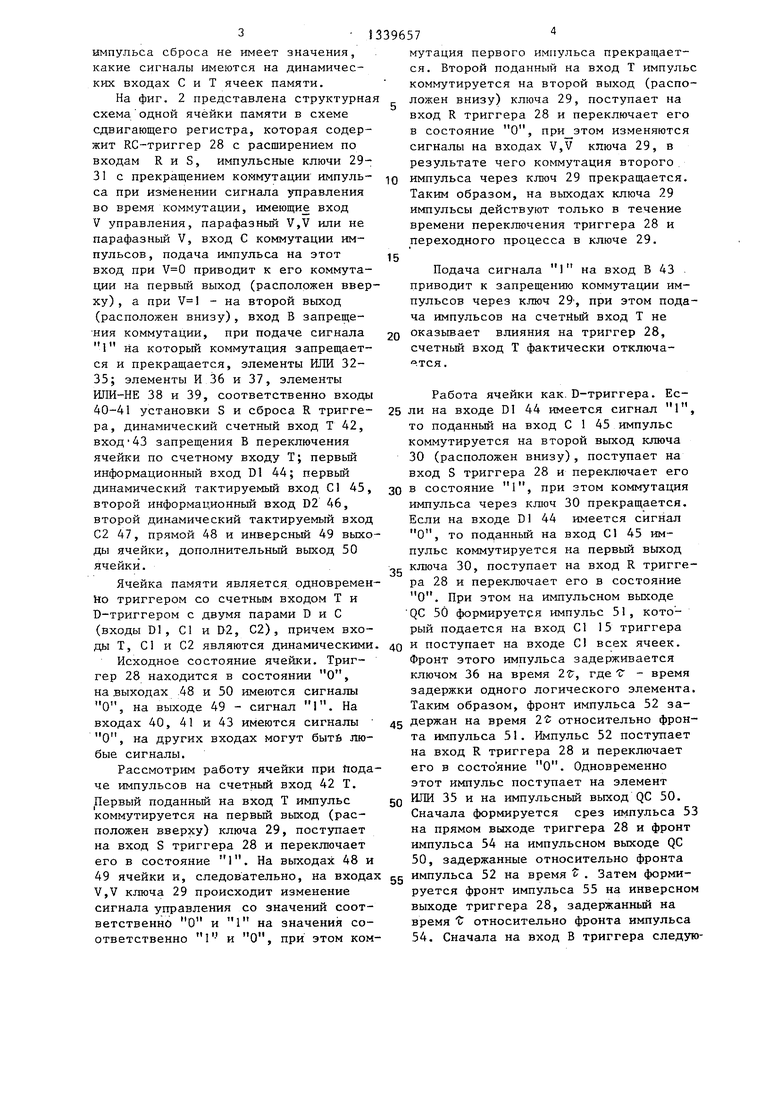

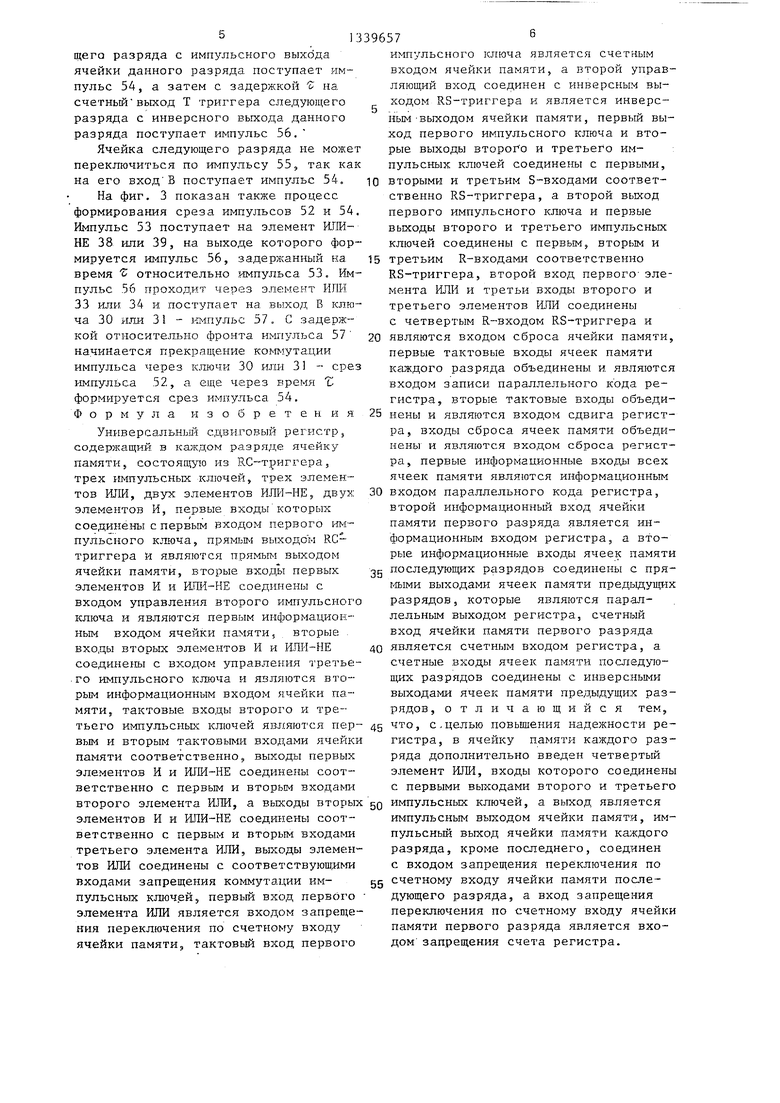

занесения цифрового кода и занесения количества импульсов; на фиг, 2 - ячейка памяти регистра; на фиг. 3 - временная диаграмма формирования сигнала на импульсном выходе QC ячейки памяти.

Предлагаемый сдвиговый регистр содержит ячейки 1-5 памяти, в каж,дой из которых имеется R - вход сброса; Т - счетный вход с динамическим запуском; В - вход запрещения переключения по счетному входу Т; D1 и D2 - первый и второй информационные входы С1 и С2 - первый и второй тактовые динамические входы; вход 6 сброса, вход 7 сдвига, информационный вход 8 при последовательном занесении информации, информационный вход 9 параллельного кода, входы 10-14 разрядов информационного входа 9, вход 15 занесения параллельного кода, счетный вход 16 регистра, вход 17 запрещения счета регистра, параллельнгзш выход 18 регистра, отдельные выходы 19-23 разрядов параллельного выхода: 18, импульсные выходы 24-27 триггеров 1-4.

Исходное состояние устройства - все ячейки памяти находятся в состоянии О, на выходах 18-23 имеются сигналы О.

Информаци5 в сдвиговый регистр может быть занесена тремя различными способами: по входу 8 - последовательный информационный код, по входу 9 - параллельный цифровой код и по входу 16 - количество импульсов (так же как заносится информация в двоичный счетчик).

Занесение последовательного цифрового кода по входу 8 производится, начиная со старшего разряда. Сигнал О или 1, соответствующий старшему разряду цифрового кода, подается на вход 8, затем на вход сдвига 7 подается импульс сдвига, который заносит упомянутый сигналв ячейку I. После этого на вход 8 подается сигнал следующего разряда, а второй импульс сдвига на входр 7 осуществляет

3396572

одновременную перезапись сиг налов из ячейки 1 в ячейку 2 и со входа 8 в триггер 1. Аналогичным образом заносятся остальные разряды последовательного цифрового кода.

При занесении информации по входу 9 на него подается цифровой код (на входы 10-14 подаются соответствующие

подается импульс, заносящий цифровой код со входа 9 в ячейки 1-5.

При занесении информации по входу

16 сдвиговый регистр работает как

двоичный счетчик. Первый импульс, поданный на вход 16, переключает ячейку 1 в состояние 1. Второй поданный на вход 16 импульс .переключает ячейку 1 в состояние О, на инверсном выходе ячейки 1 формируется фронт импульса, который переключает ячейку 2 в сос Гояние 1. Следующие, подаваемые на вход 16 импульсы, аналогичным образом переключают разрядь сдвигового регистра.

Сдвиг вправо занесенной в регистр информации производится подачей импульсов на вход 7 сдвига. При этом

происходит одновременный перенос информации из каждого i-ro разряда в i+i-й разряд.

При сдвиге информации в сдвиговом регистре ячейки памяти переключаются, при этом на счетные входы Т триггеров могут поступать фронты импульсов. Триггеры при этом не переключаются, так как одновременно с таким фронтом на вход В этого триггера с импульсного выхода ячейки предыдущего разряда (например, с выхода 25 ячейки 2) на вход запрещения В данной ячейки (ячейки 3) поступает импульс, запрещаюощй переключение ячейки по счетному входу. Именно поэтому переклЕочения ячеек 1 -5 при сдвиге или при пара;глель- ном занесении информации не оказывают воздействия на счетные входы Т триггеров.

Рассмотренный сдвиговый регистр является универсальным, так как он имеет три режима занесения информации: последовательное занесение цифрового кода по входу 8; параллельное занесение цифрового кода по входу 9; занесение количества импульсов по входу 16.

Сброс регистра осуществляется по входу 6, причем во время действия

10

3- 1339657

импульса сброса не имеет значения, какие сигналы имеются на динамических входах С и Т ячеек памяти.

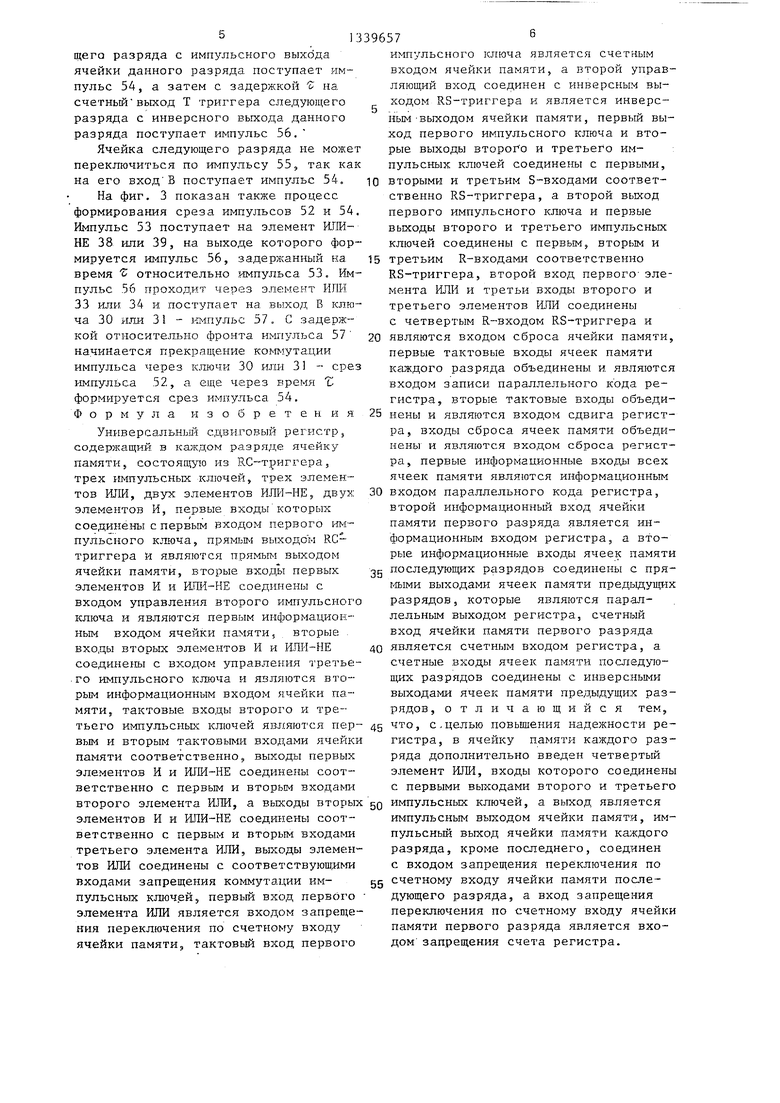

На фиг. 2 представлена структурная схема одной ячейки памяти в схеме сдвигающего регистра, которая содержит КС-триггер 28 с расширением по входам R и S, импульсные ключи 29- 31 с прекращением коммутации импульса при изменении сигнала управления во время коммутации, имеющие вход V управления, парафазный V,V или не парафазный V, вход С коммутации импульсов , подача импульса на этот вход при приводит к его коммутации на первый выход (расположен вверху) , а при V - на второй выход (расположен внизу), вход В запреще- ния коммутации, при подаче сигнала 1 на который коммутация запрещается и прекращается, элементы ИЛИ 32- 35; элементы И 36 и 37, элементы ИПИ-НЕ 38 и 39, соответственно входы

15

20

мутация первого импульса прекращается. Второй поданный на вход Т импульс коммутируется на второй выход (расположен внизу) ключа 29, поступает на вход R триггера 28 и переключает его в состояние О, при этом изменяются сигналы на входах V,V ключа 29, в результате чего коммутация второго импульса через ключ 29 прекращается. Таким образом, на выходах ключа 29 импульсы действуют только в течение времени переключения триггера 28 и переходного процесса в ключе 29.

Подача сигнала 1 на вход В 43 . приводит к запрещению коммутации импульсов через ключ 29, при этом подача импульсов на счетйый вход Т не оказьшает влияния на триггер 28, счетньй вход Т фактически отключа- °.тся.

Работа ячейки как. D-триггера. Ес40-41 установки S и сброса R тригге- 25 ли на входе D1 44 имеется сигнал 1,

ра, динамический счетный вход Т 42, вход43 запрещения В переключения ячейки по счетному входу Т; первый информационный вход D1 44; первый динамический тактируемый вход С1 45, второй информационный вход D2 46, второй динамический тактируемый вход С2 47, прямой 48 и инверсный 49 выходы ячейки, дополнительный выход 50 ячейки.

Ячейка памяти является одновременно триггером со счетным входом Т и D-триггером с двумя парами D и С (входы D, С1 и D2, С2), причем входы Т, С и С2 являются динамическими.

Исходное состояние ячейки. Триггер 28 находится в состоянии О, на выходах 48 и 50 имеются сигналы О, на выходе 49 - сигнал 1, На входах 40, 41 и 43 имеются сигналы О, на других входах могут быть любые сигналы.

Рассмотрим работу ячейки при Подаче импульсов на счетный вход 42 Т. Первый поданный на вход Т импульс коммутируется на первый выход (расположен вверху) ключа 29, поступает на вход S триггера 28 и переключает его в состояние 1. На выходах 48 и

49 ячейки и, следовательно, на входах 55 импульса 52 на время - . Затем форми- V,V ключа 29 происходит изменение руется фронт импульса 55 на инверсном сигнала управления со значений соответственно О и 1 на значения сои 1 на значения ответственно 1 и О, при этом комвыходе триггера 28, задержанный на время t относительно фронта импульса 54. Сначала на вход В триггера следую

мутация первого импульса прекращается. Второй поданный на вход Т импульс коммутируется на второй выход (расположен внизу) ключа 29, поступает на вход R триггера 28 и переключает его в состояние О, при этом изменяются сигналы на входах V,V ключа 29, в результате чего коммутация второго импульса через ключ 29 прекращается. Таким образом, на выходах ключа 29 импульсы действуют только в течение времени переключения триггера 28 и переходного процесса в ключе 29.

Подача сигнала 1 на вход В 43 . приводит к запрещению коммутации импульсов через ключ 29, при этом подача импульсов на счетйый вход Т не оказьшает влияния на триггер 28, счетньй вход Т фактически отключа- °.тся.

Работа ячейки как. D-триггера. Есто поданный на вход С 1 45 импульс коммутируется на второй выход ключа 30 (расположен внизу), поступает на вход S триггера 28 и переключает его

0 в состояние 1, при этом коммутация импульса через ключ 30 прекращается. Если на входе D1 44 имеется сигнал О, то поданный на вход С1 45 импульс коммутируется на первый вЬгход

J- ключа 30, поступает на вход R триггера 28 и переключает его в состояние О. При этом на иьшульсном выходе QC 50 формируется импульс 51, который подается на вход С1 15 триггера

0 и поступает на входе С1 всех ячеек. Фронт этого импульса задерживается ключом 36 на время 2Т, где - время задержки одного логического элемента. Таким образом, фронт импульса 52 заg держан на время 2 относительно фронта импульса 51. Импульс 52 поступает на вход R триггера 28 и переключает его в состояние О. Одновременно этот импульс поступает на элемент ИЛИ 35 и на импульсньй выход QC 50. Сначала формируется срез импульса 53 на прямом выходе триггера 28 и фронт импульса 54 на импульсном выходе QC 50, задержанные относительно фронта

0

импульса 52 на время - . Затем форми- руется фронт импульса 55 на инверсном

выходе триггера 28, задержанный на время t относительно фронта импульса 54. Сначала на вход В триггера следую513396576

вдего разряда с импульсного выхода импульсного ключа является счетным ячейки данного разряда поступает им- входом ячейки памяти, а второй управ- пульс 54, а затем с задержкой ь на ляющий вход соединен с инверсным высчетньм выход Т триггера следующего ходом RS-триггера и является инверсb - . разряда с инверсного выхода данного нын-выходом ячейки памяти, первый выразряда поступает импульс 56. ход первого импульсного ключа и втоЯчейка следующего разряда не может рые выходы второг о и третьего им- переключиться по импульсу 55, так как пульсных ключей соединены с первыми, на его вход В поступает импульс 54. ю вторыми и третьим S-входами соответНа фиг. 3 показан также процесс ственно RS-триггера, а второй формирования среза импульсов 52 и 54, первого импульсного ключа и первые Импульс 53 поступает на элемент И1Н- выходы второго и третьего импульсных НЕ 38 или 39, на выходе которого фор- ключей соединены с первым, вторым и мируется импульс 56, задержанный на 15 третьим R-входами соответственно время S относительно импульса 53, Им- П,3-триггера, второй вход первого эле- пульс 56 проходит через элемент ИЛИ мента ИЛИ и третьи входы второго и 33 1-1ПИ 34 и поступает на выход В клю- третьего элементов ИЛИ соединены ча 30 или 31 - импульс 57. С задерж- с четвертым К-входом RS-триггера и кой относительно фронта импульса 57 20 являются входом сброса ячейки памяти, начинается прекращение коммутации первые тактовые входы ячеек памяти импульса через ключи 30 или 31 - срез кгикдого разряда объединены и являются импульса 52, а еще через время Z входом записи параллельного кода реформируется срез импульса 54.гистра, вторые тактовые входы объеди- Формула изобретения 25 нены и являются входом сдвига регист- Ун1-гверсальньй сдв11говый регистр, ра, входы сброса ячеек памяти объеди- содержащий в кгикдом разряде ячейку йены и являются входом сброса регист- памяти, состоящую из RC-триггера, ра, первые информационные входы всех трех импульсных ключей, трех элемен- ячеек памяти являются информационным тов ИЛИ, двух элементов ИЛИ-НЕ, двух 30 входом параллельного кода регистра, элементов И, первые входы которых второй информационный вход ячейки соединены с первым рходом первого им- памяти первого разряда является ин- пульсного ключа, прямым выходом RC- формационным входом регистра, а вто- триггера И являются прямым выходом рые информационные входы ячеек памяти ячейки памяти, вторые входы первых 35 последующих разрядов соединены с пря- элементов И и ИШ-1-НЕ соединены с г-1ыми выходами ячеек памяти предыдущих входом управления второго импульсного разрядов, которые являются парал- ключа и являются первым информацион- лельным выходом регистра, счетный ным входом ячейки памяти, вторые . вход ячейки памяти первого разряда входы вторых элементов И и ИЛИ-НЕ 40 является счетным входом регистра, а соединены с входом управления третье- счетные входы ячеек памяти последую- го импульсного ключа и являются ВТО- щих разрядов соединены с инверсны-ми рым информационным входом ячейки па- выходами ячеек памяти предыдущих раз- мяти, тактовые входы второго и тре- рядов, отличающийся тем, тьего импульсных ключей являются пер-- 45 что, с,целью повьшения надежности ре- вым и вторым тактовыми входами ячейки гистра, в ячейку памяти каждого раз- памяти соответственно, выходы первых ряда дополнитешьно введен четвертый элементов И и ЙГШ-НЕ соединены соот- элемент ИЛИ, входы которого соединены ветственно с первым и вторьм входа и с первыми выходами второго и третьего второго элемента ИЛИ, а выходы вторых gg импульсных ключей, а выход является элементов И и ИПИ-НЕ соединены соот- импульсным выходом ячейки памяти, им- ветственно с первым и вторым входами пульсный выход ячейки памяти каждого третьего элемента ИЛИ, выходы элемен- разряда, кроме последнего, соединен тов ИЛИ соединены с соответствуюш51ми с входом запрещения переключения по входами запрещения ког мутации им- 55 счетному входу ячейки памяти после- пульсных ключей, первый вход первого дующего разряда, а вход запрещения элемента РШИ является входом запреще- переключения по счетному входу ячейки НИН переключения по счетному входу памяти первого разряда является вхо- ячейки памяти, тактовьй вход первого дом запрещения счета регистра.

50

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный сдвиговый регистр | 1985 |

|

SU1295449A1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Устройство для выделения признаков изображения | 1987 |

|

SU1418774A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительной технике и автоматике. Цель изобретения - повышение надежности регистра. Для этого в ячейку памяти 1-5 каждого-разряда регистра введен элемент ИЛИ с соответствующими связями. В режиме сдвига информации элементы Ш1И вырабатывают импульсы, запрещающие переключение ячеек памяти 1-5 по счетному входу 24-27. В результате устраняется необходимость подачи на эти входы внешних сигналов запрещения переклю иг.1

Составитель С. Королев Редактор Н. Лазаренко Техред М.Дидык / Корректор

ЗакаГ4232/44 Тираж 589 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| ) Справочник по интегральным микросхемам./Под ред | |||

| Б.В, Тарабрина, - М.: Энергия, 1980, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Универсальный сдвиговый регистр | 1985 |

|

SU1295449A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-23—Публикация

1986-01-31—Подача