W

f5

Изобретение относится к цифровой и импульсной технике и может быть использовано в вычислительной технике j автоматике, а также в микросхемотехнике.

Цель изобретения - распгарение области применения регистра за счет возможности счета импульсов.

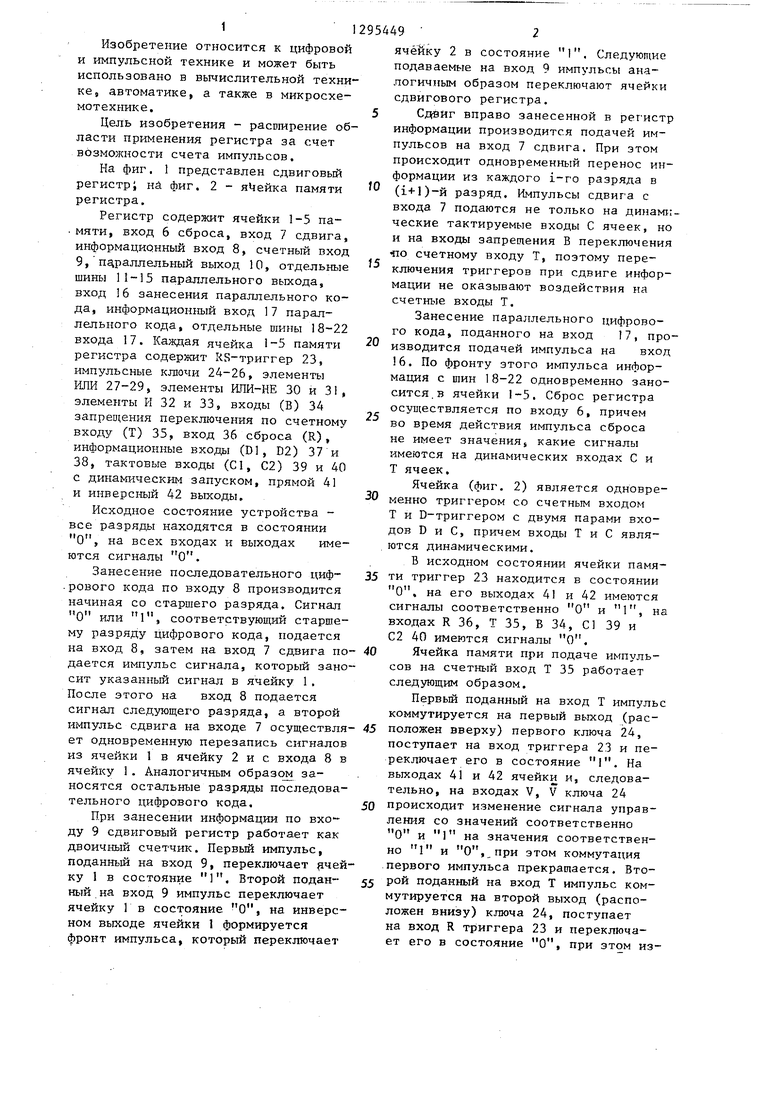

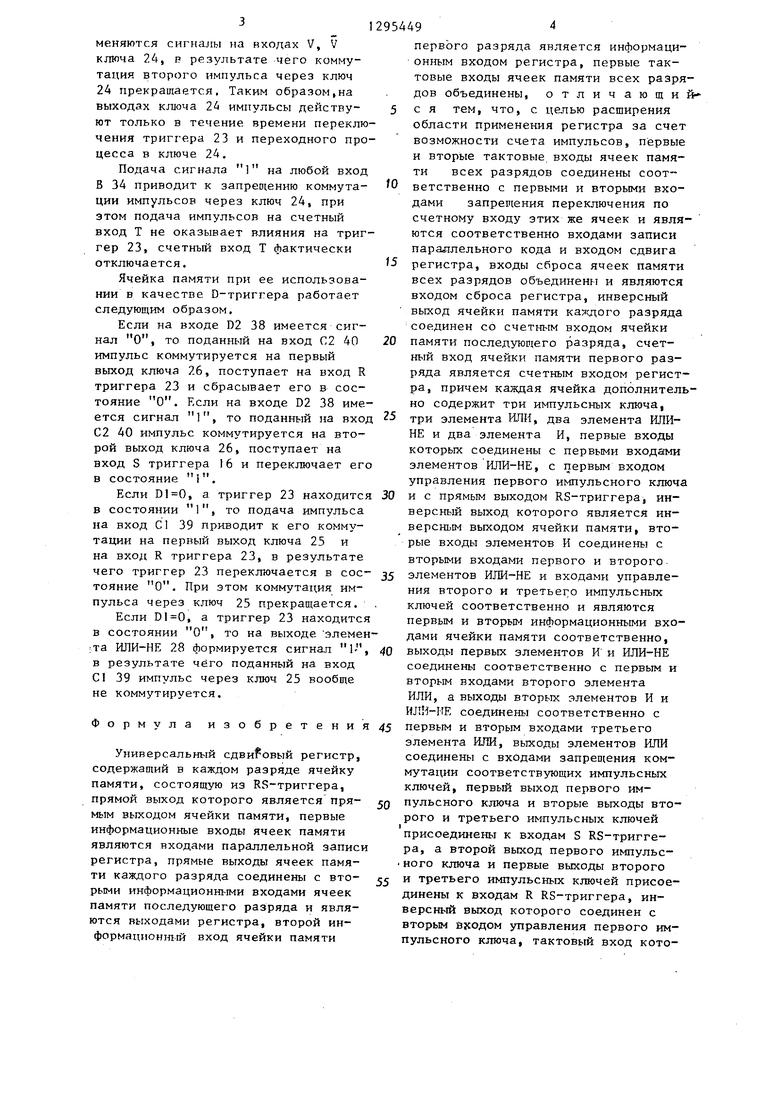

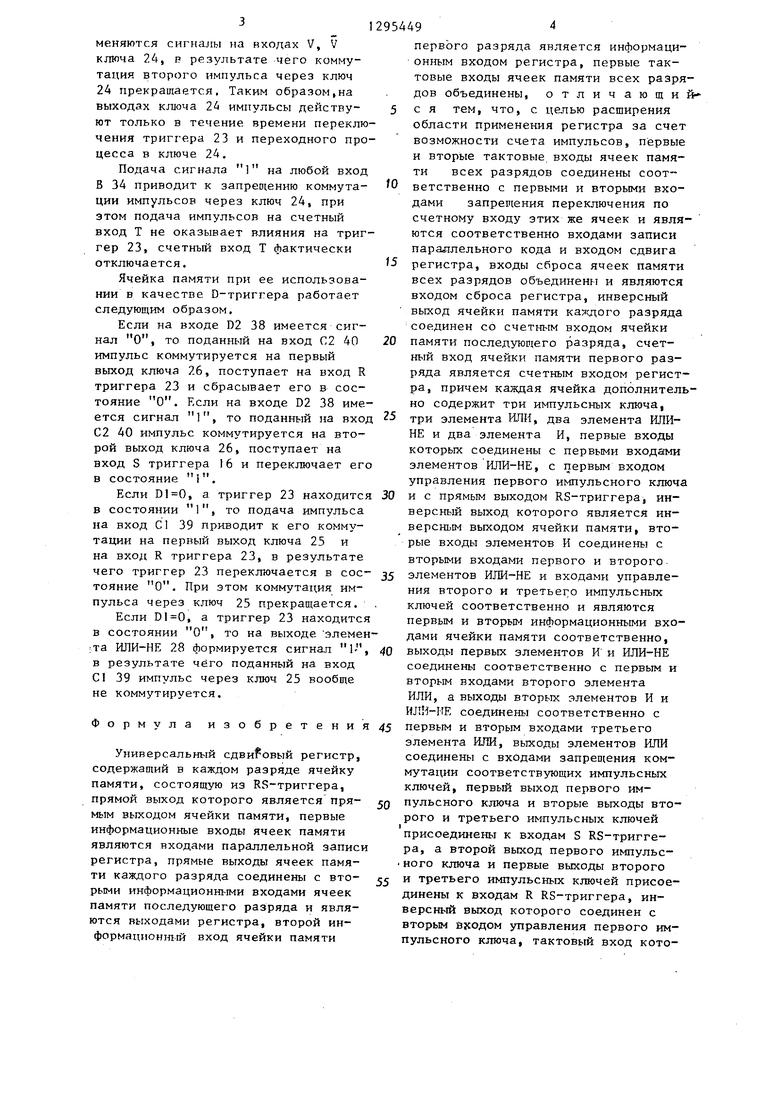

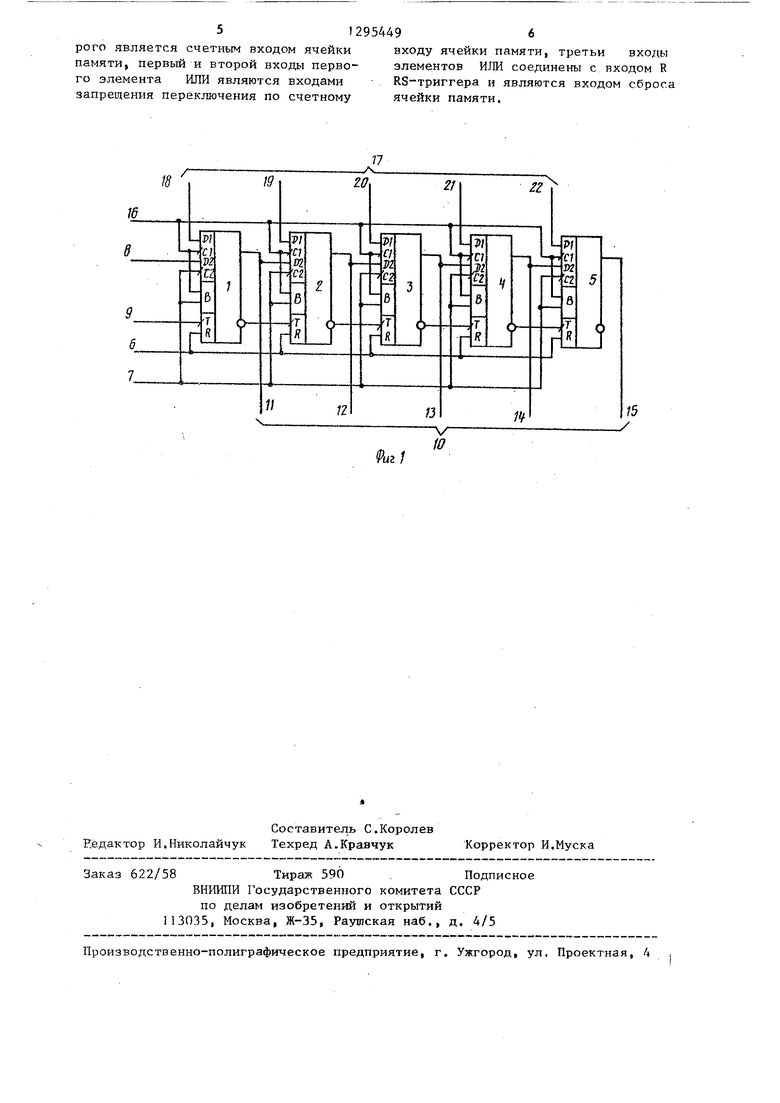

На фиг, 1 представлен сдвиговый регистрi ни фиг. 2 - ячейка памяти регистра.

Регистр содержит ячейки 1-5 па- . мяти, вход 6 сброса, вход 7 сдвига, информационный вход 8, счетный вход 9, падаллельный выход 10, отдельные шины 11-15 параллельного выхода, вход 6 занесения параллельного кода, информационный вход 17 параллельного кода, отдельные шины 18-22 входа 17. Каждая ячейка 1-5 памяти регистра содержит KS-триггер 23, импульсные ключи 24-26, элементы ИЛИ 27-29, элементы ИЛИ-НЕ 30 и 31, элементы И 32 и 33, входы (В) 34 запреп ения переключения по счетному входу (Т) 35, вход 36 сброса (R), информационные входы (D1, D2) 37 и 38, тактовые входы (С1, С2) 39 и 40 с динамическим запуском, прямой 41 и инвере1шй 42 выходы.

Исходное состояние устройства - все разряды находятся в состоянии О, на всех входах и выходах имеются сигналы О.

Занесение последовательного циф- .рового кода по входу 8 производится начиная со старшего разряда. Сигнал О или 1, соответствующий старшему разряду Цифрового кода, подается на вход 8, затем на вход 7 сдвига по- 40 дается импульс сигнала, который заносит указанный сигнал в ячейку 1. После этого на вход 8 подается сигнал следующего разряда, а второй

ячейку 2 в состояние 1, Следующи подаваемые на вход 9 импульсы аналогичным образом переключают ячейк сдвигового регистра.

Сдвиг вправо занесенной в регис информации производится подачей им пульсов на вход 7 сдвига. При зтом происходит одновременный перенос и формации из каждого i-ro разряда в (1-|-1)-й разряд. Импульсы сдвига с входа 7 подаются не только на дина ческие тактируемые входы С ячеек, и на входы запрещения Б переключен «о счетному входу Т, поэтому переключения триггеров при сдвиге инфо мации не оказывают воздействия на счетные входы Т.

Занесение параллельного цифрово го кода, поданного на вход 17, п изводится подачей импульса на вх 6. По фронту этого импульса инфор мация с щин 18-22 одновременно зан сится, в ячейки 1-5. Сброс регистра осуществляется по входу 6, причем во время действия импульса сброса не имеет значения, какие сигналы имеются на динамических входах С и Т ячеек.

Ячейка (фиг. 2) является одновр менно триггером со счетным входом Т и D-триггером с двумя парами вхо дов D и С, причем входы Т и С явля ются динамическими.

В исходном состоянии ячейки пам 35 ти триггер 23 находится в состояни О, на его выходах 41 и 42 имеютс сигналы соответственно О и 1, входах R 36, Т 35, В 34, С1 39 и С2 40 имеются сигналы О.

Ячейка памяти при подаче импуль сов на счетный вход Т 35 работает следующим образом.

Первьй поданный на вход Т импул коммутируется на первый выход (рас

20

25

30

импульс сдвига на входе 7 осуществля- 45 положен вверху) первого ключа 24,

ет одновременную перезапись сигналов из ячейки 1 в ячейку 2 и с входа 8 в ячейку 1. Аналогичным образом заносятся остальные разряды последовательного цифрового кода.

При занесении информации по входу 9 сдвиговый регистр работает как двоичный счетчик. Первый импульс, поданнъй на вход 9, переключает рчей- ку 1 в состояние 1. Второй поданный на вход 9 импульс переключает ячейку 1 в состояние О, на инверсном выходе ячейки 1 формируется фронт импульса, который переключает

5

40

ячейку 2 в состояние 1, Следующие подаваемые на вход 9 импульсы аналогичным образом переключают ячейки сдвигового регистра.

Сдвиг вправо занесенной в регистр информации производится подачей импульсов на вход 7 сдвига. При зтом происходит одновременный перенос информации из каждого i-ro разряда в (1-|-1)-й разряд. Импульсы сдвига с входа 7 подаются не только на динамические тактируемые входы С ячеек, но и на входы запрещения Б переключения «о счетному входу Т, поэтому переключения триггеров при сдвиге информации не оказывают воздействия на счетные входы Т.

Занесение параллельного цифрового кода, поданного на вход 17, производится подачей импульса на вход 6. По фронту этого импульса информация с щин 18-22 одновременно заносится, в ячейки 1-5. Сброс регистра осуществляется по входу 6, причем во время действия импульса сброса не имеет значения, какие сигналы имеются на динамических входах С и Т ячеек.

Ячейка (фиг. 2) является одновременно триггером со счетным входом Т и D-триггером с двумя парами входов D и С, причем входы Т и С являются динамическими.

В исходном состоянии ячейки памя- 35 ти триггер 23 находится в состоянии О, на его выходах 41 и 42 имеются сигналы соответственно О и 1, на входах R 36, Т 35, В 34, С1 39 и С2 40 имеются сигналы О.

Ячейка памяти при подаче импульсов на счетный вход Т 35 работает следующим образом.

Первьй поданный на вход Т импульс коммутируется на первый выход (рас0

25

30

поступает на вход триггера 23 и переключает его в состояние 1. На выходах 41 и 42 ячейки и, следовательно, на входах V, V ключа 24

происходит изменение сигнала управления со значений соответственно О и 1 на значения соответственно 1 и О, при этом коммутация первого импульса прекращается. Второй поданный на вход Т импульс коммутируется на второй выход (расположен внизу) ключа 24, поступает на вход R триггера 23 и переключает его в состояние О, при этом изменяются сигналы на входах V, V ключа 24, р результате чего коммутация второго импульса через ключ 24 прекращается. Таким образом,на выходах Knjo4a 24 импульсы действуют только в течение времени переключения триггера 23 и переходного процесса в ключе 24.

Подача сигнала 1 на любой вход В 34 приводит к запрео(ению коммутации импульсов через ключ 24, при этом подача импульсов на счетный вход Т не оказывает влияния на триггер 23, счетный вход Т фактически отключается.

Ячейка памяти при ее использовании в качестве D-триггера работает следующим образом.

Если на входе D2 38 имеется сигнал О, то поданный на вход С2 40 импульс коммутируется на первый выход ключа 26, поступает на вход R триггера 23 и сбрасывает его в сосется сигнал 1, то поданный на вход С2 40 импульс коммутируется на второй выход ключа 26, поступает на вход S триггера 16 и переключает его в состояние 1.

Если , а триггер 23 находится в состоянии 1, то подача импульса на вход С1 39 приводит к его коммутации на первый выход ключа 25 и на вход R триггера 23, в результате чего триггер 23 переключается в сое- тояние О. При этом коммутация импульса через ключ 25 прекращается.

Если , а триггер 23 находится в состоянии О, то на выходе элемен ;та ИЛИ-НЕ 28 формируется сигнап 1, в результате чего поданный на вход С1 39 импульс через ключ 25 вообще не коммутируется.

Формула изобретения

Универсальный сдвиговый регистр, содержащий в каждом разряде ячейку памяти, состоящую из RS-триггера, прямой выход которого является прямым выходом ячейки памяти, первые информационные входы ячеек памяти являются входами параллельной записи регистра, прямые выходы ячеек памяти каждого разряда соединены с вторыми информационными входами ячеек памяти последующего разряда и являются выходами регистра, второй информационный вход ячейки памяти

fO

f5

20

S

30 j

- 40

45

2954494

первого разряда является информационным входом регистра, первые тактовые входы ячеек памяти всех разрядов объединены, отличающий- 5 с я тем, что, с целью расширения области применения регистра за счет возможности счета импульсов, первые и вторые тактовые входы ячеек памяти всех разрядов соединены соответственно с первыми и вторыми входами запрещения переключения по счетному входу этих же ячеек и являются соответственно входами записи параллельного кода и входом сдвига регистра, входы сброса ячеек памяти всех разрядов объединены и являются входом сброса регистра, инверсный выход ячейки памяти каждого разряда соединен со счетным входом ячейки памяти последующего разряда, счетный вход ячейки памяти первого разряда является счетным входом регистра, причем каждая ячейка дополнительно содержит три и rayльcныx ключа, три элемента ИЛИ, два элемента ИЛИ- НЕ и два элемента И, первые входы которых соединены с первыми входами элементов ИЛИ-НЕ, с первым входом управления первого импульсного ключа и с прямым выходом RS-триггера инверсный выход которого является инверсным выходом ячейки памяти, вторые входы элементов И соединень с вторыми входами первого и второго, элементов ИЛИ-НЕ и входами управления второго и третьего импульсных ключей соответственно и являются первым и вторым информационными входами ячейки памяти соответственно, выходы первых элементов И и ИЛИ-НЕ соединены соответственно с первым и вторым входами второго элемента ИЛИ, а выходы вторых элементов И и ИЛИ-НЕ соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы элементов ИЛИ соединены с входами запреп(ения коммутации соответствующих импульсных ключей, первый выход первого импульсного ключа и вторые выходы второго и третьего импульсных ключей присоединены к входам S RS-триггера, а второй выход первого импульсного ключа и первые выходы второго и третьего импульсных ключей присоединены к входам R RS-триггера, инверсный выход которого соединен с вторым вводом управления первого импульсного ключа, тактовый вход кото50

55

рого является счетным входом ячейки памяти, первый и второй входы первого элемента ИЛИ являются входами запрещения переключения по счетному

Редактор И.Николайчук

Составитель С.Королев Техред А.Кравчук

Заказ 622/58Тираж 590Подписное

ВНРМПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.,...-.---- ------------ - --

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

входу ячейки памяти, третьи входы элементов ИЛИ соединены с входом R RS-триггера н являются входом сброса ячейки памяти.

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный сдвиговый регистр | 1986 |

|

SU1339657A1 |

| Устройство для выделения признаков изображения | 1987 |

|

SU1418774A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство обнаружения кодов групповой синхронизации | 1990 |

|

SU1812628A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

Изобретение относится к цифровой и 1шпульсной технике и может быть использовано в вычислительной технике, автоматике и микросхемотехнике . Цель изобретения - расширение области применения регистра. Поставленная цель достигается тем, что в каждый разряд регистра введены импульсные ключи 24-26 с соответствующими связями. Это позволяет использовать регистр не только для сдвига информации, но и для счета тактовых импульсов, 2 ил. 27 1 С в 2« 23 i «/ (Л t42 52 п Ж г±Ш 59 c 28 Ъ 25 DO рич.г

| СДВИГАЮЩИЙ РЕГИСТР | 1972 |

|

SU424234A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Климов В.В | |||

| Импульсные ключи в цифровых устройствах | |||

| - М.: Радио и связь, 1984 Справочник по интегральным микросхемам | |||

| /Под ред | |||

| Б.В.Тарабри- на | |||

| - М.: Энергия, 1980, с | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

Авторы

Даты

1987-03-07—Публикация

1985-06-21—Подача