113

Изобретение относится к ийпульс- ной технике, в частности к устройствам электронной коммутации, и может быть использовано для распределения импульсных сигналов в вычислительных системах с программируемой коммутацией .

Цель изобретения - увеличение надежности коммутатора за счет того, что исключается возможность отработки им ложного кода, возникающего в результате прохождения по входным и тактовой шинам импульсной помехи.

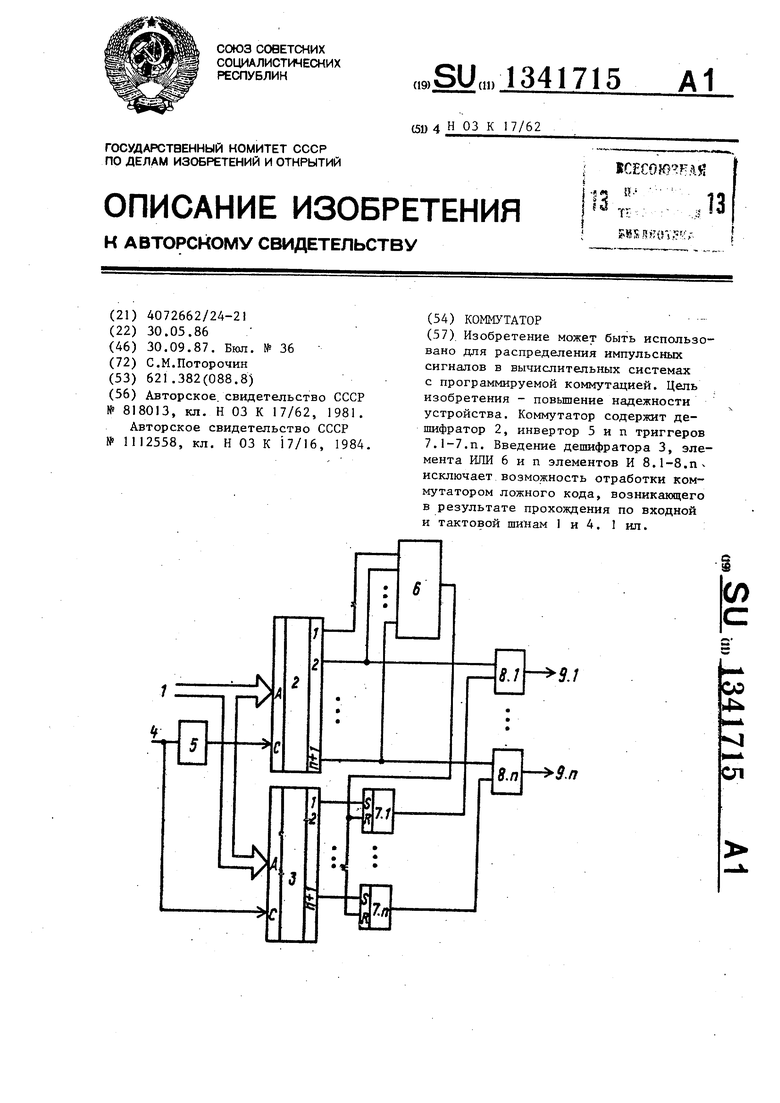

На чертеже представлена функцно- нальная схема коммутатора.

Коммутатор содержит входные шины 1, первый и второй дешифраторы 2 и 3 тактовую шину 4, инвертор 5, элемент ИЛИ 6, п триггеров 7.1-7.П, п элементов И 8.1-8,п, выходы 9,1-9.п.

Входные шины 1 коммутатора соединены с входами дешифраторов 2 и 3, Тактовая шина 4 подключена к входу .синхронизации второго дешифратора 3 и через инвер тор 5 - к входу синхронизации первого дешифратора 2, выходы которого соединены с входами элементов ИЛИ 6. Выходы второго дешифратора 3 соединены с S-входами соответ- ствующих триггеров 7.1-7.П, R-входы которых объединены и соединены с выходом элемента ИЛИ 6. Первые входы элементов И 8.1-8.п соединены с выходами первого дешифратора 2. Вторые входы элементов И 8.1-8.П соединены с выходами соответствующих триггеров 7.1-7.п. Выходы элементов И 8.1-8.П соединены.с выходными шинами 9.1-9.П коммутатора.

Коммутатор работает следующим образом.

Условием формирования сигнала на выходной шине 9,1-9.п коммутатора является совпадение номера триггера 7.1-7,п, установленного в единичное состояние во время присутствия активного сигнала на тактовой шине 4 ком- мутатора и соответственно разрешения работы второго дешифратора 3, с номе- ром выхода первого дешифратора 2, активизируемого после окончания действия сигнала на тактовой шине 4 коммутатора и соответственно разрешения работы второго дешифратора 3, с но- мером выхода первого дешифратора 2, активизируемого после окончания действия сигнала на тактовой шине 4 коммутатора и соответственно разрешения

152

работы второго дешифратора 3, с номером выхода первого дешифратора 2, активизируемого, после окончания действия сигнала на тактовой шине 4 коммутатора.

Длительность формируемого выходного сигнала равна суммарному времени отработки элементом ИЛИ 6 сигнала с выхода первого дешифратора 2 и триггером 7,1-7,п сигнала с выхода элемента ИЛИ 6, который устанавливает его в нулевое состояние (при управлении медленнодействующими механизмами на выходных шинах коммутатора необходимы удлинители импульсов),

При отсутствии помехи на входных шинах 1 коммутатора на управляющих входах первого и второго дешифраторов 2 и 3, как в момент сигнала на тактовой шине 4, так и после его снятия, присутствует один и тот же код. Номер триггера 7.1-7.П, установленного в единичное состояние, совпадает с номером выхода первого дешифратора 2, на котором присутствует сигнал. На выходной шине 9 коммутатора формируется импульс, длительность которого равна суммарному времени прохождения сигнала с выхода первого дешифратора 2 через элемент ИЛИ 6 и -установки сигналом с выхода элемента ИЛИ 6 триггера 7.1-7.П в нулевое состояние.

При возникновении импульсной помехи на входных шинах 1 и отсутствии сигнала на тактовой шине 4 разрешена работа первого дешифратора 2 и запрещена работа второго дешифратора 3, На одном из выходов первого дешифратора 2 появляется активный уровень. Триггеры 7.1...7.п обнулены в преды- дзпдем такте и низкими уровнями на своих выходах блокируют прохождение активного сигнала с любого из выходов пер-вого дешифратора 2 на выходные шины 9.1-9.П коммутатора. При возникновении импульсной помехи на тактовой шине 4, при отсутствии информации на входных шинах 1 коммутатора ни одна из выходных шин, как несоответствующая нулевому коду, не активизируется.

При возникновении импульсной помехи на тактовой 4 и входных 1 шинах коммутатора активизируется один из выходов второго дешифратора 3, номер которого -соответствует коду сигналов на входных шинах 1, возникших в ре313

зультате воздействия помехи. При этом один из триггеров 7,1-7.п, соединенный с выходом второго дешифратора 3, на котором присутствует сиг- нал, устанавливается в единичное состояние. Работа первого дешифратора 2 в это время запрещена. После окончания воздействия помехи запрещается работа второго дешифратора 3 и разре- шается работа первого дешифратора 2. Причем момент разрешения работы первого дешифратора 2 задержан относительно момента запрета работы второ-. го дешифратора 3 на величину времени задержки переключения инвертора 5, что способствует повьппению помехоустойчивости коммутатора.

После разрешения работы первого дешифратора 2 номер кода, поступающего на выходные шины 1 коммутатора, не совпадает с номером кода, формируемого на них в момент воздействия помехи, и как следствие, не совпадает номер активизируемого выхода первого дешифратора 2 с номером установившегося в единичное состояние одного из триггеров 7.1-7.п. .Код импульсной помехи коммутатором не отрабатывается .

Редактор И.Касарда Заказ 4444/56

Составитель А.Чаховский Техред М.Ходанич

Корректор

Тираж 90.1Подписное

ВНЙИПИ Государственного комитета СССР

по делан изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

I.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, ч

Формула изобретения

Коммутатор, содержащий входные, выходные и тактовую шины, инвертор, п триггеров и первый дешифратор, о т- личающийся тем, что, с целью увеличения надежности, введены второй дешифратор, элементы И, элемент ИЛИ, входы которого подключены к выходам первого дешифратора, а выход соединен с R-входаЬш триггеров, S-входы которых соединены с соответствующими, начиная с второго по п+1, выходами второго дешифратора, первые входы элементов И соединены с соответствующими, начиная с второго по n-fl, выходами первого дешифратора, вторые входы элементов И сйединены с выходами соответствующих, триггеров, а выходы элементов И соединены с соответствующими выходными шинами ком- , мутатора, входные шины которого соединены с входами первого и второго дешифраторов, тактовая шина -коммутатора, соединена с входом синхронизации второго дешифратора и с входом инвертора, выход которого соединен с входом синхронизации первого дешифратора.

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1981 |

|

SU1001470A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Фазовый синхронизатор | 1990 |

|

SU1739491A1 |

| Модуль многоканального коммутатора | 1986 |

|

SU1368971A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство контроля импульсных последовательностей | 1990 |

|

SU1795539A1 |

| Селектор импульсов заданной кодовой комбинации | 1987 |

|

SU1457169A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1688259A1 |

| Анализатор иинтенсивности импульсных помех | 1986 |

|

SU1406498A1 |

. Изобретение может быть использовано для распределения импульсных сигналов в вычислительных системах с программируемой коммутацией. Цель изобретения - повышение надежности устройства. Коммутатор содержит дешифратор 2, инвертор 5 и п триггеров 7.1-7.п. Введение дешифратора 3, элемента ИЛИ 6 и п элементов И 8.1-8.п исключает возможность отработки коммутатором ложного кода, возникающего в результате прохождения по входной и тактовой шинам 1 и 4. 1 ил. З.п со Nt vj ел

| Авторское, свидетельство СССР № 818013, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Коммутатор с обнаружением ошибок | 1983 |

|

SU1112558A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-30—Публикация

1986-05-30—Подача