4, второй 5 и третий 6 регистры нижней границы участка программы, первый 7, второй 8 и третий 9 регистры верхней границы участка программы, дешр ратор 10, шифратор 11, сумматор 12, счетчик циклов 13, первую 14 и вторую 15 схемы сравнения, первый 16 и второй 17 демультиплексоры, мультиплексор 18, первьй 19, второй 22, третий 20, четвертый 21 , пятьш

1

Изобретение относится к вычислительной технике и может быть использовано для организации контроля и отладки програ;мм.

Целью изобретения является расши- рение области применения.

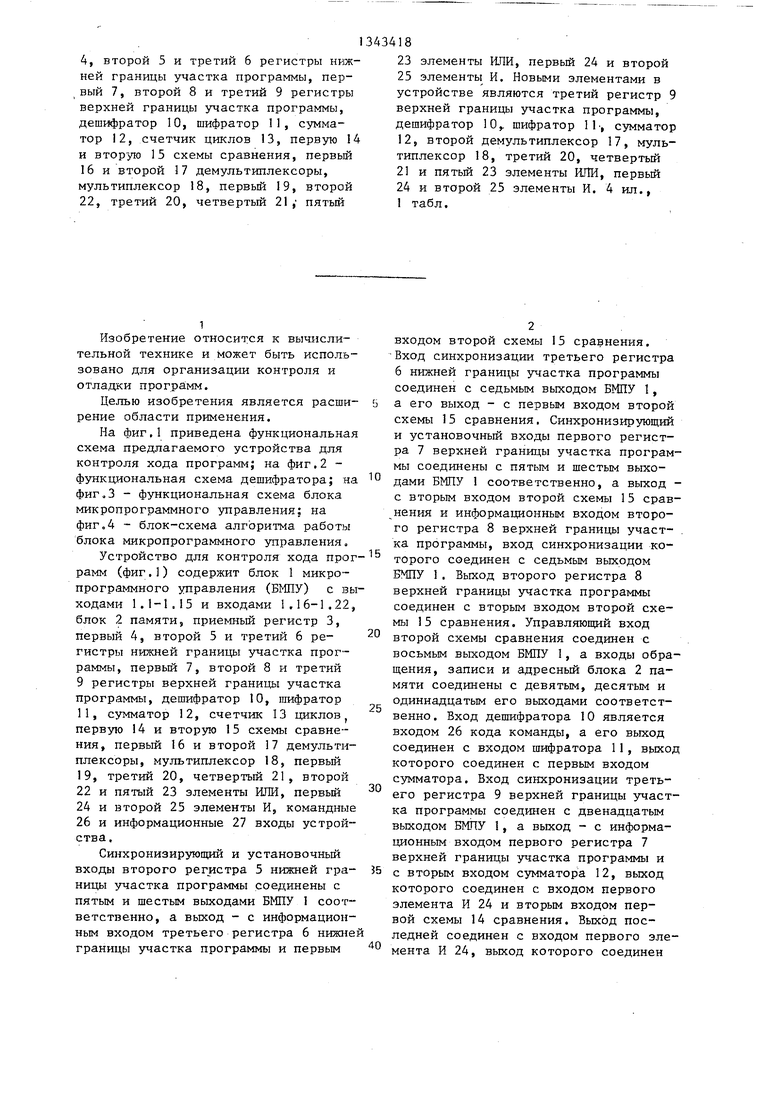

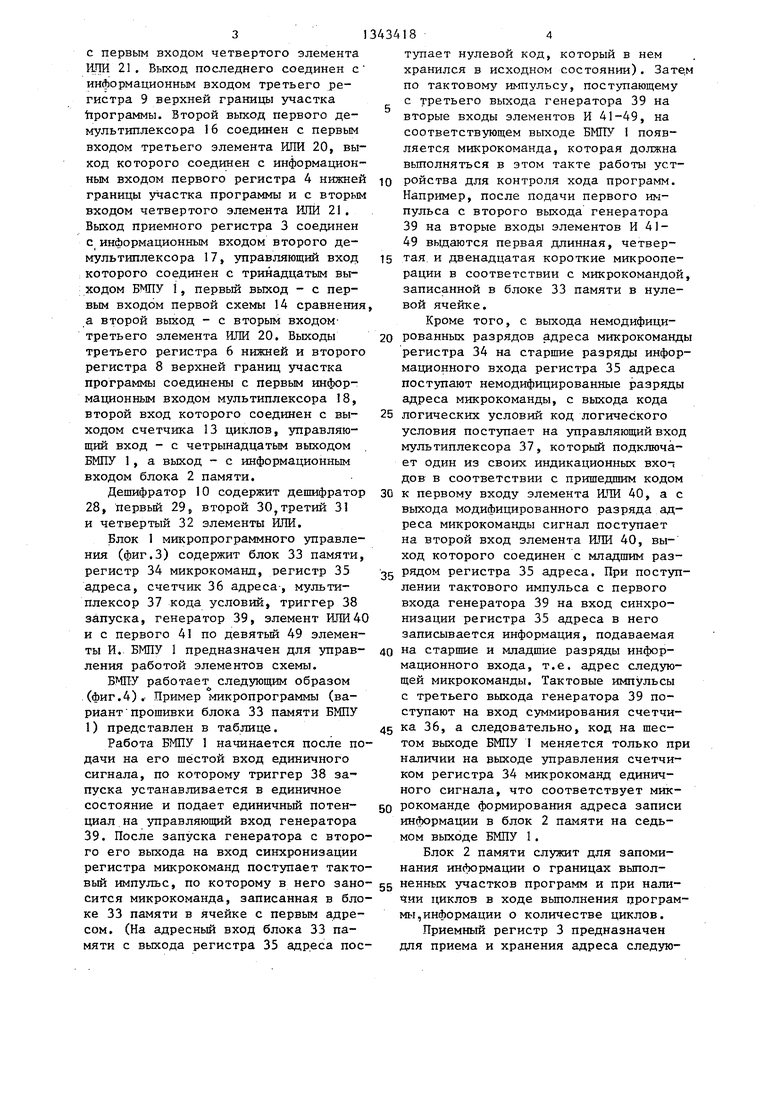

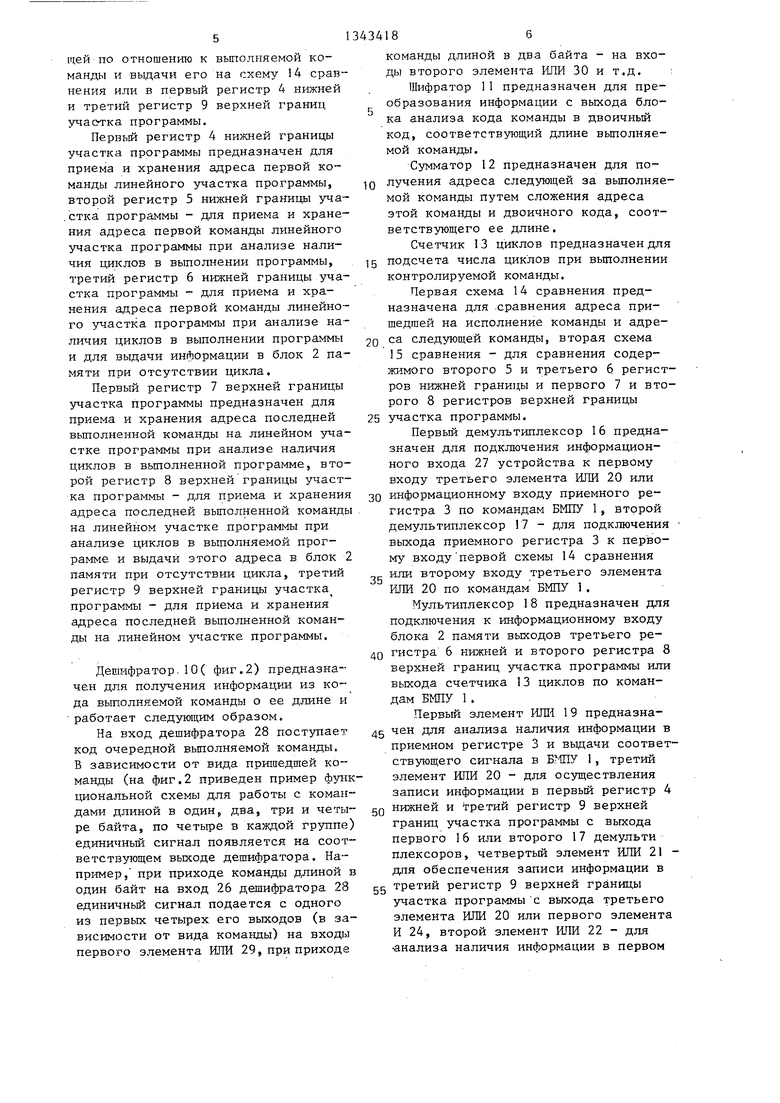

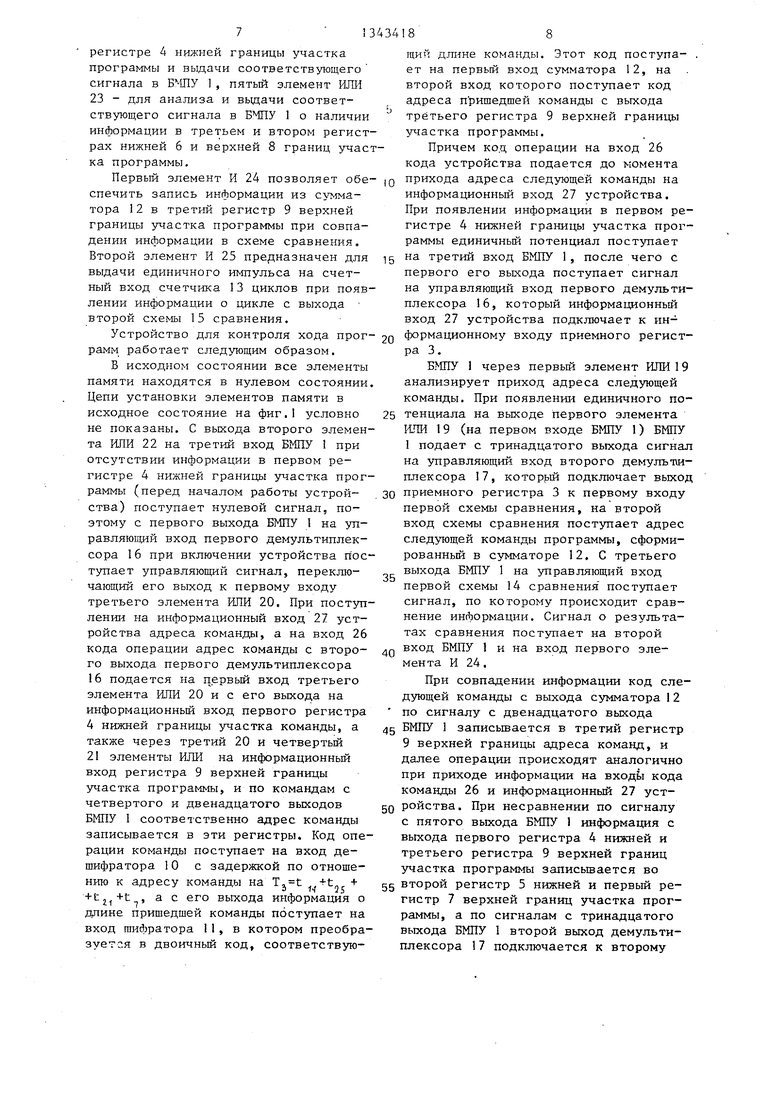

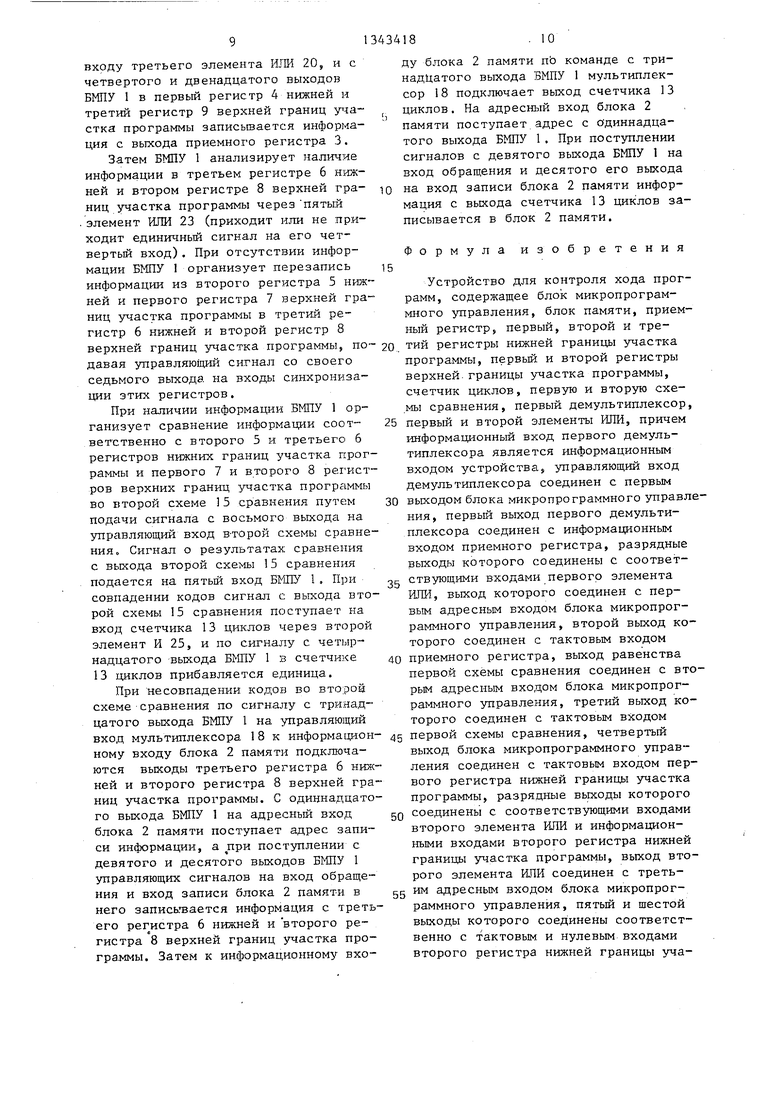

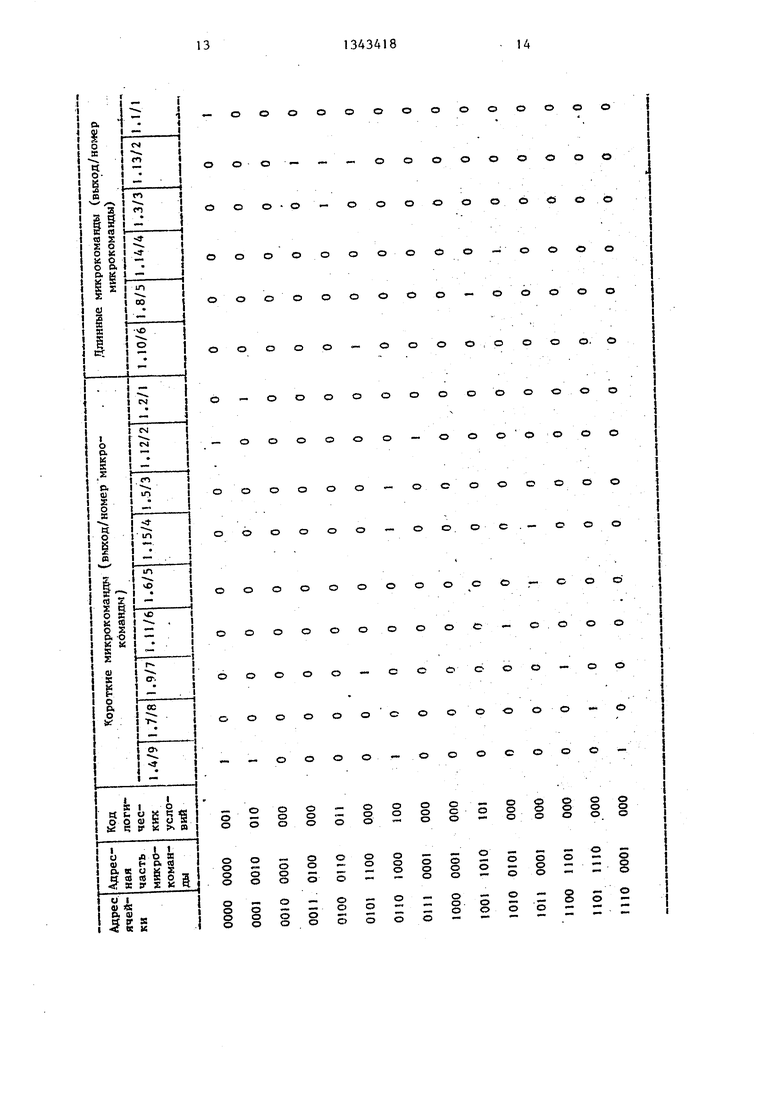

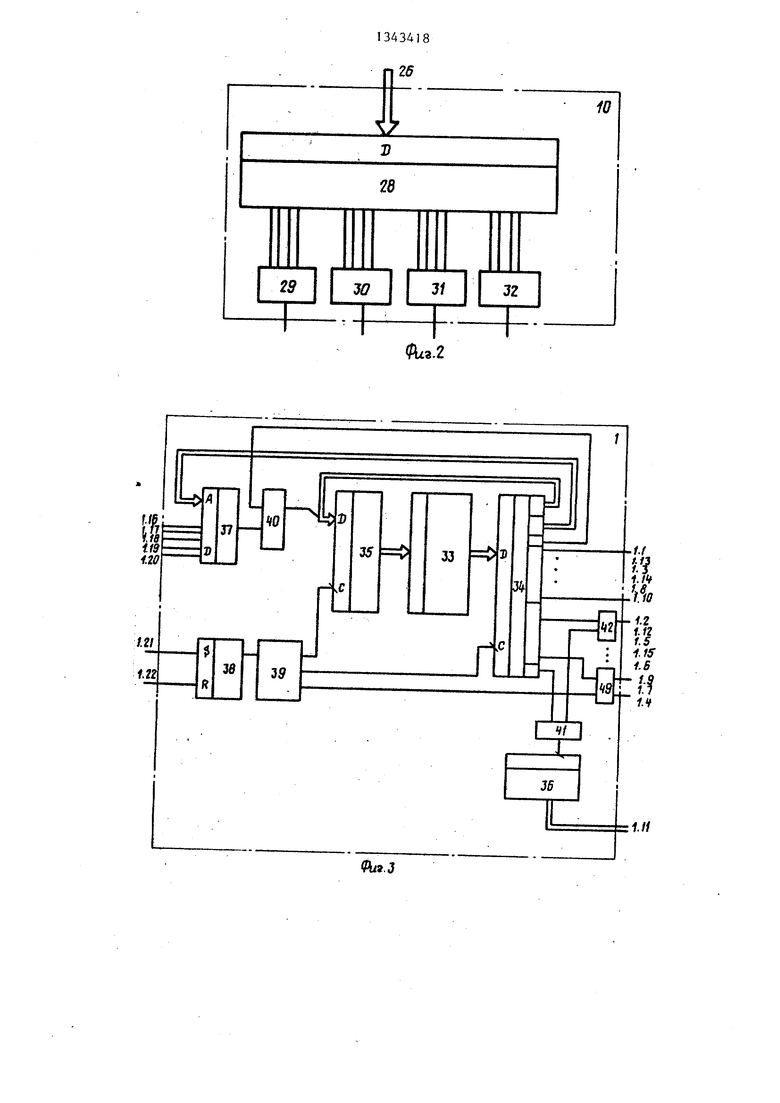

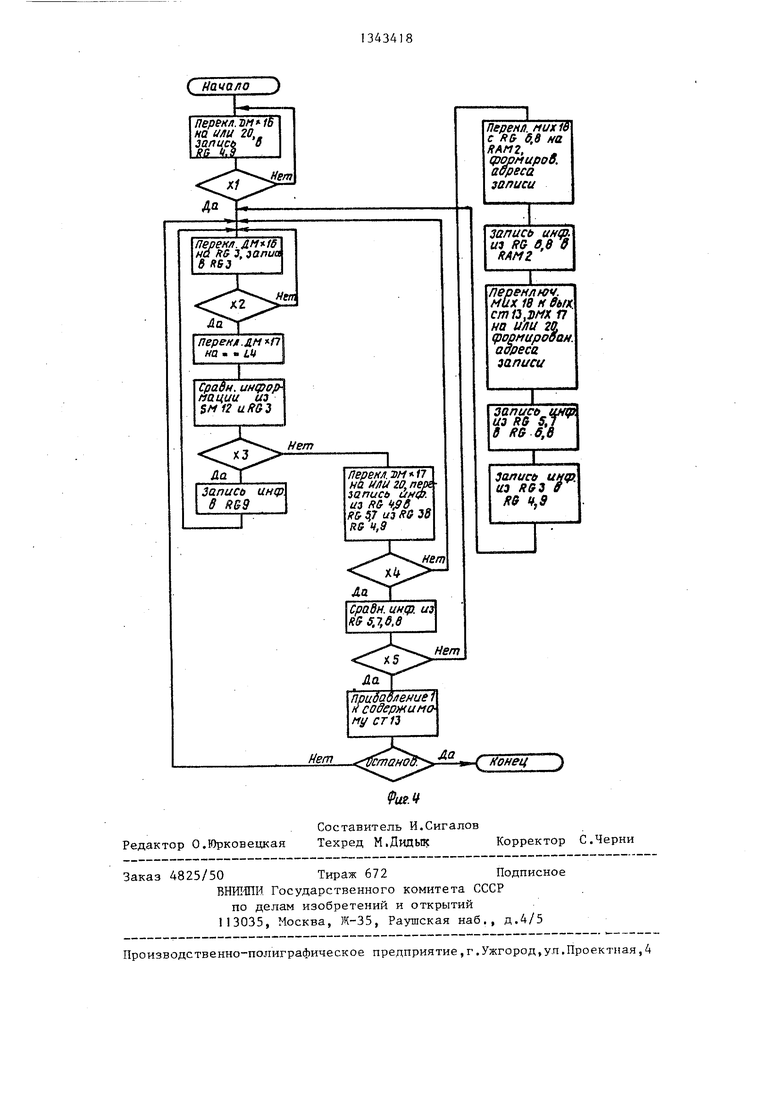

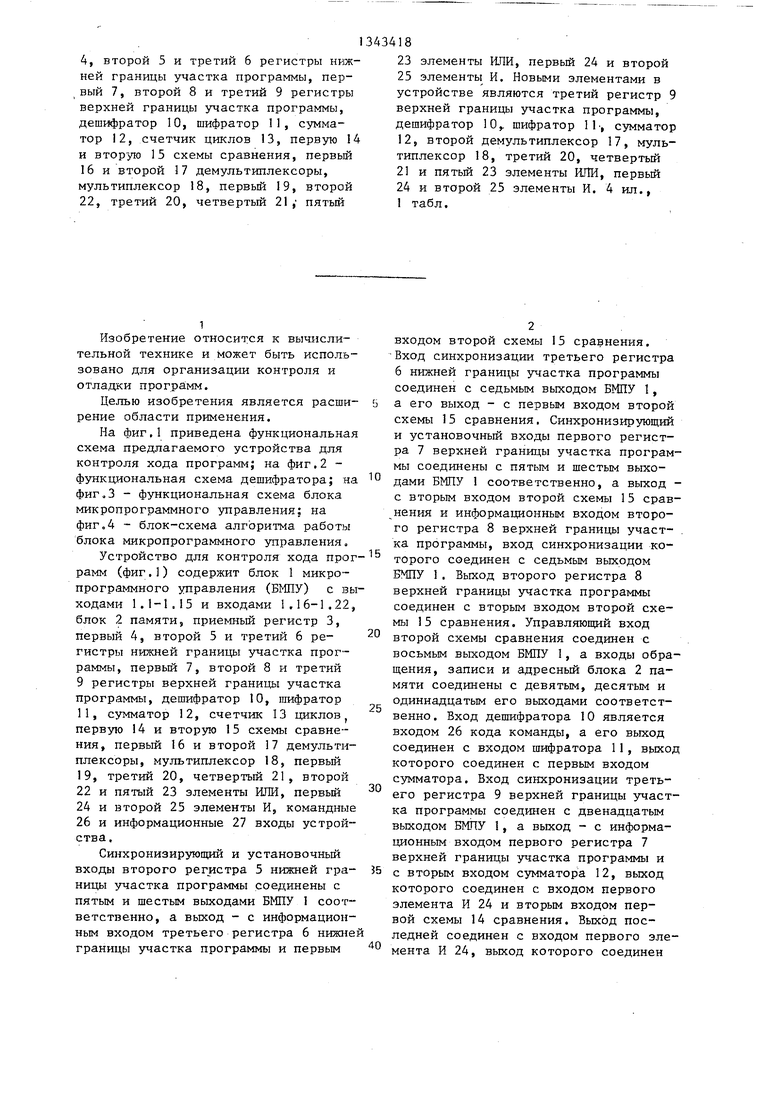

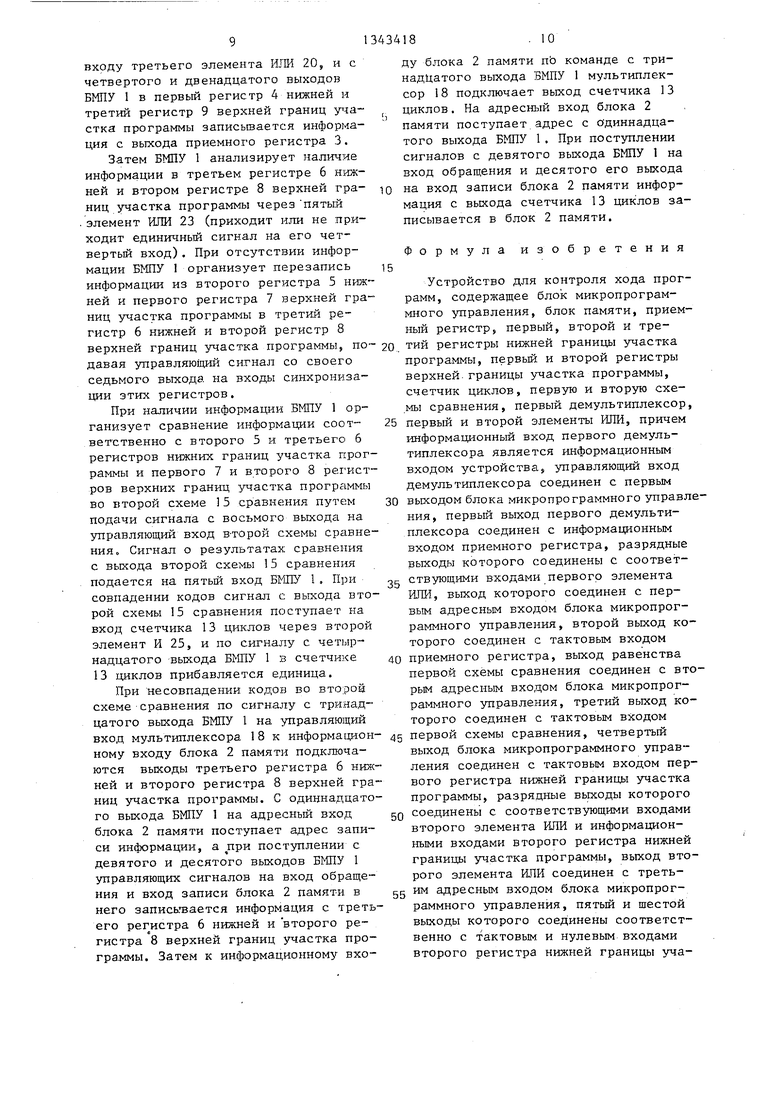

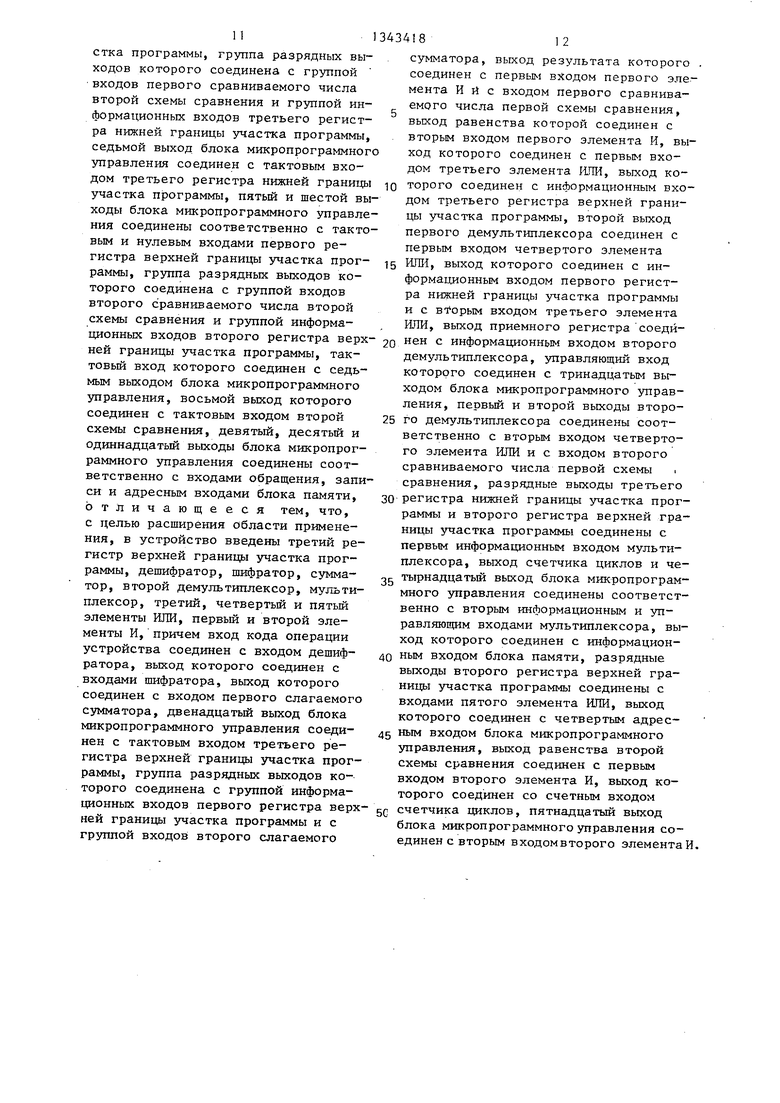

На фиг,1 приведена функциональная схема предлагаемого устройства для контроля хода программ; на фиг.2 - функциональная схема дешифратора; на фиг«3 - функциональная схема блока микропрограммного управления: на фиг.4 - блок-схема алгоритма работы блока микропрограммного управления.

Устройство для контроля хода прог рамм (фиг.1) содержит блок 1 микропрограммного управления (БМПУ) с выходами 1.1-1.15 и входами 1.16-1.22, блок 2 памяти, приемньш регистр 3, первый 4, второй 5 и третий 6 ре- гистры нижней границы участка программы, первьй 7, второй 8 и третий 9 регистры верхней границы участка программы, дешифратор 10, шифратор 11, сумматор 12, счетчик 13 циклов первую 14 и вторую 15 схемы сравнения, первый 16 и второй 17 демультиплексоры, мультиплексор 18, первый 19, третий 20, четвертый 21, второй 22 и пятый 23 элементы ИЛИ, первый 24 и второй 25 элементы И, командные 26 и информационные 27 входы устройства.

Синхронизирующий и установочньш входы второго регистра 5 нижней гра- ницы участка программы соединены с пятым и шестым выходами ВМПУ 1 соответственно, а выход - с информационным входом третьего регистра 6 нижне

границы участка программы и первым

43418

23элементы ИЛИ, первый 24 и второй 25 элементы И, Новыми элементами в устройстве являются третий регистр 9 верхней границы участка программы, дешифратор 10,. шифратор , сумматор 12, второй демультиплексор 17, мультиплексор 18, третий 20, четвертый 21 и пятьш 23 элементы ИЛИ, первый

24и второй 25 элементы И, 4 ил., 1 табл.

входом второй схемы 15 сравнения. Вход синхронизации третьего регистра 6 нижней границы участка программы соединен с седьмым выходом БМПУ 1, а его выход - с первым входом второй схемы 15 сравнения, Синхронизирующий и установочный входы первого регистра 7 верхней границы участка программы соединены с пятым и шестым выходами БМПУ 1 соответственно, а выход - с вторым входом второй схемы 15 сравнения и информационным входом второго регистра 8 верхней границы участ- . ка программы, вход синхронизации которого соединен с седьмым вьтодом БМПУ 1. Выход второго регистра 8 верхней границы участка программы соединен с вторым входом второй схемы 15 сравнения. Управляющий вход второй схемы сравнения соединен с восьмым выходом БМПУ I, а входы обращения, записи и адресный блока 2 памяти соединены с девятым, десятым и одиннадцатым его выходами соответственно . Вход дешифратора 10 является входом 26 кода команды, а его выход соединен с входом шифратора 11, вькод которого соединен с первым входом сумматора. Вход синхронизации третьего регистра 9 верхней границы участка программы соединен с двенадцатым выходом БМПУ , а выход - с информа ционным входом первого регистра 7 верхней границы участка программы и с вторьм входом сумматора 12, выход которого соединен с входом первого элемента И 24 и вторым входом первой схемы 14 сравнения. Выход последней соединен с входом первого элемента И 24, выход которого соединен

с первым входом четвертого элемента ИЛИ 21. Выход последнего соединен с информационным входом третьего регистра 9 верхней границы участка программы. Второй выход первого де- мультиплексора 16 соединен с первым входом третьего элемента ИЛИ 20, выход которого соединен с информационным входом первого регистра 4 нижней границы участка программы и с вторым входом четвертого элемента ИЛИ 21. Выход приемного регистра 3 соединен с информационным входом второго де- мультиплексора 17, управляющий вход которого соединен с тринадцатым выходом БМПУ i, первый выход - с первым входом первой схемы 14 сравнения а второй выход - с вторым входом- третьего элемента ИЛИ 20, Выходы третьего регистра 6 нижней и второго регистра 8 верхней границ участка программы соединены с первым информационным входом мультиплексора 18, второй вход которого соединен с выходом счетчика 13 циклов, управляющий вход - с четрынадцатым выходом БМПУ 1, а выход - с информационным входом блока 2 памяти.

Дешифратор 10 содержит дешифратор 28, первьй 299 второй 30,третий 31 и четвертый 32 элементы ИЛИ.

Блок 1 микропрограммного управления (фиг.З) содержит блок 33 памяти, регистр 34 микрокоманд, регистр 35 адреса, счетчик 36 адреса-, мультиплексор 37 кода условий, триггер 38 запуска, генератор 39, элемент ШШ40 и с первого 41 по девятьш 49 элементы И. БМПУ 1 предназначен для управления работой элементов схемы.

БМП-У работает следующим образом (фиг.4) . Пример микропрограммы (вариант прошивки блока 33 памяти БМПУ 1) представлен в таблице.

Работа БМПУ 1 начинается после подачи на его шестой вход единичного сигнала, по которому триггер 38 запуска устанавливается в единичное состояние и подает единичный потенциал на управляющий вход генератора 39. После запуска генератора с второго его выхода на вход синхронизации регистра микрокоманд поступает тактовый импульс, по которому в него зано- gg ненных участков программ и при нали- сится микрокоманда, записанная в бло- циклов в ходе выполнения црограм- ке 33 памяти в ячейке с первым адре- мы,информации о количестве циклов, сом. (На адресный вход блока 33 па- Приемный регистр 3 предназначен мяти с выхода регистра 35 адреса пос- для приема и хранения адреса следую

434184

тупает нулевой код, который в нем хранился в исходном состоянии) . Зате.м по тактовому импульсу, поступающему с третьего выхода генератора 39 на вторые входы элементов И 41-49, на соответствующем выходе БМПУ 1 появляется микрокоманда, которая должна выполняться в этом такте работы уст10 ройства для контроля хода программ. Например, после подачи первого импульса с второго выхода генератора 39 на вторые входы элементов И 41- 49 выдаются первая длинная, четвер15 тая и двенадцатая короткие микрооперации в соответствии с микрокомандой, записанной в блоке 33 памяти в нулевой ячейке.

Кроме того, с выхода немодифици20 рованных разрядов адреса микрокоманды регистра 34 на старшие разряды информационного входа регистра 35 адреса поступают немодифицированные разряды

адреса микрокоманды, с выхода кода

25 логических условий код логического условия поступает на управляющий вход мультиплексора 37, который подключает один из своих индикационных вхо-т дов в соответствии с пришедшим кодом

30 к первому входу элемента ИЛИ 40, а с выхода модифицированного разряда адреса микрокоманды сигнал поступает на второй вход элемента ИЛИ 40, выход которого соединен с младшим раз35 рядом регистра 35 адреса. При поступлении тактового импульса с первого входа генератора 39 на вход синхронизации регистра 35 адреса в него записывается информация, подаваемая

40 на старшие и младшие разряды информационного входа, т.е. адрес следующей микрокоманды. Тактовые импульсы с третьего выхода генератора 39 поступают на вход суммирования счетчи-

45 ка 36, а следовательно, код на шестом выходе БМПУ 1 меняется только пр наличии на выходе управления счетчиком регистра 34 микрокоманд единичного сигнала, что соответствует мик50 рокоманде формирования адреса записи информации в блок 2 памяти на седьмом выходе БМПУ 1.

Блок 2 памяти служит для запоминания информации о границах выполщей по отношению к выполняемой команды н вьщачи его на схему 14 сравнения или в первый регистр 4 нижней и третий регистр 9 верхней границ учаотка программы.

Первый регистр 4 нижней границы участка программы предназначен для приема и хранения адреса первой команды линейного участка программы, второй регистр 5 нижней границы уча- .стка программы - для приема и хране ния адреса первой команды линейного участка программы при анализе наличия циклов в выполнении программы, третий регистр 6 нижней границы участка программы - для приема и хранения адреса первой команды линейного участка программы при анализе наличия циклов в выполнении программы и для выдачи информации в блок 2 памяти при отсутствии цикла.

Первый регистр 7 верхней границы участка программы предназначен для приема и хранения адреса последней Бьшолненной команды на линейном участке программы при анализе наличия циклов в выполненной программе, второй регистр 8 верхней границы участка программы - для приема и хранения адреса последней выполненной команды на линейном участке программы при анализе циклов в выполняемой программе и выдачи этого адреса в блок 2 памяти при отсутствии цикла, третий регистр 9 верхней границы участка программы - для приема и хранения адреса последней выполненной команды на линейном участке программы.

Деишфратор.10( фиг.2) предназначен для получения информации из кода выполняемой команды о ее длине и работает следующим образом.

На вход дешифратора 28 поступает код очередной выполняемой команды. В зависимости от вида пришедшей команды (на фиг.2 приведен пример функ гщональной схемы для работы с командами длиной в один5 два, три и четыре байта, по четыре в каждой группе) единичньш сигнал появляется на соответствующем выходе дешифратора. Например, при приходе команды длиной в один байт на вход 26 дешифратора 23 единичный сигнал подается с одного из первых четырех его выходов (в зависимости от вида команды) на входы первого элемента ИЛИ 29, при приходе

команды длиной в два байта - на входы второго элемента ИЛИ 30 и т.д. ; Шифратор 11 предназначен для преобразования информации с выхода блока анализа кода команды в двоичный код, соответствующий длине вьтолняе- мой команды.

Сумматор 12 предназначен для получения адреса следующей за выполняемой команды путем сложения адреса этой команды и двоичного кода, соответствующего ее длине.

Счетчик 13 циклов предназначен для

подсчета числа циклов при вьтолнении контролируемой команды.

Первая схема 14 сравнения предназначена для .сравнения адреса пришедшей на исполнение команды и адреса следующей команды, вторая схема I5 сравнения - для сравнения содержимого второго 5 и третьего 6 регистров нижней границы и первого 7 и второго 8 регистров верхней границы

участка программы.

Первый демультиплексор 16 предназначен для подключения информационного входа 27 устройства к первому входу третьего элемента ИЛИ 20 или

информационному входу приемного регистра 3 по командам БМПУ 1, второй демультиплексор 17 - для подключения выхода приемного регистра 3 к первому входу первой схемы 14 сравнения

или второму входу третьего элемента ИЛИ 20 по командам БМПУ 1.

Мультиплексор 18 предназначен для подключения к информационному входу блока 2 памяти выходов третьего регистра 6 нижней и второго регистра 8 верхней границ участка программы или выхода счетчика 13 циклов по командам БМПУ 1.

Первый элемент ИЛИ 19 предназначен для анализа наличия информации в приемном регистре 3 и вьщачи соответствующего сигнала в 1, третий элемент ИЛИ 20 - для осуществления записи информации в первый регистр 4

нижней и третий регистр 9 верхней границ участка программы с выхода первого 16 или второго 17 демульти плексоров, четвертый элемент ИЛИ 21 - дня обеспечения записи информации в

третий регистр 9 верхней границы участка программы с выхода третьего элемента ИЛИ 20 или первого элемента И 24, второй элемент ИЛИ 22 - для анализа наличия информации в первом

7 13

регистре 4 нижней границы участка программы и выдачи соответствующего сигнала в Б -ШУ 1 , пятый элемент ИЛИ 23 - для анализа и выдачи соответствующего сигнала в БМПУ 1 о наличии информации в третьем и втором регистрах нижней 6 и верхней 8 границ участка программы.

Первый элемент И 24 позволяет обе- спечить запись информации из сумматора 12 в третий регистр 9 верхней границы участка программы при совпадении информации в схеме сравнения. Второй элемент И 25 предназначен для выдачи единичного импульса на счетный вход счетчика 13 циклов при появлении информации о цикле с выхода второй схемы 15 сравнения.

Устройство для контроля хода прог- рамм работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии. Цепи установки элементов памяти в исходное состояние на фиг.1 условно не показаны. С выхода второго элемента ЙШИ 22 на третий вход БМПУ 1 при отсутствии информации в первом регистре 4 нижней границы участка программы (перед началом работы устрой- ства) поступает нулевой сигнал, поэтому с первого выхода БМПУ 1 на управляющий вход первого демультиплек- сора 16 при включении устройства rioc тупает управляющий сигнал, переклю- чающий его выход к первому входу третьего элемента ИЛИ 20. При поступлении на информационный вход 27 устройства адреса команды, а на вход 26 кода операции адрес команды с второ- го выхода первого демультиплексора 16 подается на ц.ервый вход третьего элемента ИЛИ 20 и с его выхода на информационный вход первого регистра 4 нижней границы участка команды, а также через третий 20 и четвертьш 21 элементы ИЛИ на информационный вход регистра 9 верхней границы участка программы, и по командам с четвертого и двенадцатого выходов БМПУ 1 соответственно адрес команды записывается в эти регистры. Код операции команды поступает на вход дешифратора 10 с задержкой по отноше

нию к адресу команды на , +

, а с его выхода информация о длине пришедшей команды поступает на вход шифратора 11, в котором преобразуется в двоичный код, соответствующий длине команды. Этот код поступа- ет на первый вход сумматора 12, на второй вход которого поступает код адреса п ришедшей команды с выхода третьего регистра 9 верхней границы участка программы.

Причем код операции на вход 26 кода устройства подается до момента прихода адреса следующей команды на информационный вход 27 устройства. При появлении информации в первом регистре 4 нижней границы участка программы единичный потенциал поступает на третий вход БМПУ 1, после чего с первого его выхода поступает сигнал на управляющий вход первого демультиплексора 16, который информационный вход 27 устройства подключает к информационному входу приемного регистра 3.

БМПУ 1 через первый элемент ИЛИ 19 анализирует приход адреса следующей команды. При появлении единичного потенциала на выходе первого элемента ИЛИ 19 (на первом входе БМПУ 1) БМПУ 1 подает с тринадцатого выхода сигнал на управляющий вход второго демультш- плексора 17, которой подключает выход приемного регистра 3 к первому входу первой схемы сравнения, на второй вход схемы сравнения поступает адрес следующей команды программы, сформированный в сумматоре 12. С третьего выхода БМПУ 1 на управляющий вход первой схемы 14 сравнения поступает сигнал, по которому происходит сравнение информации. Сигнал о результатах сравнения поступает на второй вход БМПУ 1 и на вход первого элемента И 24.

При совпадении информации код следующей команды с выхода сумматора 12 по сигналу с двенадцатого выхода БМПУ 1 записьшается в третий регистр 9 верхней границы адреса команд, и далее операции происходят аналогично при приходе информации на входЬ кода команды 26 и информационный 27 устройства . При несравнении по сигналу с пятого выхода БМПУ 1 информация с выхода первого регистра 4 нижней и третьего регистра 9 верхней границ участка программы записьшается во второй регистр 5 нижней и первый регистр 7 верхней границ участка программы, а по сигналам с тринадцатого выхода БМПУ 1 второй выход демультиплексора 17 подключается к второму

входу третьего элемента ИЛИ 20, и с четвертого и двенадцатого выходов БМПУ 1 в первый регистр 4 нижней и третий регистр 9 верхней границ участка программы записьшается информация с выхода приемного регистра 3.

Затем БМПУ 1 анализирует наличие информации в третьем регистре 6 нижней и втором регистре 8 верхней границ участка программы через пятый .элемент ИЛИ 23 (приходит или не приходит единичный сигнал на его чет- вертьш вход). При отсутствии информации БМПУ 1 организует перезапись информации из второго регистра 5 нижней и первого регистра 7 верхней границ участка программы в третий регистр 6 нижней и второй регистр 8 верхней границ участка программы, подавая управляющий сигнал со своего седьмого выхода на входы синхронизации этих регистров.

При наличии информации БМПУ 1 организует сравнение информации соответственно с второго 5 и третьего 6 регистров нижних границ участка программы и первого 7 и второго 8 рех ист- ров верхних границ участка программы во второй схеме 15 сравнения путем подачи сигнала с восьмого выхода на управляющий вход в-торой схемы сравнения« Сигнал о результатах сравнения с вькода второй схемы 15 сравнения подается на пятьш вход БМПУ 1, При совпадении кодов сигнал с выхода второй схемы 15 сравнения поступает на вход счетчика 13 циклов через второй элемент И 25, и по сигналу с четырнадцатого выхода 1 в счетчике 13 циклов прибавляется единица.

При несовпадении кодов во второй схеме сравнения по сигналу с тринадцатого выхода БМПУ 1 на управляющий вход мультиплексора 18 к информационному входу блока 2 памяти подключаются выходы третьего регистра 6 ней и второго регистра 8 верхней границ участка программы. С одиннадцатого выхода БМПУ 1 на адресный вход блока 2 памяти поступает адрес записи информации, а при поступлении с девятого и десятого выходов БМПУ 1 управляющих сигналов на вход обращения и вход записи блока 2 памяти в него запись вается информация с третьего рег истра 6 нижней и второго регистра 8 верхней границ участка программы. Затем к информационному входу блока 2 памяти п о команде с тринадцатого выхода БМПУ 1 мультиплексор 18 подключает выход счетчика 13

циклов. На адресный вход блока 2 памяти поступает адрес с одиннадцатого выхода БМПУ 1. При поступлении сигналов с девятого выхода БМПУ 1 на вход обращ,ения и десятого его выхода

на вход записи блока 2 памяти информация с выхода счетчика 13 циклов записывается в блок 2 памяти.

Формула изобретения

Устройство для контроля хода программ, содержащее блок микропрограммного управления, блок памяти, приемный регистр, первый, второй и третий регистры нижней границы участка программы, первьй и второй регистры верхней границы участка программы, счетчик циклов, первую и вторую схе- .мы сравнения, первый демультиплексор,

первый и второй элементы ИПИ, причем информационный вход первого демуль- типлексора является информационным входом устройства$ управляющий вход демультиплексора соединен с первым

выходом блока микропрограммного управления, первый выход первого демультиплексора соединен с информационным входом приемного регистра, разрядные выходы которого соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым адресным входом блока микропрограммного управления, второй выход которого соединен с тактовым входом

приемного регистра, выход равенства первой схемы сравнения соединен с вторым адресным входом блока микропрограммного управления, третий выход которого соединен с тактовым входом

первой схемы сравнения, четвертый выход блока микропрограммного управления соединен с тактовым входом первого регистра нижней границы участка программы, разрядные выходы которого

соединены с соответствующими входами второго элемента ИЛИ и информационными входами второго регистра нижней границы участка программы, выход второго элемента ИЛИ соединен с третьим адресным входом блока микропрограммного управления, пятый и шестой выходы которого соединены соответственно с тактовым: и нулевым входами второго регистра нижней границы участка программы, группа разрядных выходов которого соединена с группой входов первого сравниваемого числа второй схемы сравнения и группой информационных входов третьего регистра нижней границы участка программы, седьмой выход блока микропрограммног управления соединен с тактовым входом третьего регистра нижней границы участка П1рограммы, пятый и шестой выходы блока микропрограммного управления соединены соответственно с тактовым и нулевым входами первого регистра верхней границы участка программы, группа разрядных выходов которого соединена с группой входов второго сравниваемого числа второй схемы сравнения и группой информационных входов второго регистра верхней границы участка программы, так- товьй вход которого соединен с седьмым выходом блока микропрограммного управления, восьмой выход которого соединен с тактовым входом второй схемы сравнения, девятый, десятый и одиннадцатый выходы блока микропрограммного управления соединены соответственно с входами обращения, записи и адресным входами блока памяти, отличающееся тем, что, с целью расширения области применения, в устройство введены третий регистр верхней гранищ 1 участка программы, дешифратор, шифратор, сумматор, второй демультиплексор, мультиплексор, третий, четвертый и пятьш элементы ИЛИ, первый и второй элементы И, причем вход кода операции устройства соединен с входом дешифратора, выход которого соединен с входами шифратора, выход которого соединен с входом первого слагаемого сумматора, двенадцатый выход блока микропрограммного управления соединен с тактовьм входом третьего регистра верхней границы участка программы, группа разрядных выходов которого соединена с группой информационных входов первого регистра верхней границы участка программы и с группой входов второго слагаемого

сумматора, выход результата которого . соединен с первым входом первого элемента И и с входом первого сравниваемого числа первой схемы сравнения, выход равенства которой соединен с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента I-LTPI, выход которого соединен с информационным входом третьего регистра верхней границы участка программы, второй выход первого демультиплексора соединен с первым входом четвертого элемента

ИЛИ, выход которого соединен с информационным входом первого регистра нижней границы участка программы и с вт орым входом третьего элемента ИЛИ, выход приемного регистра соедйнен с информационнь1М входом второго демультиплексора, управляющий вход которого соединен с тринадцатым выходом блока микропрограммного управления, первый и второй выходы второго демультиплексора соединены соответственно с вторым входом четвертого элемента ИЛИ и с входом второго сравниваемого числа первой схемы i сравнения, разрядные выходы третьего

регистра нижней границы участка программы и второго регистра верхней границы участка программы соединены с первым информационным входом мультиплексора, выход счетчика циклов и четырнадцатый выход блока микропрограммного управления соединены соответственно с вторым информационным и управляющим входами мультиплексора, выход которого соединен с информационным входом блока памяти, разрядные выходы второго регистра верхней границы участка программы соединены с входами пятого элемента ИЛИ, выход которого соединен с четвертым адресным входом блока микропрограммного управления, выход равенства второй схемы сравнения соединен с первым входом второго элемента И, выход которого соединен со счетным входом

счетчика циклов, пятнадцатый выход блока микропрограммного управления соединен с вторым входомвторого элементаИ.

С Hava/to 3

BSSL- t : g g2r..«i,. J

Пкренп. них 1в

с Kir б,в на

ПАП2.

(рормироо,

аареса

записи

записи uMqt из R5 5,Т б RG 6,6

Залип UHqy. из ЯУЗ 8 Я 6 tf,S

ияМ

Составитель И.Сигалов Редактор О.Юрковецкая Техред М.ДИДЬП

Заказ 4825/50Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Мультимикропрограммное устройство для контроля и управления | 1984 |

|

SU1249513A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

Изобретение относится к области вычислительной техники и может быть использовано для организации контроля и отладки программ. Цель изобретения - расширение области применения устройства. Устройство для контроля хода программ содержит блок 1 микропрограммного управления, блок 2 памяти, приемный регистр 3, первый (Л ОО N со 4 СХ)

| Патент США № 3931611, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода программ | 1980 |

|

SU1057949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-07—Публикация

1986-04-03—Подача