10

20

1 1345341 Изобретение относится к импульсой технике и может быть использовано измерительных и вычислительных стройствах.

Целью изобретения является повыение достоверности функционирования ересчетного устройства.

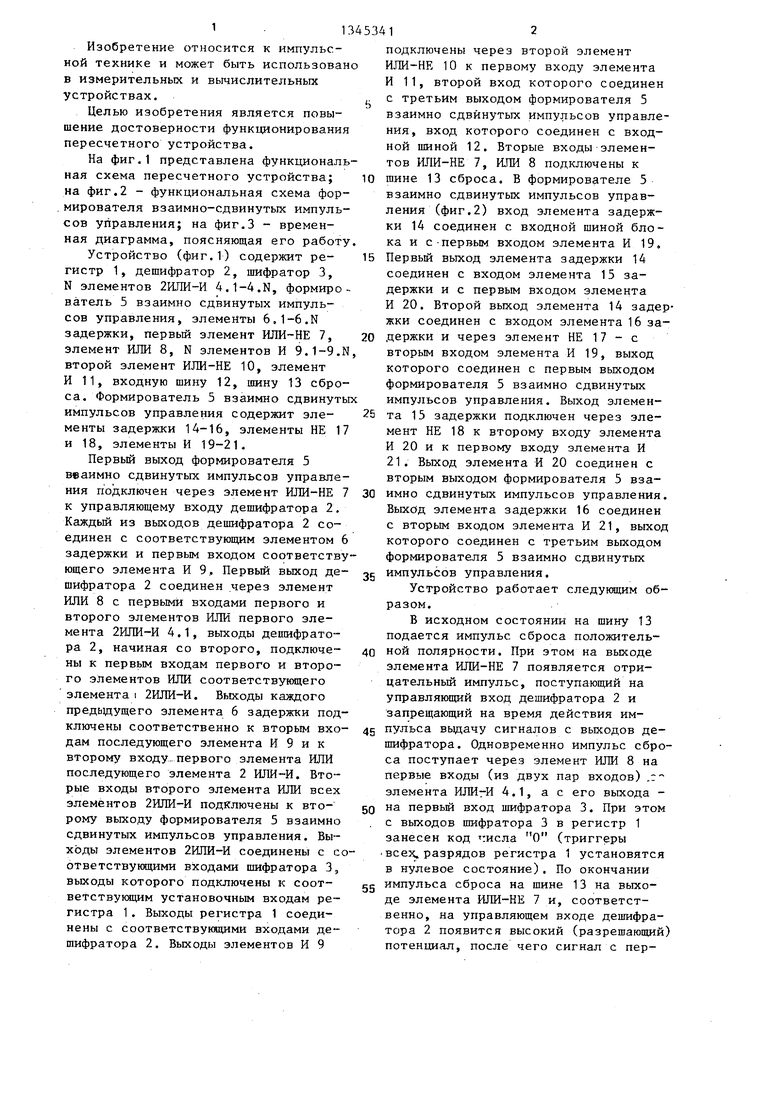

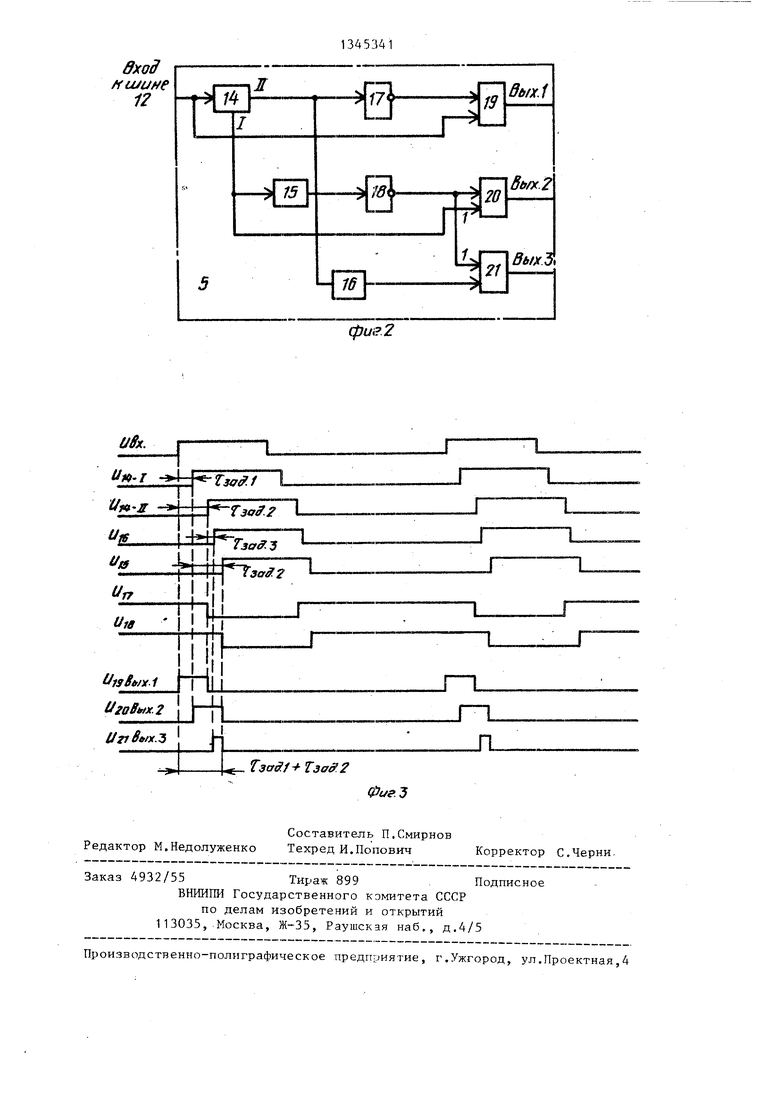

На фиг.1 представлена функциональная схема пересчетного устройства; на фиг.2 - функциональная схема фор- мирователя взаимно-сдвинутых импульов управления; на фиг.З - временная диаграмма, поясняющая его работу

Устройство (фиг.1) содержит регистр 1, дешифратор 2, шифратор 3, N элементов 2ИЛИ-И 4.1-4.N, формирователь 5 взаимно сдвинутых импульсов управления, элементы 6.1-6.N задержки, первый элемент ИЛИ-НЕ 7, элемент ИЛИ 8, N элементов И 9.1-9.N, второй элемент ИЛИ-НЕ 10, элемент И 11, входную шину 12, шину 13 сброса. Формирователь 5 взаимно сдвинутых импульсов управления содержит эле- 25 менты задержки 14-16, элементы НЕ 17 и 18, элементы И 19-21.

Первьй выход формирователя 5 веаимно сдвинутых импульсов управления подключен через элемент ШШ-НЕ 7 к управляющему входу дешифратора 2. Каждый из выходов дешифратора 2 соединен с соответствующим элементом 6 задержки и первым входом соответствующего элемента И 9, Первый выход дешифратора 2 соединен через элемент ИЛИ 8 с первыми входами первого и второго элементов ИЛИ первого элемента 2ИЛИ-И 4.1, выходы депшфрато- ра 2, начиная со второго, подключены к первым входам первого и второго элементов ИЛИ соответствующего элемента 2ИЛИ-И. Выходы каждого предьщущего элемента 6 задержки подключены соответственно к вторым входам последующего элемента И 9 и к второму ВХОДУ-первого элемента ИЛИ последующего элемента 2 ИЛИ-И. Вторые входы второго элемента ИЛИ всех элементов 2ИЛИ-И подключены к второму выходу формирователя 5 взаимно сдвинутых импульсов управления. Выходы элементов 2ИЛИ-И соединены с со- ответствуюощми входами шифратора 3, выходы которого подключены к соответствующим установочным входам регистра 1. Выходы регистра 1 соединены с соответствующими входами дешифратора 2. Выходы элементов И 9

п в н 15 П

в gg и

30

35

40

45

50

0

341

5

подключены через второй элемент ИЛИ-НЕ 10 к первому входу элемента И 11, второй вход которого соединен с третьим выходом формирователя 5 взаимно сдвинутых импульсов управления, вход которого соединен с входной шиной 12. Вторые входы элементов ИЛИ-НЕ 7, ИЛИ 8 подключены к тине 13 сброса, В формирователе 5 взаимно сдвинутых импульсов управления (фиг. 2) вход элемента задержки 14 соединен с входной шиной блока и с-первым входом элемента И 19. 5 Первый выход элемента задержки 14 соединен с входом элемента 15 задержки и с первым входом элемента И 20. Второй выход элемента 14 задержки соединен с входом элемента 16 задержки и через элемент НЕ 17 - с вторым входом элемента И 19, выход которого соединен с первым выходом формирователя 5 взаимно сдвинутых импульсов управления. Выход элемента 15 задержки подключен через элемент НЕ 18 к второму входу элемента И 20 и к первому входу элемента И 21. Выход элемента И 20 соединен с вторым выходом формирователя 5 взаимно сдвинутых импульсов управления. Выход элемента задержки 16 соединен с вторым входом элемента И 21, выход которого соединен с третьим выходом формирователя 5 взаимно сдвинутых импульсов управления.

Устройство работает следуклцим образом.

В исходном состоянии на шину 13 подается импульс сброса положительной полярности. При этом на выходе элемента ИЛИ-НЕ 7 появляется отрицательный импульс, поступающий на управляющий вход дешифратора 2 и запрещающий на время действия импульса выдачу сигналов с выходов дешифратора. Одновременно импульс сброса поступает через элемент ИЛИ 8 на первые входы (из двух пар входов) .г элемента ИЛИгИ 4.1, а с его вькода - на первьм вход шифратора 3. При этом с выходов шифратора 3 в регистр 1 занесен код гисла О (триггеры всех, разрядов регистра 1 установятся в нулевое состояние). Ло окончании g импульса сброса на шине 13 на выходе элемента ИЛИ-НЕ 7 и, соответственно, на управляющем входе дешифратора 2 появится высокий (разрешающий) потенциал, после чего сигнал с пер0

5

0

5

0

вого выхода дешифратора 2, соответствующий нулевому состоянию регистр 1, начнет подаваться через элемент ИЛИ 8 и элемент 2 ШШ-И 4.1 на пер- вьй вход шифратора 3, а с его выходов - на соответствующие установочные входы регистра 1, подтверждая нулевое состояние регистра 1.

Таким образом, в исходном состоянии на первом, втором и третьем выходах формирователя 5 взаимно сдвинутых импульсов управления низкие потенциалы, на выходе элемента ШШ-НЕ 7 высокий потенциал. Высокий потенциал первого выхода дешифратора 2 поступает через элемент ИЛИ 8 и элемент ИЛИ-И 4.1 на первый вход нифратора 3, при этом сигналами с его выходов подтверждается нулевое состояние регистра 1 . Высокий потенциал первого выхода дешифратора 2 поступает также на первый вход элемента И 9.1, закрытого по другому входу, и через элемент задержки 6.1 - на второй вход элемента И 9.2 и на второй вход первой пары входов элемента 2ИЛИ-И 4.2, подготавливая его к пропусканию первого входного (счетного) импульса. На выходах элементов И 9.1-9.N низкие потенциалы, а на выходе элемента ИЛИ-НЕ 10 и.

3««Ai

ii ЗЯй,

зал,

мента И 11 высокий потенциал.

По каждойу импульсу, поступающему на входную шину 12, и, соответственно, на вход формирователя 5 взаимно сдвинутых импульсов управле шя на первом, втором и третьем его выходах формируется по одному импульсу,сдвинутых относительно друг друга и перекрывающихся во времени. На временной диаграмме работы формирователя 5 взаимно сдвинутых импульсов управления (фиг.З) приняты следующие обо- значения:

-время задержки сигнала на первом выходе элемента -14 задержки;

-время -задержки сигнала на втором выходе элемента 14 задержки и время задержки элемента 15 задержки;

-время задержки элемента 16 3 адержки.

Сигнал с входа формирователя 5 взаимно сдвинутых импульсов поступает на вход элемента задержки 14 и на первый вход элемента И 19, на

5

0

5

втором входе которого имеется высокий потенциал с выхода элемента НЕ 17. Элемент И 19 открывается, формируя передний фронт импульса на первом выходе формирователя 5. Через время 1 сигнал с первого выхода элемента задержки 14 поступает на вход элемента 15 задержки и на 0 первый вход элемента И 20, который открывается, формируя передний фронт . импульса на втором выходе формирователя 5. Через время , относительно входного импульса появляется 5 импульс на втором выходе элемента 14 задержки, который поступает на вход элемента НЕ 17 и на вход элемента 16 задержки. При этом закрывается элемент И 19, формируя зад- 0 НИИ фронт импульса на первом выходе формирователя 5, а через время -D сигнал с выхода элемента задержки поступает на второй вход элемента И 21, который открывается, 5 формируя передний фронт импульса на третьем выходе формирователя 5. Через время зад относительно сигнала на входе элемента 15 задержки сигнал с его выхода через элемент 0 НЕ 18 поступает на второй вход элемента И 20 и на первый вход элемента И 21, которые закрываются, формируя задний фронт импульсов соответственно на втором и третьем выходах формирователя 5.

Таким образом, с поступлением импульса на вход формирователя 5 на его первом и втором выходах формируются импульсы длительностью , Импульс на втором выходе отстает от импульса на первом выходе на время io,c(A .На третьем выходе формирователя 5 также формируется импульс, который начинается после окончания импульса на первом выходе через время и заканчивается одновременно с импульсом на втором выходе.

С поступлением на входную шину 12 первого счетного импульса одновременно импульс с первого выхода формирователя 5 взаимно сдвинутых импульсов управления поступает через элемент ИЛИ-НЕ 7 на управляющий вход g дешифратора 2, запрещая на время Сзо., вьщачу сигналов с его выходов. При этом снимается положительный потенциал с объединенных первых входов элемента 2ИЛИ-И 4.1, с его выхо0

1345341 с первого входа

шифратора 3.

Через время ск несколько превышающее общее время прохождения (отпускания) сигнала через элемент ИЛИ-НЕ 7. пешиЛоатоо 2. элементы ИЛИ 8,2ИЛИ-И 4.1 .шифратор 3,импульс с второго выхода формирователя 5 поступает на объединенные «вторые входы вторых па входов элементов 2ИЛИ-И 4, 1-4„Ы.При этом открывается элемент 2ИЛИ-И 4.2, так как на втором его входе первой входов присутствует положительный потенциал с выхода элемента задерж- ки 6.1. Время задержки элементов задержки 6.1-6.N выбирается равным или несколько большим величины з«А, зс.42 Импульс С вькода :элемента ИЛИ-И 4.2 поступает на вто- рой вход шифратора 3, при этом с выходов шифратора 3 в регистр 1 занесен код числа 1.

По окончании импульса на первом выходе формирователя 5 (на управляющем входе дешифратора .2) сигнал с второго выхода дешифратора 2 (соответствующий коду числа 1 в регистр 1) подается на первый вход элемента И 9.2, на вход элемента задержки 6„2 и на первые входы элементов ИЛИ элемента 2ИЛИ-И 4,2 при наличии импульса на втором входе второго элемента ИЛИ. Поэтому по окончании импульса на втором выходе формирователя 5 и на втором входе второго элемента ИЛИ элемента 2ИЛИ-И 4.2 послед

НИИ остается открытым, сигнал с его выхода продолжает поступать на второй вход шифратора 3, подтверждая в регистре код числа 1. Положительный потенциал с второго выхода дешифратора 2 открывает элемент И 9.2 (на время действия сигнала на выходе элемента задержки 6.1), выходной импульс которого поступает через элемент Ш1И-НЕ 10 на первьй вход элемента И 11 и закрывает его. Поэтому импульс с третьего выхода формирователя 5 не проходит на выход элемента И 11 .

Через время + момента появления сигнаЛа на втором выходе дешифратора 2 сигнал с выхода элемента задержки 6.2 поступает на второй вход первой пары входов элемента 2ИЛИ-И 4.3, подготавливая его к пропусканию второго счетного импульса.

8

1

С приходом второго входного счетного импульса импульс с первого выхода формирователя 5 запрещает выдачу сигнала со второго выхода дешифратора 2. Снимается сигнал с первых входов элементов ИЛИ элемента 2ШШ-И 4.2 и, соответственно, с второго входа шифратора 3. Импульс с второго выхода формирователя 5 открывает элемент 2ИЛИ-И 4.3 и с его выхода поступает на третий вход шифратора 3, при этом в регистр 1 заносится код числа 2.

По окончании импульса на первом выходе формирователя 5 сигнал с третьего выхода дешифратора 2 подается на первьй вход элемента И 9.3, на вход элемента задержки 6.3 и на первые входы элементов ИЛИ элемента 2Ш1И-И 4.3. По окончании импульса на втором выходе формирователя 5 элемент 2ИЛИ-И 4.3 остается откры5

0

5

0

поступать на третий вход шифратора 3.

Сигнал с третьего выхода дешифратора 2 открывает элемент И 9.3, выходной импульс которого через элемент ИЛИ-НЕ 10 закрывает по первому входу элемент И 11, поэтому импульс с третьего вЬгхода формирователя 5 не проходит на выход элемента И 11.

Сигнал с выхода элемента задержки 6.3 поступает на второй вход первой пары входов элемента 2Ш1И-И 4.4, подготавливая его к пропусканию третьего счетного импульса и т.д.

Таким образом, с поступлением на входную шину 12 каждого счетного импульса, содержимое регистра 1 увеличивается на единицу. Код числа, соответствующий порядковому номеру входного счетчика импульса, заносится в регистр 1 по переднему фронту импульса с второго выхода формирователя 5 взаимно сдвинутых импульсов управления при прохождении его через соответствующий элемент 2ИЛИ-И на соответствующий вход шифратора 3 и подтверждается затем за счет прохождения через соответствующий открытый элемент 2ИЛИ-И сигнала с соответствующего выхода дешифратора 2. Непрерывное наличие сигнала на вы- -i- ходе соответствующего элемента

2ИЛИ-И на одном из входов шифратора 3 и на соответствующих установочных входах регистра 1 исключает возможность возникновения сбоев в реги5

0

стре 1 как в динамическом, так и в статическом режимах работы устройства.

При отсутствии неисправностей в регистре 1 импульсы, поступающие поочередно с выходов элементов И 9.1-9.N через элемент ИЛИ-НЕ 10, каждый раз закрывают по первому вхо20

ду элемент И 11, поэтому соответству- ig элемента 2ИЛИ-И, первый выход дешифратора соединен с первым входом элемента ИЛИ, вьгход которого соединен с первыми входами первого и второго элементов ИЛИ первого элемента

15 2Ш1{17И, выход каждого предыдущего элемента задержки подключен соответственно к второму входу последующего элемента И и к второму входу первого элемента ИЛИ последующего элемента 2 ИЛИ-И, выход последнего элемента задержки соединен с вторым входом первого элемента ИЛИ первого элемента 2 ИЛИ-И, вторые входы элементов ИЛИ всех элементов 2ШШ-И

25 подключены к второму выходу формирователя взаимно сдвинутых импульсов управления, выходы элементов 2ИЛИ-И соединены с соответствующими входами щифратора, выходы которого подключены к соответствующим установочным входам регистра, выходы которого соединены с соответствующими входами дешифратора, выходы N элементов И подключены через второй элемент ИЛИ-НЕ к первому входу дополнительного элемента И, второй вход которого соединен с третьим выходом формирователя взаимно сдвинутых импульсов, вход которого соединен с входной шиной устройства, при этом вторые входы элемента ИЛИ и первого элемента ИЛИ-НЕ подключены к шине сброса устройства.

ющие им импульсы с третьего выхода формирователя 5 на выход элемента И 11 проходить не будут, В случае отказа одного из триггеров регистра 1, когда с поступлением сигнала на его установочный вход состояние триггера не изменяется на противоположное, нарушается последовательность появления сигналов на выходах дешифратора 2, В результате с поступлением очередного счетного импульса на входную шину 12 импульс на выходе соответствующего элемента И 9 отсутствует, Яоэтому очередной импульс с третьего выхода формирователя 5 пройдет на выход элемента И 11, сигнализируя о неисправности регистра 1 .

Формула изобретения ЗО

Пересчетное устройство, содержащее регистр, N элементов И, элемент ИЛИ, первый элемент ИЛИ-НЕ, дополнительный элемент И, отличающееся тем, что, с целью повы- - шения достоверности функционирования, в него введены дешифратор, шифратор N элементов/ 2ИЛИ-И, N элементов задержки, второй элемент ИЛИ-НЕ и формирователь взаимно сдвинутых импульсов управления, первый выход которого соединен через первый элемент

35

4(;

РШИ-НЕ с управляющим входом дешифратора, каяэдый из N выходов которого подключен к соответствующим элементу задержки и первому входу соответствующего элемента И, выходы дешифратора, начиная с второго, соединены с первыми входами первого и вто« рого элементов ИЛИ соответствующего

20

15

25

35

25

4(;

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный элемент с контролем | 1986 |

|

SU1370779A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Многоканальное устройство для временного разделения и синхронизации импульсных сигналов | 1989 |

|

SU1651361A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для выдачи команд об изменении движения транспорта | 1986 |

|

SU1446640A1 |

| Счетный элемент с контролем | 1990 |

|

SU1765889A1 |

Пересчетное устройство содержит регистр 1, дешифратор 2, шифратор 3, N элементов ИЛИ-И 2 4.1-4.N, формирователь 5 взаимно сдвинутых импульсов управления, элементы задержки 6.1-6.N, элементы ИЛИ-НЕ 7, 10, элемент ИЛИ 8, N элементов И 9.1-9.N, 11, входную шину 12, шину сброса 13. Изобретение повьш1ает достоверность функционирования пересчетного устройства. 3 ил. /fer/J (fiUZ.f

| Кольцевой счетчик с устройством обнаружения ошибок | 1981 |

|

SU1015500A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Двоичный счетчик с обнаружением ошибок | 1984 |

|

SU1169163A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-18—Подача