1

1345355

Изобретение относится к автоматике, вьиислительной технике и может применяться в автоматизированных системах управления технологическим оборудованием.

Цель изобретения - повышение помехоустойчивости устройства за счет контроля длительности входных кодовых импульсов.

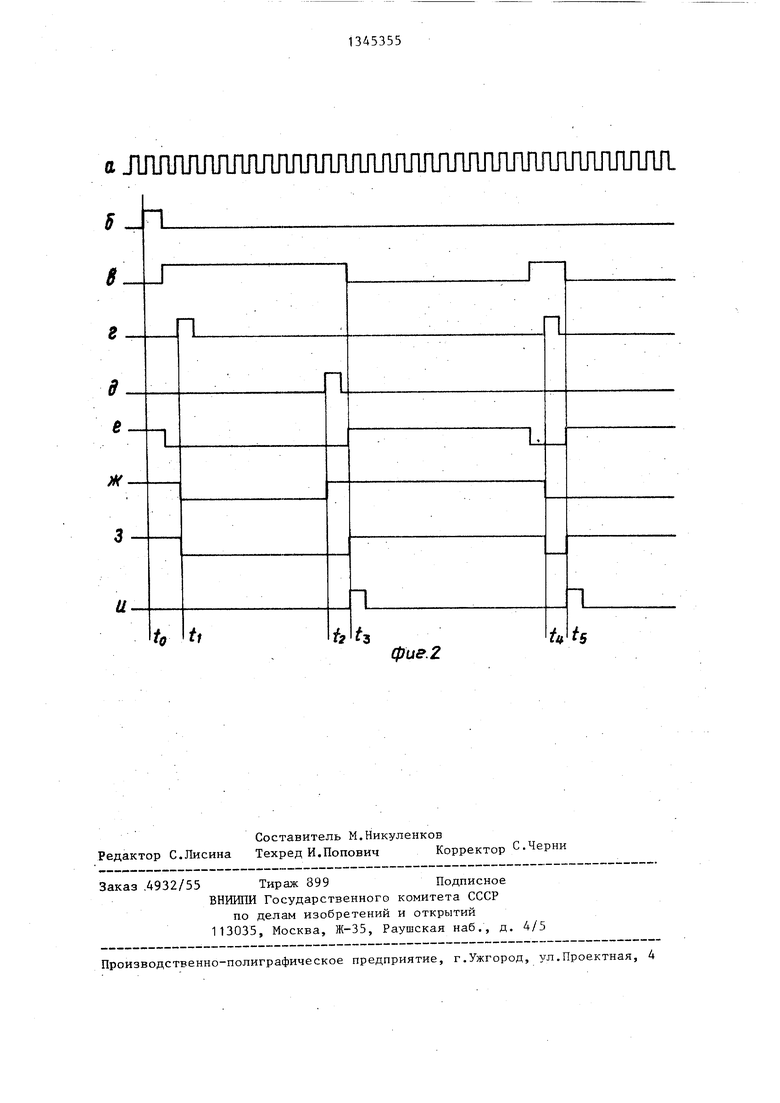

На фиг. 1 представлена функциональная схема предлагаемого устройства, на фиг. 2 - временные диаграммы, поясняющие.его работу.

Устройство содержит (фиг. 1) первый триггер 1 режима, элемент И 2, регистр 3 сдвига, счетчик 4, второй генератор 5 тактовых импульсов, дешифратор 6, второй, третий триггеры 7, 8 и первый генератор 9 тактовых импульсов.

Устройство работает следующим образом.

В исходном состоянии генератор 5 вырабатывает последовательность импульсов (фиг. 2а), сигнал низкого уровня с выхода элемента И 2 удерживает счетчик 4 в нулевом состоянии. Рвбота устройства начинается при по- ступлейии на вход триггера 1 сигнала Начало сообщения (фиг. 26, t, ), который записывает единицу в первый разряд регистра 3, а в остальные разряды - нуль. Одновременно этот сигнал поступает на вход триггера 1, устанавливая его в единичное состояние, открывающее элемент И 2, через который с входа устройства поступает последовательный код. Вследствие того, что разряды последовательного кода единицы и нули передаются импульсами соответственно большой и малой длительности, работу устройства рассмотрим на примере приема первого единичного разряда и второго нулевого разряда (фиг. 2в).

Сигнал высокого уровня,, соответствующий первому единичному разряду, с выхода элемента И 2 постзтает на установочный вход счетчика 4, разблокируя его. Счетчик 4 начинает отсчет импульсов. С его выходов на входы дешифратора 6 в параллельном коде подается число отсчитанных импульсов. Как только это число доходит до величины, соответствующей появлению сигнала высокого уровня, на первом выходе дешифратора 6 (фиг. 2г, t,) происходит установка в нулевое состо355

яние триггера 7

2

(фиг,

2ж,

t.)

и три1-

5

0

0

0

0

гера 8 (фиг. 23,-t). Счетчик 4 продолжает считать и, когда число отсчитанных импульсов доходит до величины, соответствующей появлению сигнала высокого уровня, на втором выходе дешифратора 6 (фиг. 2д, .t) происходит установка в единичное состояние триггера 7 (фиг. 2ж, t), что фиксирует прием разряда последовательного кода уровня единицы. С выхода триггера 7 сигнал высокого уровня поступает на вход первого разряда регистра 3 сдвига. По окончании импульса первого единичного разряда с выхода элемента И 2 сигнал низкого уровня поступает на установочный вход счетчика 4, блокируя его. Счетчик 4 устанавливается в нулевое состояние, и на третьем вьЕХоде дешифратора 6 появляется сигнал высокого уровня (фиг. 2е, tj), устанавливающий триггер 8 в единичное состояние (фиг. 2з, t,).

5 Сигнал высокого уровня с выхода триггера 8 поступает на вход генератора 9, который вырабатывает импульс сдвига (фиг. 2и, tj). Этим импульсом производится сдвиг информации в регистре 3, в первый разряд которого записывается единица с вьвсода триггера 7.

Импульсы помех, поступающие во время паузы между импульсами первого и второго разрядов последовательного

5 кода на установочный вход счетчика 4, производят его разблокировку. Но длительность помех не позволяет счетчику 4 просчитать импульсы для выработки сигнала высокого уровня даже на первом выходе дешифратора 6. Поэтому исключается возможность выработки импульсов сдвига при поступлении на вход импульсов помех.

5 При поступлении сигнала высокого уровня, соответствующего второму нулевому разряду, с выхода элемента И 2 производится разблокировка счетчика 4. Последний опять начинает отсчет импульсов. Как только число импульсов доходит до величины, соответствующей иоявлен по сигнала высокого уровня на первом выходе дешифратора 6 (фиг. 2г, 14), происходит установка в нулевое состояние триггеров 7 Чфиг. 2ж, t4)и 8:(фиг. 2з, t ). Счетчик 4 продолжает считать импульсы, но сигнал высокого уровня на его установочном входе оканчивается, и

5

счетчик 4 устанавливается в кулевое СОСТОЯНИЙ, На третьем выходе депгифра тора 6 -появляется сигнал высокого уровня (фиг. 2е, t.), устанавливающий триггер 8 в единичное состояние (фиг..2з, tj). Сигнал высокого уровня с выхода триггера 8 поступает на вход генератора 9, который вырабатывает очередной импульс сдвига (фиг. 2и, t). Этим импульсом производится сдвиг информации в регистре 3, в первый разряд которого записывается-нуль с выхода триггера 7.

Аналогично производится накапливание и сдвиг остальных разрядов последовательного кода в регистре 3 сдвига. Сдвиги продолжаются п-тактов т.е. до тех пор, пока единица, записанная по сигналу Начало сообщения в первый разряд регистра 3, не продвигается в Ср+1) разряд. Сигнал с выхода этого разряда поступает на вход триггера 1, устанавливая его в нулевое состояние и закрывая элемент И . Наличие единицы в (п+1) разряде свидетельствует об окончании преобразования последовательного кода в Параллельный.

Таким образом, предлагаемое устройство обеспечивает преобразование последовательного кода в параллельный характеризуясь высокой помехоустойчивостью за счет контроля длительности информационных импульсов последовательного кода.

4

рмула изоб

ре тения

0

д

Устройство для преобразования Последовательного кода в параллельный, содержащее первый генератор тактовых импульсов, выход которого сое-, динен с входом сдвига регистра, выход регистра соединен с входом установки в О первого триггера, выход которого соединен с первым входом элемента И, второй вход элемента И и объединенные вход установки в 1 первого триггера и установочный вход 5 регис;тра являются соответственно информационным и установочным входами устройства, отличающееся тем, что, с целью повьшения помехоустойчивости устройства, в него введены второй генератор тактовых импульсов, счетчик, дешифратор, второй и третий триггеры, выходы второго генератора тактовых импульсов и элемента И соединены соответственно со счетным и установочным входами счетчика, выходы которого соединены с соответствующими входами дешифратора, первый выход дешифратора соединен с входами установки в О второго и третьего триггеров, второй и третий вькоды дешифратора соединены с входами установки в соответственно второго и третьего триггеров, выходы которых соединены соответственно с информационным входом регистра и входом первого генератора тактовых импульсов.

0

5

0

tt л1Ш1шплжмл1тлл ш

Составитель М.Никуленков Редактор С.Лисина Техред И.Попович Корректор С.Черни

Заказ .4932/55 Тираж 899Подписное

ВНРШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная, 4

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Коммутатор | 1988 |

|

SU1520664A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Устройство цикловой синхронизации воспроизведения цифровой информации с носителя магнитной записи | 1989 |

|

SU1599895A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Селектор импульсов заданной кодовой комбинации | 1982 |

|

SU1131032A1 |

| Устройство циклового фазирования для волоконно-оптических систем передачи информации | 1988 |

|

SU1540021A1 |

Изобретение относится к автоматике, вычислительной технике и может использоваться в автоматизированных системах управления технологическим оборудованием. Целью изобретения является повышение помехоустойчивости устройства. Устройство осуществляет преобразование последовательного кода в параллельный и контролирует длительность входных кодовых импульсов. Устройство содержит триггеры 1, 7, 8, элемент И 2, регистр 3 сдвига, счетчик 4 и генераторы 5, 9 тактовых импульсов. 2 ил. Н УЙГ (Л с б со N сл 00 СЛ СП П41 ffju.l

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования после-дОВАТЕльНОгО КОдА B пАРАллЕльНый | 1979 |

|

SU809160A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-29—Подача