1

Изобретение относится к вычиаштёльной технике и может быть использовано для аппаратурной реализации функций sin X и С05Х в быстродействующих цифровых вычислительных устройствах.

Известен цифровой функциональный генератор, содержащий блоки для запоминания угловых значений функций и ее производной, дешифратор, сумматор, и множительный блок, соединенный с выходом с входом сумматора, группу элементов И, группу элементов ИЛИ и два регистра, выходы одного из тсоторых соединены с входом множительного бл(жа, а выходы второго через дешифратор подключены к первым входам двух групп элементов И, вторые входы которых соединены с выходами соответствующих раэряд(ж блоков запоминания угловых значений функций и ее производной, причем. ш 1ходы элементов И через соответствук щие элементы ИЛИ подключены соответ ственно к входу множительного блока и к входу сумматора 1 .

Недостаток такого генератора заключается в сложности реализации, обуслов- ленной наличием блока умножения и необходимостью использовать блоки памяти большей емкости для достижения высокой точности.

Наиболее близким к предлагаемому является устройство для вычисления функций синуса и косинуса, содержащее входной регистр, три блока памяти, два блока ум10ножения, сумматор и выходной регистр, выходы старших разрядов входного регистра подключены к адресным входам nej вого и второго блоков памяти, выходы младштос разрядов входного регистра - к

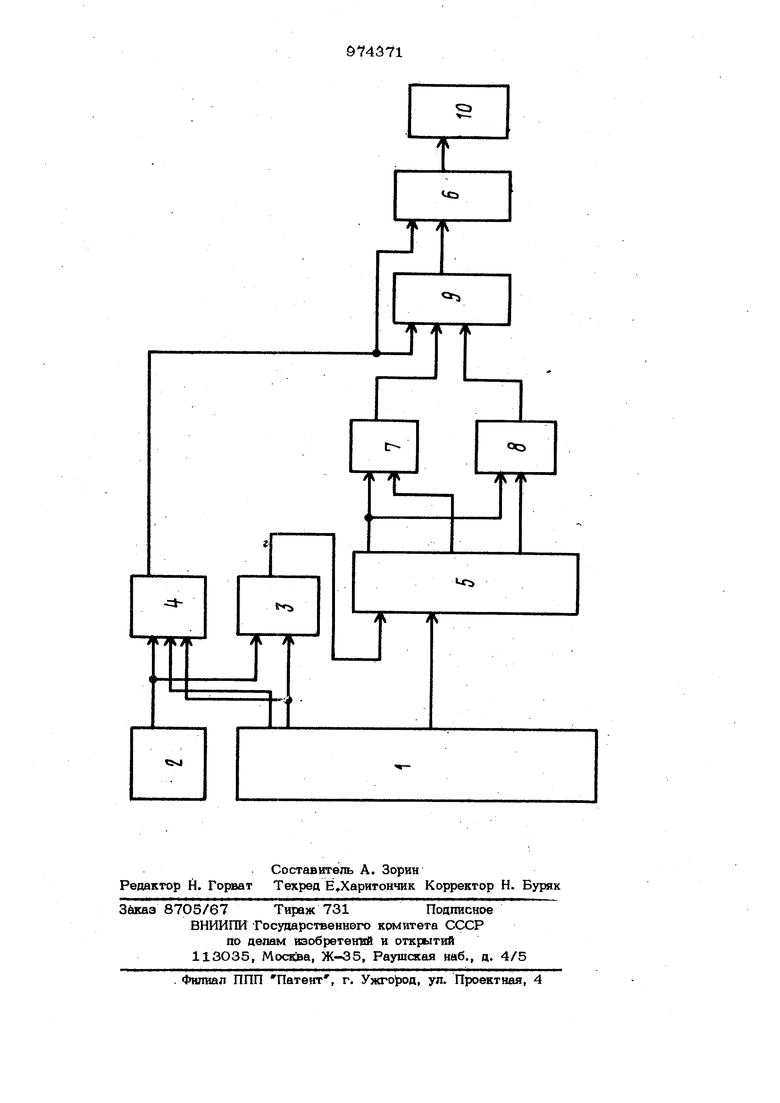

15 первой группе входов блока умножения, вторая группа входов которого подключена к выходам второго блока памяти, выходы блока умножения подключены к nejvвой группе входов сумматора, выход ко20торого подключен к входу выходного регистра, адресные входьт второго блока памяти подключены к вьтходам старшей подгруппы младщих разрядов входного регистра, выходы третьего бпока памяти к первой группе входов, а выходы первого блока памяти - к второй группе входов второго блока умножения, выходы которго подключены к второй группе эходов сумматора 2 . Однако известное устройство обладает сложной конструкцией. Целью изобретения является упрощение устройства. Поставленная цель достигается гем, что в устройстве для вычисления функций SfnK,co5X , содержащем входной регкстр триггер, сумматор по модулю два, блок анализа квадранта, два блока памяти, сумматор, два коммутатора и выходной регистр, причем выход триггера соединен с первыми входами блока анализа квадранта и сумматора по модулю два, вторые входы которых соединены с выходом второго разряда входного регистра, выход первого разряда и выход разрядов с трет его до п -го (где п - разрядность аргумента) которого соединены соответственно с третьим входом блока анализа квадранта и информационным входом первого коммутатора, управляющий вход которого соединен с выходом сумматора по модулю два, выход блока анализа квадранта соединен с управляющим входом второго коммутатора, выход и информационный вход которого соединены соответственно с входом выходного регистра и выходом сумматора, первый выход первого коммутатора соединен с первыми входами первого vi второго блоков памяти, второй и третий выходы первого коммутатора соединены соответственно со вторыми входами первого и второго блоков памяти, выходы которых соединены собтветствённо с первым и вторым lтафop a- ционкыми входами сумматора, управляющий вход которого соединен с выходом блока анал11за квадранта. На чертеже представлена блок - схем устройства. Устройство для вычисления функций Sinx и cos X содержит входной регистр 1 триггер 2, сумматор 3 по модулю два, eiicac 4 анализа квадранта, коммутаторы 5 « 6, блоки 7 и 8 памяти, сумматор 9 выходной регистр Ю. Сумматор 3 должен вырабатывать логическую функцию Фг; Фл Б + F, а блок анализа квадранта 4 должен вырабатывать логическую функцию Ф,.: АБ + AF + BAF. десь А и Б - два старщих разряда кода угла, определяющие номер квадранта, F - код функций (Р О при вычислении функции sinx, F l при вычислении функии cos X) Устройство работает следующим образом. В регистр 1 записывается код аргумента, выраженный в единицах - , где - код аргумента в радианах. Коммутатор 5 пропускает на входы блоков 7 и 8 прямой или инверсный код агрумента, в зависимости от управляющего сигнала, вырабатываемого сумматором 3. Представим аргумент в виде х а + в + с. Тогда (X) f (а+Ъ)+ f(a+b)c+ (а + Ъ)сЯ Если произвести разбиение кода аргумента на группы разрядов а, Ъ и с так, чтобы произведение П f (а+Ъ)с было меньще единицы младщего разряда, получим (Х)(((;.()д + ()(|2)с, f(X)csf {c(4.ij) + f(|C, °nv f c,,, . Первый блок 7 вырабатывает код точного значения функции sinxl., а второй блок 8 реализует табличное устройство умножения. С выхода второго блока 8 на вход сумматора 9 подается код f(f УС-12 , т.е. код добавки минус единица младшего разряда, а на третий вход сумматора подается единица; если выходной код не будет преобразовываться в дополнительный, и подается ноль, если выходной код будет преобразоваться. При реализации 16-разрядных функций в группу а входят разряды со второго по щестой, в группу в - разряды с седьмого по десятый, в группу с - разряды с одиннадцатого по пятнадцатый. Предложенная структура устройства вычисления функций ч и cos х позволяет отказаться от двух блоков умножения, что снижает аппаратурные затраты и и сложность изделия. Формула изобретения Устройство ДЛИ вычисления функций sin X. исо5х , содержащее входной регистр, триггер, сумматор по модулю ова, блок аналмза квадранта, два блока памят сумматор, два коммутатора и выходной регистр, прулем выход триггера соединен с первыми входами блока анализа квадранта и сумматора по модулю два, вторые входы которых соединены с выходом второго разряда входного регистра, выход первого разр51да и выход разрядов с третьего до й-го (где п - разрядность аргумента) которого соединены соответ ственно с третьим входом блока авалюа квадранта и информационным входом перм Ього коммутатора, управляющий вход которого соединен с выходом сумматора по модулю два, выход блока анализа квадранта соединен с управляющим входом второго коммутатора, выход и информа-. ционный вход которого соединены соот ветственно с входом выходного регистра 9 71« и выходом сумматора, пе{шый выход первого коммутатора соединен с первыми входами первого и второго блоков памяти, отличающееся тем, что, с целью упрощения уст зойства, второй и третий выходы первого коммутатора соединены соответственно со вторыми входами первого и второго блоков памяти, выходы которых соединены соответ- ственно с первым и вторым информационными входами сумматора, управляющий вход которого соединен с выходом блока анализа квадранта. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 504195, кл. G; 06 F 1/О2, 1975. 2.Авторское свидетельство СССР № 622О90, кл. G 06 F 7/548, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1061136A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

t k

Т

i i

Авторы

Даты

1982-11-15—Публикация

1981-02-27—Подача