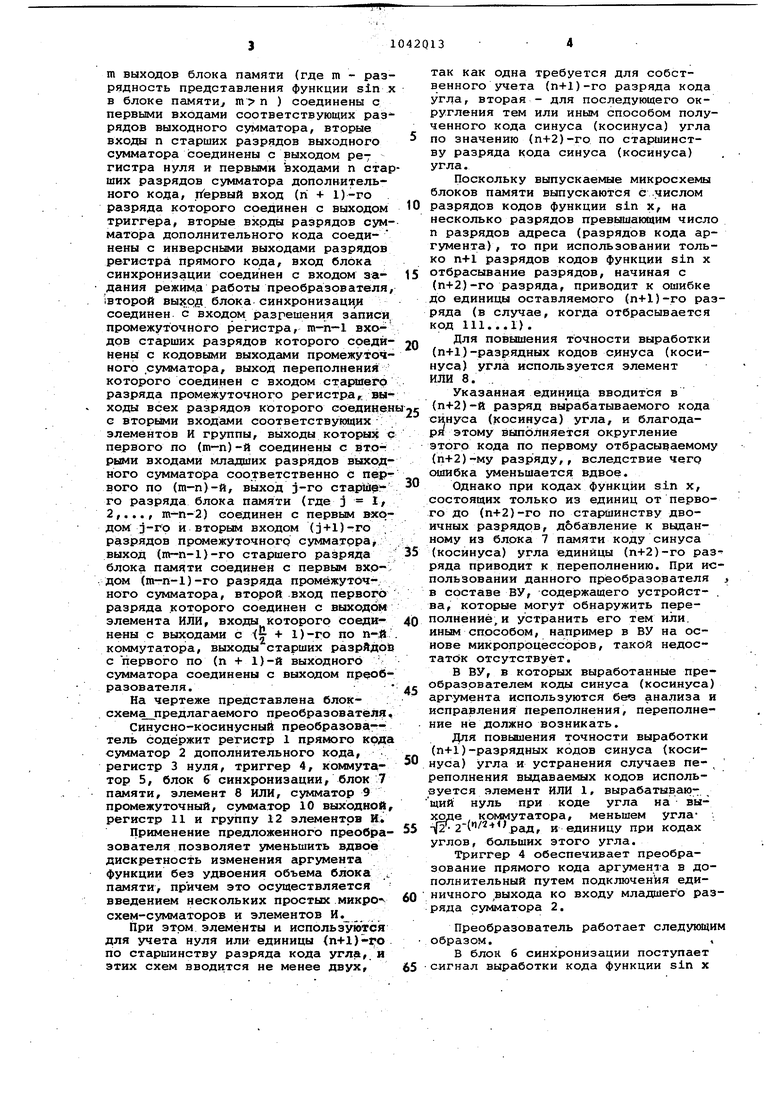

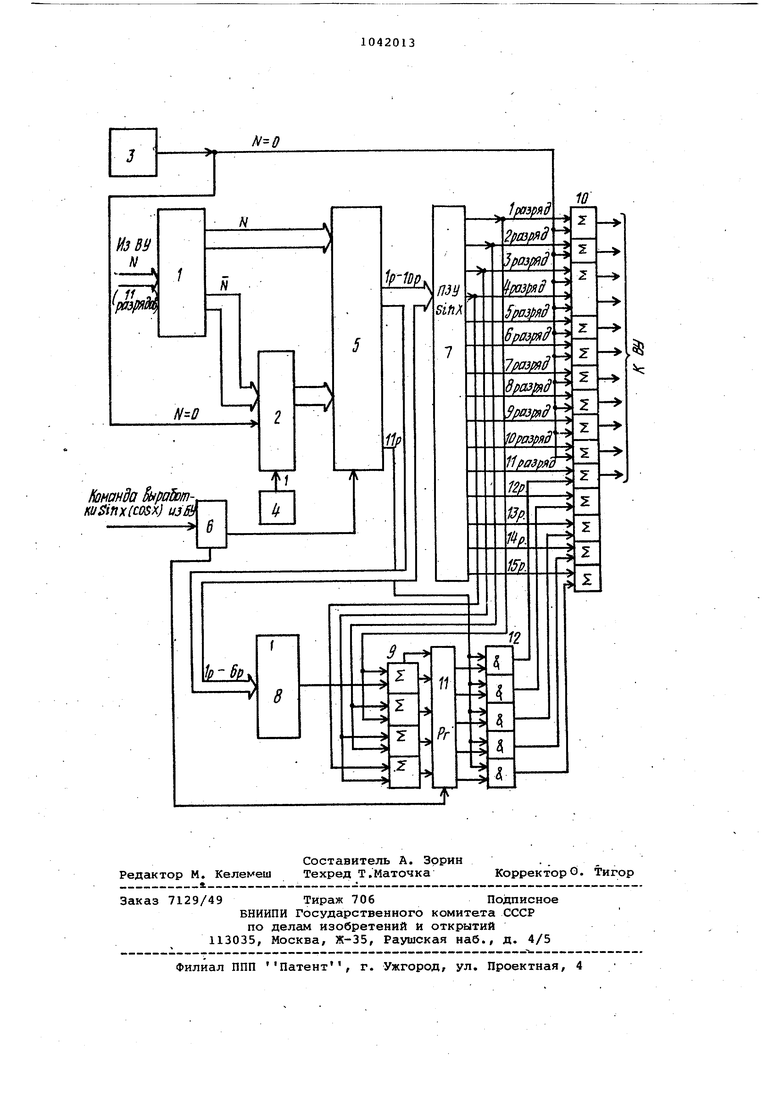

Изобретение относится к вычислительной технике и может быть исполь зовано в цифро-аналоговых вычислите ных устройствах (ВУ), например в на вигационных ВУ, работающих с датчиками и потребителями, в которых углы выдаются и принимаются с помощью сннусно-косинусных вращающихся тран форматоров или сельсинов. Одной из наиболее частых операций в таких цифро-аналоговых вУ является преобразование двоичных кодо обрабатываемых, углов в двоичные коды синусов и косинусов этих углов, в .том числе для последующего преобразования кодов синусов и косинусов углов в напряжения. Такое преобразование кода угла в код синуса (косинуса) этого угла м.ожет выполняться с помощью постоянных запоминающих устройств (ПЗУ), в которых запи сана таблица двоичных кодов значений функций sin X в пределах квадранта при изменении угла-аргумента (0-9и) (1-2), где п - число разрядов, адреса ПЗУ - разрядов кода, подаваемого в ПЗУ угла. При этом в первом квадранте код функции sin х получают в ПЗУ при подаче в него прямого кода угла, а код функции cos х - пр подаче в ПЗУ sin х дополнительного кода угла. В других квадрантах коды функций sin X и .cos X (в- том числе знаки величин) получают по известным из тригонометрии соотношениям, связывающим эти функции с функциями sin X cos X угла х, расположенного в Ч1ервом квадранте. Известен преобразователь, сконструированный на базе стандартного постоянного, запоминающего устройст.в Коды значений функции sin х, записанные в ПЗУ имеют число двоичных разрядов, большее чем число разрядов адреса ПЗУ (число разрядов двоичного кода аргумента, подаваемого в ПЗУ). При использовании ПЗУ это позволяет интерполировать значения функций sin X (cos х) в промежутках Тлежду значениями, записанными в ПЗУ и тем самым уменьшить дискретность изменения аргумента. В указанном преобразователе число разрядов адреса - 10, так что дискретность изменения угла, подаваемого в ПЗУ, ра на 5,3 (90°/2°.. Значения же функции sin X записаны в виде 16-ти раз рядных кодов, так что при интерполя ции можно уменьшить дискретность изменения угла от 2 до 64 раз ij j Известное ус гройство имеет следу ющие недостатки: во-первых, при необходимости уменьшения дискретности изменения аргумента для них требуется ЦВМ заменяющее ее ВУ, осуществляющее инт.ерполяцию; во-вторых при интерполяции для уменьшения дис кретности изменения аргумента даже только в 2 раза требуется по два обра щения ПЗУ при выработке каждой из функций sin X и cos X (для получения двух соседних значений функции) и вычисления разностей соседних значений. Наиболее близким по технической сущности к изобретению является преобразователь двоичного кода угла в двоичньгй код синуса (косинуса) этого угла, содержащий датчик прямого и дополнительного кодов угла, блок памяти с записанной в нем таблицей двоичных кодов значений функции sin х при изменении угла в пределах квгщранта, коммут-атор и блок синхронизации, адресные входы блока памяти имеют п разрядов и через коммутатор подключены к выходам датчиков прямого и дополнительного кодов углов, управляющий вход коммутатора подключен к ВЫХОДУ блока синхронизации, а датчики прямого и дополнительного кода выполняют функции регистра и сумматора 2 . Недостатком данного преобразователя является то, что без ВУ-интерполятора он позволяет вырабатывать коды значений функций sin х (cos х) при изменении аргумента с дискретностью , определяемой числом разрядов адреса блока памяти, а при необходимости уменьшить вдвое эту дискретность позволяет.выполнить это только путем удвоения объема блока памяти. Цель изобретения - повышение точности за счет уменьшения дискретности изменения аргумента и функции без увеличения объема памяти. Поставленная цель достигается тем, что в синусно-косинусный преббразователь, содержащий регистр прямого кода, сумматор дополнительного кода, коммутатор, блок памяти на п вводов, (где п + 1 - разрядность входного кода) и блок синхронизации, первый выход которого соединен с управляющим входом коммутатора, п старших разрядных выходов которого соединены с входом, блока памяти, первая группа п + 1 инфорянационных входов коммутатора соединена с прямыми выходами п + 1 разрядов регистра прямого кода, вход которого соединен с (п + 1)-м разрядным входом аргумента преобразователя, выходы сумматора дополнительного кода соединены с второй группой п + 1 информационных входов коммутатора, дополнительно введены регистр нулевого кода, триггер, элемент ИЛИ, выходной сумматор, промежуточный сумматор, промежуточный регистр и группа элементов И, первые входы которых соединены с вы ходом старшего разряда коммутатора. m выходов блока памяти (где m - раз рядность представления функции sin в блоке памятиJ т п ) соединены с первыми входами соответствующих раз рядов выходного сумматора, вторые входы п старших разрядов выходного сумматора соединены с выходом регистра нуля и первыми входами п ста ших разрядов сумматора дополнительного кода, первый вход (п + 1)-го разряда которого соединен с выходом триггера, вторые вхрды разрядов сумматора дополнительного кода соедииены с инверсными выходами разрядов регистра прямого кода/ вход блока синхронизации соединен с входом задания режима работы преобразователя IB торой выход блока синхронизаци соединен с входрм разрешения записи промежуточного регистра, m-n-1 входов старших разрядов которого соедйне ны с кодовыми выходами промежуточного сукплатора, выход переполнения которого соединен с входом стариего разряда промежуточного регистра,; выходы всех разрядов которого соединен с вторЕлми входами соответствующих элементов И группы, выходы которых С первого по (т-п)-и соединены с вторыми входами младших разрядов выходного сумматора соответственно с первого по (т-п)-й, выход j-ro старшего разряда блока памяти (где j 1/ 2 ,..., m-n-2) соединен с первым входом д-гр и вторым входом (j+l)-ro разрядов прсмежуточногр сумматрра выход (т-п-1)-го старшего разряда блока памяти соединен с первым входом (m-n-l)-ro разряда промёжутРч-, ного сумматора, второй вход первого разряда которого соединен с выходом элемента ИЛИ, входы которогр соединены с выходами с + 1)-го по п-й коммутатора, выходы старших разрйдрв с первого по (п + 1)-й выходного сумматора соединены с выходом преобразователя. На чертеже представлена блок- : схема предлагаемого преобразователе Синусно-косинусный преобразовав- тель содержит регистр 1 прямого кода сумматор 2 дополнительного кода, регистр 3 нуля, триггер 4, коммутатор 5, блок 6 синхронизации, блок 7 памяти, элемент 8 ИЛИ, сумматор 9 промежуточный, сумматор 10 выходной регистр Ни группу 12 элементрв И. Применение предложенного преобразователя позволяет уменьшить вдвое дискретность изменения аргумента функции без удвоения объема блока ,. памяти, причем это осуществляется введением нескольких простых микро схем-сумматоров и элементов И. При этрм элементы и испрльзуются для учета нуля или единицы (п-И)-го по старшинству разряда кода угла, и этих схем вводится не менее двух, так как одна требуется для собственного учета (п+1)-го разряда кода угла, вторая - для последующего округления тем или иным способом полученного кода синуса (косинуса) угла по значению (п+2)-го по старшинству разряда кода синуса (косинуса) угла. Поскольку выпускаемые микросхемы блоков памяти выпускаются с .числом разрядов кодов функции sin х, на несколько разрядов превышакиаим число п разрядов адреса (разрядов кода аргумента) , то при использовании только п+1 разрядов кодов функции sin х отбрасывание разрядов, начиная с (п+2)-го разряда, приводит к ошибке до единицы оставляемого (п+1)-го разряда (в случае, когда отбрасывается код 111...1). Для повышения точности выработки (п+1)-разрядных кодов сянуса (косинуса) угли используется элемент ИЛИ 8. . Указанная единица вводится в (п+2)-и разряд вырабатываемого кода синуса (косинуса) угла, и благодаря этому выполняется округление этогр кода по первому отбрасываемому (п+2)-Му разряду,, вследствие чегр еняибка уменьшается вдвое. Однако при кодах функции sin х, состоящих только из единиц от первого до (п+2)-го по старшинству двоичных разрядов, дббавление к выданному из блока 7 памяти коду синуса (косинуса) угла единицы (п+2)-го разряда приводит к переполнению. При использовании данного преобразователя , в составе ВУ, содержащего устройст- . ва, которые могут обнаружить переполнение, и устранить его тем или. иным спрсобрм, например в ВУ на основе микропроцессоров, такРй недостатрк отсутствует. В ВУ, в которых выработанные преобразрвателем коды синуса (косинуса) аргумента используются б&з анализа и исправления переполнения, переполнение не должно возникать. Для повшиения точности выработки (п+1)-разрядных кодов синуса (косинуса) угла и устранения случаев переполнения выдаваемых кодов используется элемент ИЛИ 1, вырабатывающий нуль при коде угла на выходе коммутатора, меньшем угла 2 2(, и единицу при кодах углов, больших этого угла. Триггер 4 обеспечивает преобразование прямого кода аргумена а в дополнительный путем подключения единичного выхода ко входу младшего разряда сумматора 2. Преобразователь работает следующим образом. В блок б синхронизации поступает сигнал выработки кода функции sin х ИЛИ- cos X, а в регистр 1 - (п+1)-ра рядный код-угла N(,n (индексом п+1 внизу обозначена разрядность кода 3сли,например, поступил сигнал вы работки кода функции sin х по коду (ии) угла X, то блок 6 синхронизаци выдает в коммутатор 5 сигнал подклю чения адресных входов блока 7 памят к выходам сумматора 2, вырабатывающего дополнительный код %(+(). Старшие п разрядов дополнительного кода угла в виде кода поступают на адресные входы блока 7 памяти, и по ним выдается код функции sin N/ff, (конкретные значения функций, получаемые по соответствую щим кодам, в дальнейшем обознача ются как функции этих кодов). Старшие щ-п-1 разрядов этого код (в рассматриваемом примере - че тыре) поступают на входы сумматора 9 как 4-х разрядный код, причем он по ступает на первые входы соответству ющих разрядов сумматора 9, и сдвинутый монтажно на один разряд, - на вторые входы сумматора 9. Таким образом, в сумматоре 9 этот код складывается с кодом, умноженным на 2 т.е. происходит умножение этого код на 1,5. Этот код поступает из сум. матора 9 на входы регистра 11 и записывается там по сигналу записи кода, поступающему в регистр 11 из блока 6 синхронизации с задержкрй от указанного выше сигнала в коммутатор 5 о передаче в блок 7 кода Nou на время прохождения кода через ком мутатор 5, выработки кода sin п коду Nrf и суммирования кодов в сум маторе 9. Из регистра 11 код поступает на входы двухвходовыхэлементов И 12, затем блок 6 синхронизации выдает в коммутатор 5 сигнал передачи на адресные входы блока прямого кода N.f| угла из датчика 1. При этом из блока 7 на входы сумматора 10 выдается код функции sin Nfl, на другие входы п старших, разрядов поступают нули, а (п+1)-го и следующих по старшинству разрядов сумматора 10 поступает код с выходов элементов И. На первые входы элементов И 12 подается (п-М)-й разряд кода угла с выхода коммутатора 5. Если значение этого разряда равно О, код из регистра 11 через элементы И 12 не проходит, если оно равно , то код с ре.гистра 11 проходит на ci MaTop 1р. Таким образом, элементы И 12 осущест вляют умножение одноразрядного чис-ла - значения (п+1)-го разряда кода угла - на 4-х разрядный код функции sin Nern г умноженный на 1,5. Если код на выходе элементов И 12 обозначить как Ь, (п+Г)-й разряд кода t) как (N, то получим Ыц 1,5 sin NxH6N Но, так как Nk + , то sin NgjjScos N. Следовательно ,5 cos cros N. 1,5SN. Ho двоичные коды, поступакицие в блок 7, представляют собой правильные двоичные дроби от угла 90, в которых опущены О единиц и запятая перед Дробью. Если любой из этих кодов умножить наil/2ft 1, 5, то получатся коды, представляющие собой двоичные дроби от радиана, так что 1,5$ N - это угол в радианах. Но тогда код NU представляет собой -приращение функции sin NIJ при изменении угла на S N. 8 s4n N, cos N.SN (рад). A сумма значения функции sin Nf, и приращения 6 sin Nj представляет собой значениефункции sin(f,+8N) s-in(Nf,+8N)sin Ы,т5Ы(рад). Таким образом, сумматор 10 осуществляет выработку функции sin(Njj + +SN)sin Nnti/ т.е. значение синуса угла, заданного (п+1)-разрядным, кодом, что и требуется для уменьшения вдвое дискретности изменения угла ПО сравнению с углом, заданным п-разрядным кодом, поступающим в блок 7 памяти. При этом необходимо учитывать:значения функции-sin X, запис1аниые в бло ке 7 памяти,всегда меньше единицы и представляют собой правильные двоичные дроби, в которых опущены О единиц и запятая перед дробью; единица первого по старшинству разряда этой дроби абозначает 2, второго разряда - 2 и- т.д.; первый по старшинству разряд кода sin Njj подается на блок 7 памяти на вход первого по старшинству разряда сумматора 9, так что на выходе этого разряда сумматора 9 единица означает ту же величину, что и единица старшего разряда кода sin Ng, т.е. единицы на выходах следующих по старшинству разрядов сумматора 9 означают соответственно 2 , 2 и т.д; единица на выходе переноса изстаршего разряда сумматора 9 означает 1; регистр 11 повторяет код на выходс1Х сумматор а 9, так что на его выходах единицы кода означают соответственно 1, 2, 2 . значение угла, выргикаемое единицей (п+1)го разряда, поступающего с (п+1)-го разряда выхода кошлутатора 5 .на вт6- рые входы элементов И 12, равно 90 ,2-;(h+i) -элементы И 12 умножают угол 90°. величину 1,5 cos N, поступающую из регистра 11 в виде, кода со значениями единиц 1, 2, и т.д., поэтому на выходах элементов И 12 единицы кода означают соответственно (учитывая перевод в радианы за счет коэффициента It-/2 t 1,5) : l,2-(n 2(in-0 2 -1-1 ,2. ,-(140 2-. 2 2 -4 ,-ИМ o-fn+5) При монтажном сдвиге кода с выходов старших разрядов блока 7 памяти при подаче его в сумматор 9 ос тается свободным второй вход старше го разряда, который соответствует после прохождения через элементы И (п+2)-му разряду кода sin N. Для округ;ления по этому разряду кода функция sin N на этот вход сумматора 9 подается единица с элемента ИЛИ 8, Для устранения случаев переполне ния эта единица подается, когда код синуса угла не содержит единицы во всех старших разрядах до (п+2)-го включительно, т.е. при углах, которые не превышают угла (),, где Но тогда дополнительный код должен быть не меньше tsL . Такая проверка дополнительного кода Ы.г„ производится элементом ИЛИ в.Выработка кода функции cos N.,) осуществляется аналогично, но при этом сначала передается, прямой код NH, по нему вырабатывается и запоминается поправка к. косинусу п-разряд-. ного кода угла, а потом подается до-полнительный код , в блоке 7 памяти вырабатывается значение cos Ыц, которое в сумматоре 9 суммируется со своей поправкой, включающей единицу (п+2)-го разряда для округленияПрименение предлагаемого преобразователя позволяет уменьшить вдвое ошибки из-за дискретности изменения аргумента функции sin х (cos х) без увеличения объема блока памяти с помощью несложной схемы.

N

Из В У

.J

N (

10

1разряд

2разряд

Jpojpfid

rV

/7J

i-i

Spgjp S

алл

.

Tpamd

V:

tn

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор гармонических функций | 1983 |

|

SU1224802A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| Устройство для вычисления синуса и косинуса угла табличным методом | 1986 |

|

SU1348830A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Устройство для вычисления функций SIN х и coS х | 1981 |

|

SU974371A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр прямого кода, сумма:тор |1ополнительного кода, коммутатор, блок памяти на П входов (где и +1 - разрядность входного кода) и блок синхронизации, первый выход которого соединен с управляющим входом коммутатора, п старших разрядных выходов которого соединены с-входом блока памяти, первая группа п +1 информационных входов коммутатора соединена с прямыми выходами ц +1 разрядов регистра прямого кода, вход которого соединен с (tl+l) ям разрядным входом аргумента преобразователя, выходы сумматора .дополнительного кода соединены с второй группой п +1 информационных входов коммутатора, о т л и ч а ющ и и с я тем, что, с целью повышения точности за счет уменьшения диеткретности изме{1ения аргумента и функцни без увеличения объема памяти, в него введены регистр нулевого кода, триггер, элемент ИЛИ, выходной сумматор, промежуточный сумматор, промежуточный .регистр и группа элементов. И, первые входы которых соединены с выходом старшего разряда коммута-.тора, гп выходов блока пг1мятй (гдегН разрядность представления функции sin X в блоке памяти; | п) соединены с первыми входами соответствующих разрядов выходного сумиатора, вторые входы Ц старших разрядов выходного сумматора соединены с выходом регистра нуля и первьми входами И старших разрядов сумматора дополнительного кода, первый вход (rt+l)-ro разряда которого соединен с выходом триггера, вторые входы разрядов сумматора дополнительного кода соединены с инверсными выходами разрядов регистра прямого кода, вход блока синхронизации соединен с входом задания режима работы преобразователя, второй выход блока синхронизации соединен с входом разрешения записи промежуточного регистра,ГП входов старших разрядов которого соединены с кодовыми выходами проме(Л жуточного сумматора, выход переполнения которого соединен с входом старшего разряда промежуточного регистра, выходы всех разрядов которого соединены с вторыми входгми соответствующих элементов И группы, выходы которых с первого по (т-(|)-й ) соединены с вторьми входами Младших разрядов выходного сумматора соответственно с первого по (т-гЛ)-й, :выход j -гр старшего разряда блока памяти (где J 1,2,. .. ,m-n-2) соединен с первым ВХОДОМ) -го и вторшл входом (J+1)-го .разрядов промежуточного сумматора, выход (m-n-l)-ro старшего разряда блока памяти со.единен с первым входом (m-n-l)-ro разт ряда промежуточного сумматора, второй вход первого разряда которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами + 1)-го поп-и коммутатора, выходы старших разрядов с первого по (П+1) -и выходного сумматора соединены с выходом преобразователя.

Команда paSu/nKuSinx co$x) uj&i

1Рраз1)яд

11раз1 я1

0/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения целлюлозы из стеблей хлопчатника | 1912 |

|

SU505A1 |

| Карат-М | |||

| Техническое описание | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-09-15—Публикация

1981-07-06—Подача