очередей заявок. Цель изобретения - расширение области применения устройства за счет постановки поступающих на обслуживание заявок в общую очередь. Устройство состоит из блока 1 памяти, дешифратора 6, счетчика 2, регистра 3, коммутатора 4, схемы сравнения 5, элементов И 9-13, 15,

1

Изобретение относится к вычислительной технике и может быть использовано для сфганизации приоритетного обслуживания и приоритетных очередей заявок.

Цель изобретения - расширение области применения устройства за счет организации общей очереди заявок.

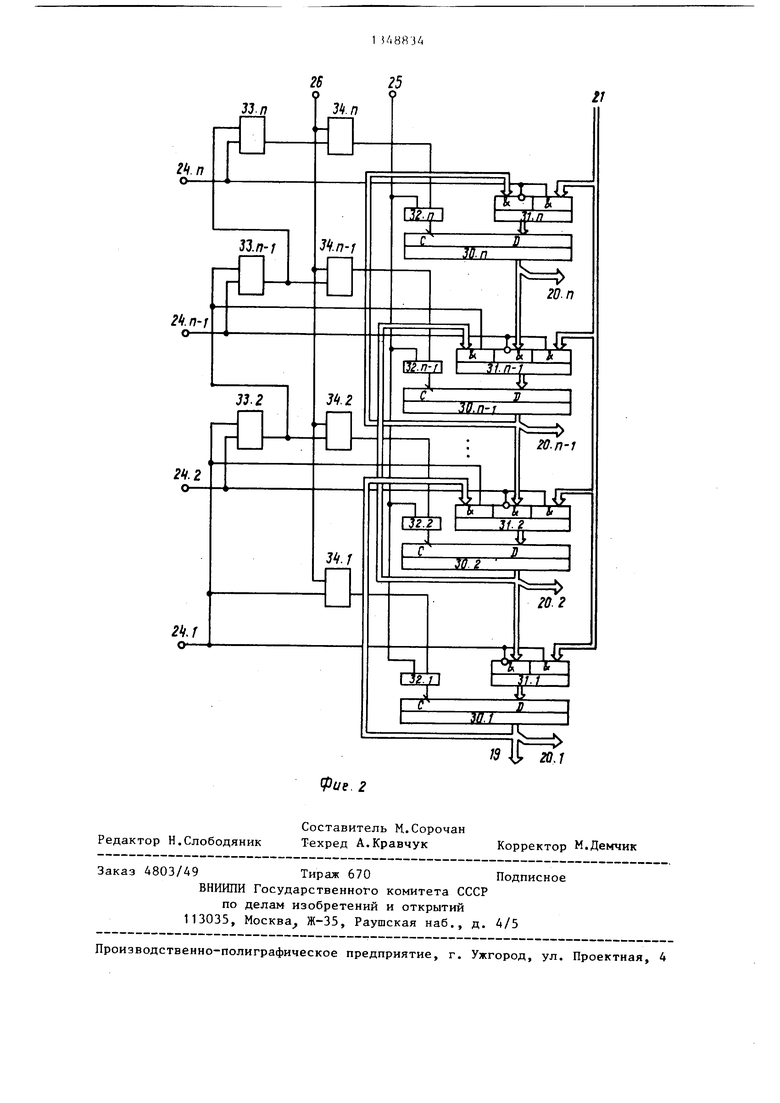

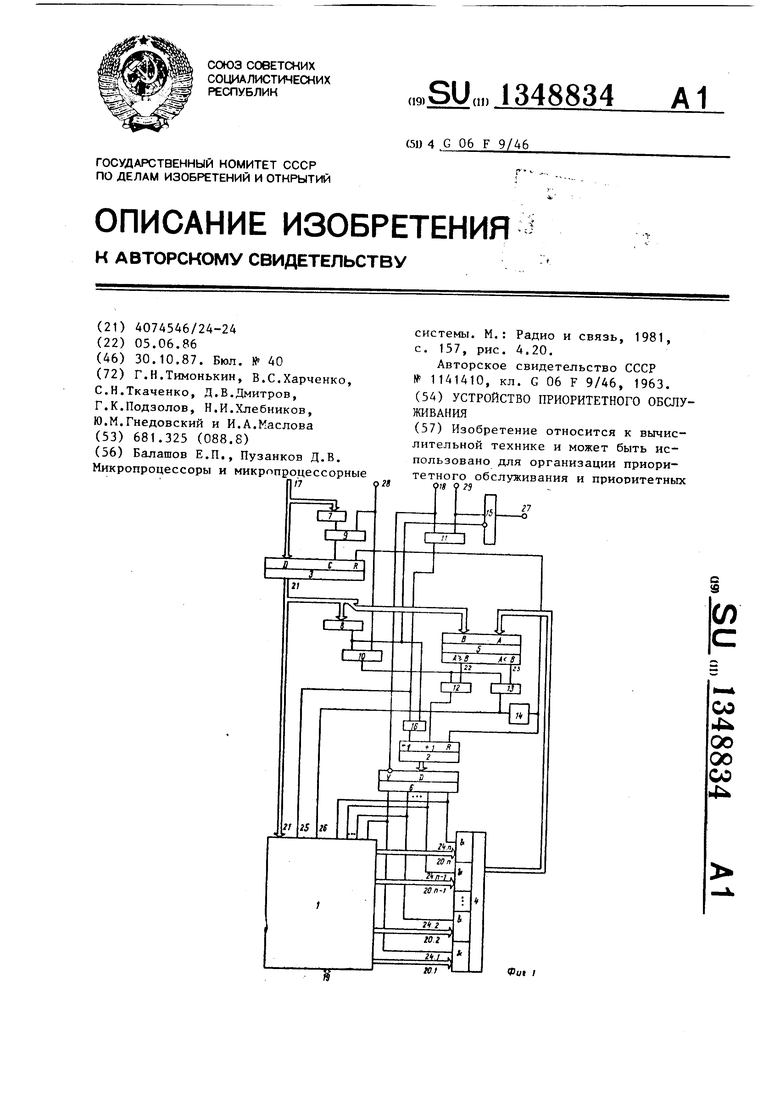

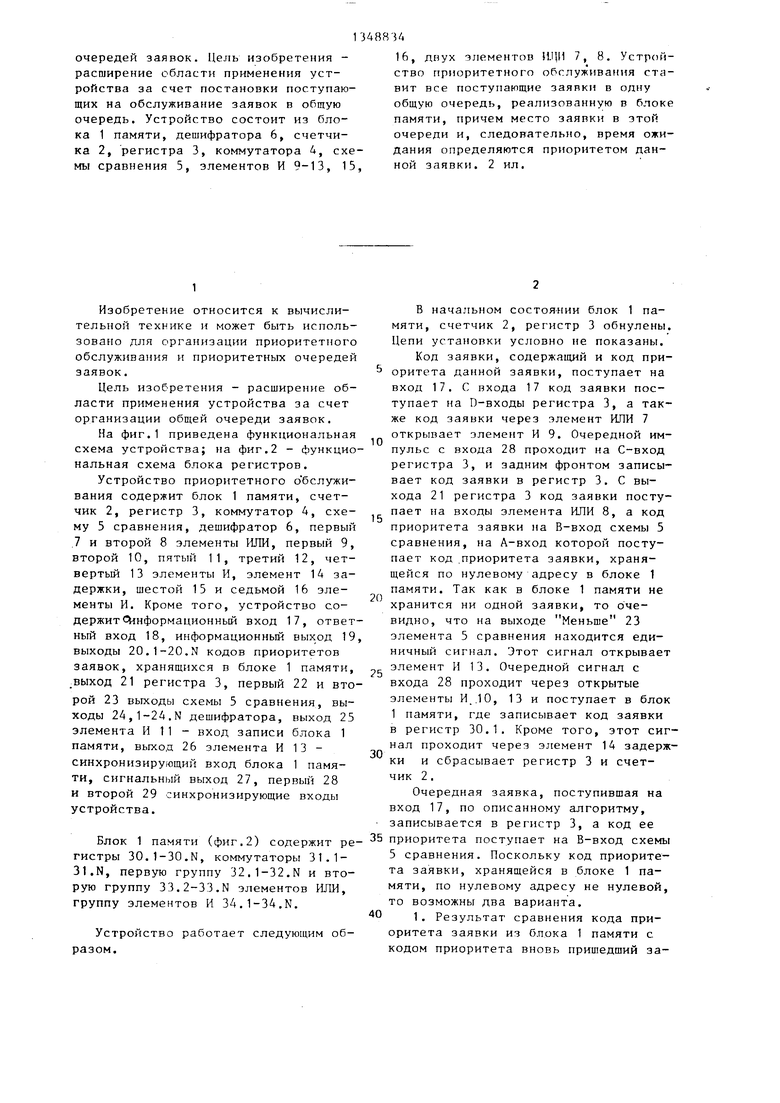

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока регистров.

Устройство приоритетного о бслужи- вания содержит блок 1 памяти, счетчик 2, регистр 3, коммутатор А, схему 5 сравнения, дешифратор 6, первый 7 и второй 8 элементы ИЛИ, первый 9, второй 10, пятый 11, третий 12, четвертый 13 элементы И, элемент 14 задержки, шестой 15 и седьмой 16 элементы И. Кроме того, устройство содержит Информационный вход 17, ответный вход 18, информационный выход 19, выходы 20.1-20.N кодов приоритетов заявок, хранящихся в блоке 1 памяти, выход 21 регистра 3, первый 22 и второй 23 выходы схемы 5 сравнения, выходы 24,1-2А.N дешифратора, выход 25 элемента И 11 - вход записи блока 1 памяти, выход 26 элемента И 13 - синхронизирующий вход блока 1 памяти, сигнальный выход 27, первый 28 и второй 29 синхронизирующие входы устройства.

Блок 1 памяти (фиг.2) содержит ре гистры 30.1-30.N, коммутаторы 31.1- 31.N, первую группу 32.1-32.N и вторую группу 33.2-33.N элементов ИЛИ, группу элементов И 34.1-34.N.

Устройство работает следующим образом.

16, днух элементов НИИ 7, 8. Устройство приоритетного обслуживания ставит все поступающие заявки в одну общую очередь, реализованную в блоке памяти, причем место заявки в этой очереди и, следовательно, время ожидания определяются приоритетом данной заявки. 2 ил.

10

15

20

5

30

35

40

В начальном состоянии блок 1 памяти, счетчик 2, регистр 3 обнулены. Цепи установки условно не показаны.

Код заявки, содержащий и код приоритета данной заявки, поступает на вход 17. С входа 17 код заявки поступает на D-входы регистра 3, а также код заявки через элемент ИЛИ 7 открывает элемент И 9. Очередной импульс с входа 28 проходит на С-вход регистра 3, и задним фронтом записывает код заявки в регистр 3. С выхода 21 регистра 3 код заявки поступает на входы элемента ИЛИ 8, а код приоритета заявки на В-вход схемы 5 сравнения, на А-вход которой поступает код приоритета заявки, хранящейся по нулевому адресу в блоке 1 памяти. Так как в блоке 1 памяти не хранится ни одной заявки, то очевидно, что на выходе Меньше 23 элемента 5 сравнения находится единичный сигнал. Этот сигнал открывает элемент И 13. Очередной сигнал с входа 28 проходит через открытые элементы И .10, 13 и поступает в блок 1 памяти, где записывает код заявки в регистр 30.1. Кроме того, этот сигнал проходит через элемент 14 задержки и сбрасывает регистр 3 и счетчик 2.

Очередная заявка, поступившая на вход 17, по описанному алгоритму, записывается в регистр 3, а код ее приоритета поступает на В-вход схемы 5 сравнения. Поскольку код приоритета заявки, хранящейся в блоке 1 памяти, по нулевому адресу не нулевой, то возможны два варианта.

1. Результат сравнения кода приоритета заявки из блока 1 памяти с кодом приоритета вновь пришедший за

3П

явки - меньше. Как в описанном случае, очередной сигнал с входа 28 проходит через открытые элементы И 10, 13 в блок 1 памяти, где проходит синхронизация записи вновь при- шедшей заявки в регистр 30.1 и перезапись заявки, пришедшей ранее, из регистра 30.1 в регистр 30.2, так как код ее приоритета меньше кода приоритета вновь пришедшей заявки.

2. Результат сравнения двух кодов приоритетов - больше или равно. Это означает, что код приоритета вновь пришедшей заявки меньше кода приоритета имеющейся в блоке 1 памяти заявки. Тогда на выходе 22 схемы 5 сравнения появляется единичный сигнал, который открывает элемент И 12. Очередной сигнал с входа 28 через элементы И 10 и 12 поступает на суммирующий вход счетчика 2. В результате на первом выходе 24.2 дешифратора 6 появляется единичный сигнал. Но так как в регистре 30.2 еще нет заявки, то на А-вход схемы 5 сравнения поступает нулевой код. Поэтому очередной импульс с входа 28 проходит на выход элемента И 13 и поступает в блок 1 памяти, где происходит запись кода заявки в регистр 30.2, а пройдя через элемент 14 задержки, установит регистр 3 и счетчик 2 в нулевое состояние, подготавливая тем самьм устройство к приему очередной заявки.

Поступающие в последующие моменты времени заявки обслуживаются аналогично описанному алгоритму.

Поступление кода заявки на вход 1 синхронизируется импульсами с входа 29. Поэтому код заявки поступает в промежутке между импульсами по входу 29, но обязательно во время импульса по входу 28, так как он синхронизирует запись кода заявки в уст ройстве.

Появление сигнала на входе 18 синхронизируется импульсами с входа 28 Поэтому он поступает в промежутке между импульсами на входе 28, но обязательно во время импульса по входу 29. Данный сигнал обозначает, что заявка, хранящаяся в регистре 30,1, взята на обслуживание обслуживающим органом, а следовательно, необходимо произвести сдвиг информации в блоке 1 памяти. Поэтому сигнал с входа 29 через открытьш элемент И 11 поступает в блок 1 памяти, где

0

5

0

5

8

5

0 5

0 5

0

344

и производит сдвиг информации. Кроме того, если сдвиг произошел в процессе поиска места для очередной заявки, то очевидно, что у заявок, хранящихся в блоке 1, изменяются адреса, поэтому изменяется адрес и в счетчике 2. .Сигнал через элемент И 16 поступает на вычитающий вход счетчика 2. В этом случае исключается возможность пропуска одного из кодов приоритетов для сравнения на элементе 5 сравнения.

Чтобы исключить возможность прихода очередной заявки на вход 17 в то время, когда еще не найдено место для ранее пришедшей заявки, сигналы синхронизации поступления заявок с входа 29 могут пройти на выход 27 только когда в регистре 3 присутствует нулевая информация.

Блок 1 памяти (фиг.2) работает следующим образом.

Запись кода заявки, поступающей на вход 21, производится в соответствии с сигналами с выхода дешифратора 6. Очередная заявка должна быть записана в тот регистр, в котором код приоритета меньше кода вновь поступившей заявки, о чем указывает сигнал на соответствующем выходе 24.1 дешифратора 6. Этот сигнал открывает соответствующий информационный вход коммутатора 31.1. Далее этот сигнал поступает на управляющие входы коммутаторов 31.i-31.N-1, открывая информационные входы соседних регистров. Таким образом, разрещает- ся проход информации с выхода регистра 30.1 на вход регистра 30. (1+1), с выхода регистра 30.(1 + 1) на вход регистра 30.(1+2) и т.д. В результате производится сдвиг вверх информации и освобождается регистр 30.1 для вновь пришедшей заявки.

Перезапись информации осуществляется импульсом с входа 26, который через открытые элементы И 34.1- 34.N и элементы ИЛИ 32.1-32.N проходит на С-входь1 регистров 30.1-30.N.

Если необходимо произвести сдвиг информации вниз, когда очередная заявка из регистра 30.1 взята на обслуживание, то поступает импульс по входу 25, который проходит на С-входы всех регистров 30.1-30.N. В этом случае на всех входах 24.1-24.N присутствуют нулевые сигналы, так

как сигнал с входа 18 боту дешифратора 6.

Формула и зоб

запрещает рар е т е н и

Устройство приоритетного обслуживания, содЕ ржащее блок памяти и дешифратор, причем выходы дешифратора подключены к адресным входам записи блока памяти, отличающееся тем, что, с целью расширения области применения за счет организации общей очереди заявок, в устройство введены счетчик, регистр коммутатор, схема сравнения, первый и второй элементы ИЛИ, с первого по седьмой элементы И и элемент задержки, причем группа информационных входов устройства подключер а к группе информационных входов регистра и к входам первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, выход которого подключен к входу записи регистра, первая группа выходов которого подключена к группе информационных входов блока памяти и входам второго элемента ИЛИ, вторая группа выходов регистра соединена с первой группой входов схемы с:равнения, выход второго элемента ИЛИ подключен к первому входу второго элемента И, выход которого подсоединен к первым входам третьего и четвертого элементов И, выход третьего элемента И подсоедине

к суммирующему входу.счетчика, группа 35 татора, группа вькодов дешифратора выходов которого подключена к группе соединена с группой адресных входов информационных входов дешифратора, блока памяти.

5

0

5

0

выход четвертого элемента И подключен к входу синхронизации блока памяти и через элемент задержки - к установочным входам регистра и счетчика, первый синхронизирующий вход устройства подключен к вторым входам первого и второго элементов И, второй синхронизирующий, вход устройства подключен к первым входам пятого и шестого элементов И, ответный йход устройства подключен к второму входу пятого элемента И и к стробирующему входу дешифратора, группа выходов которого соединена с группой управляющих входов коммутатора, группа выходов которого подключена к второй группе входов схемы сравнения, выходы Больше или равно и Меньше которой подключены к вторьт входам третьего и четвертого элементов И соответственно, выход пятого элемента И подключен к входу записи блока памяти и к первому входу седьмого элемента И, выход которого подключен к вычитающему входу счетчика, выход второго элемента ИЛИ подключен к вторым входам седьмого и шестого элементов И, выход шестого элемента И является сигнальным выходом устройства, группа информационных выходов блока памяти является группой выходов устройства, а группа выходов кодов приоритетов блока памяти соединена с группой информационньпс входов комму2S о

JJ./;

J«./7

25 о

7

.я

Л/7-/

J.n-j

Ш:

Т

3

Г.д

J/TTT

f«.-r

33.2

D

311.2

г.2 о-

J«.r

го.п

J

а

W

ТТЛt

г

за.п-т

h

n-j

Ik

LE

I1

T

±

HE:

Зогг

/.

2tt,J

ir

I 32} I

X

ue.2

Составитель М.Сорочан Редактор Н.Слободяник Техред А.Кравчук Корректор М.Демчик

Заказ 4803/49Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3OJ

/5

T

J гол

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритетного обслуживания | 1986 |

|

SU1531095A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для моделирования вычислительной системы | 1990 |

|

SU1786492A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Многопроцессорная вычислительная система | 1990 |

|

SU1798799A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| УСТРОЙСТВО ПРИОРИТЕТНОГО ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2182354C2 |

| Устройство для вероятностного моделирования работы транспортных систем | 1988 |

|

SU1612313A1 |

| Устройство приоритета | 1990 |

|

SU1829033A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации приоритетного обслуживания и приоритетных 9 9 М 7 (Л со 4 00 00 со Nj Фи I

| Балашов Е.П., Пузанков Д.В | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| М.: Радио и связь, 1981, с | |||

| Соломорезка | 1918 |

|

SU157A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство приоритетного обслуживания | 1983 |

|

SU1141410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-05—Подача