Изобретение относится к радиотехнике и может быть использовано для фильтрации данных, заданных цифровьгм кодом.

Цель изобретения - повьшение быстродействия ,

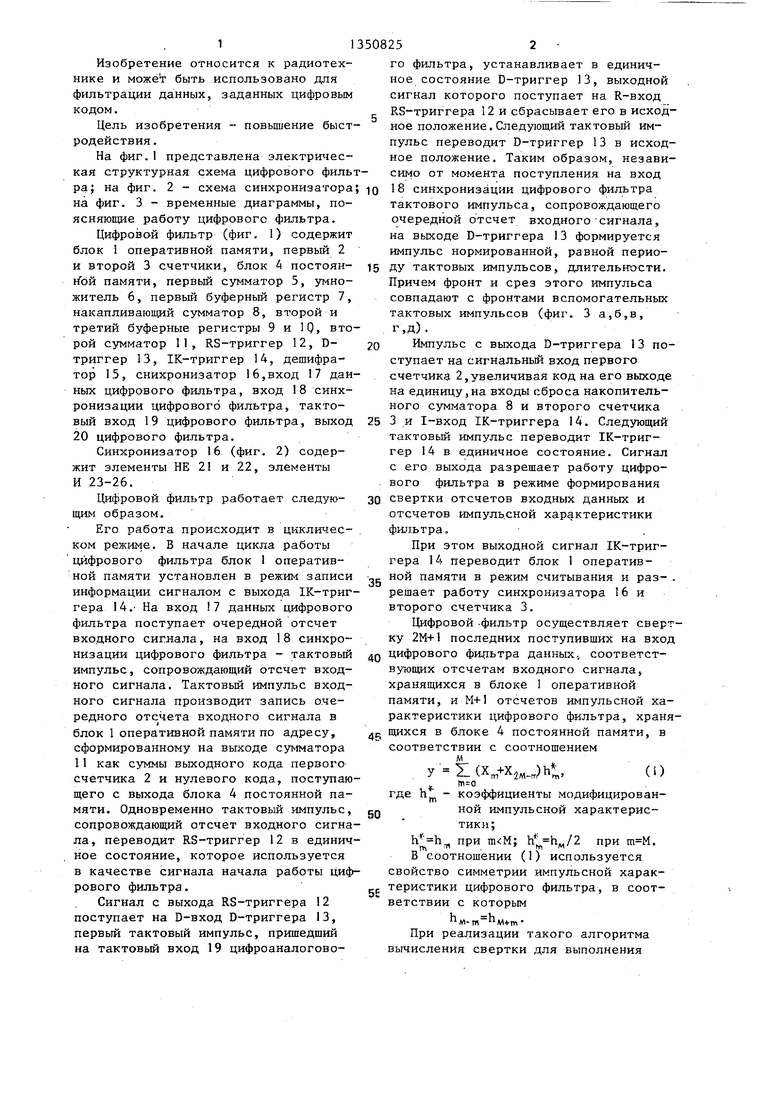

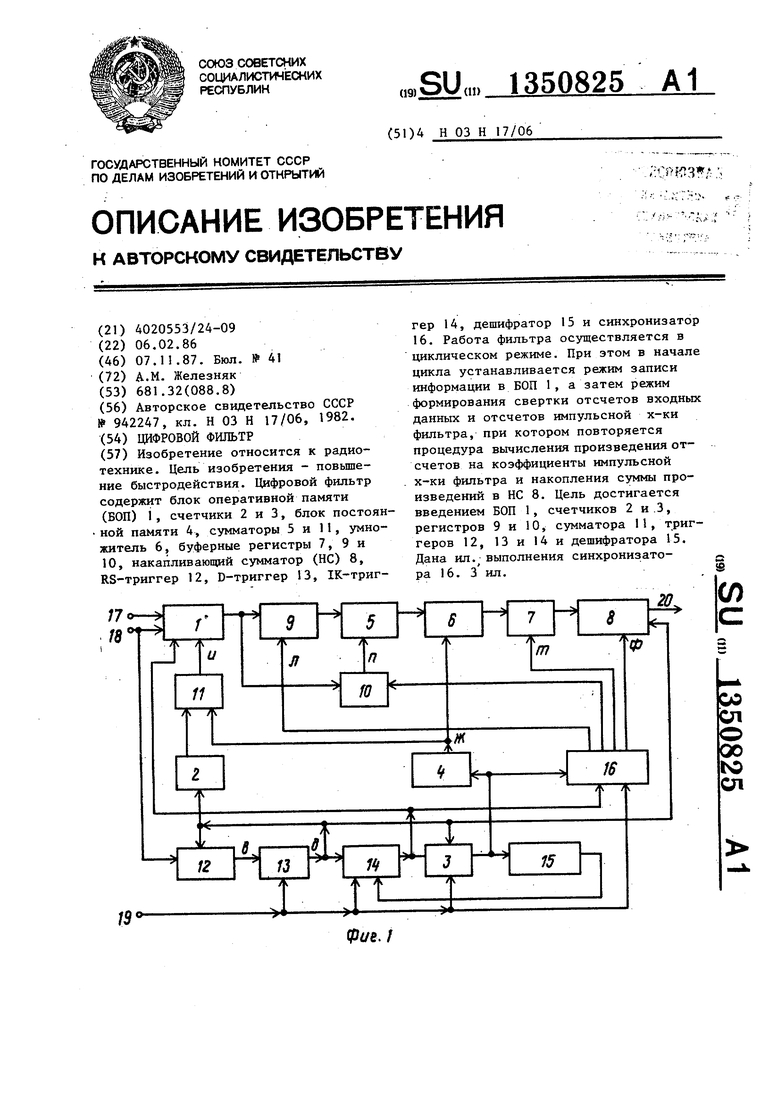

На фиг.1 представлена электрическая структурная схема цифрового фильт15

20

25

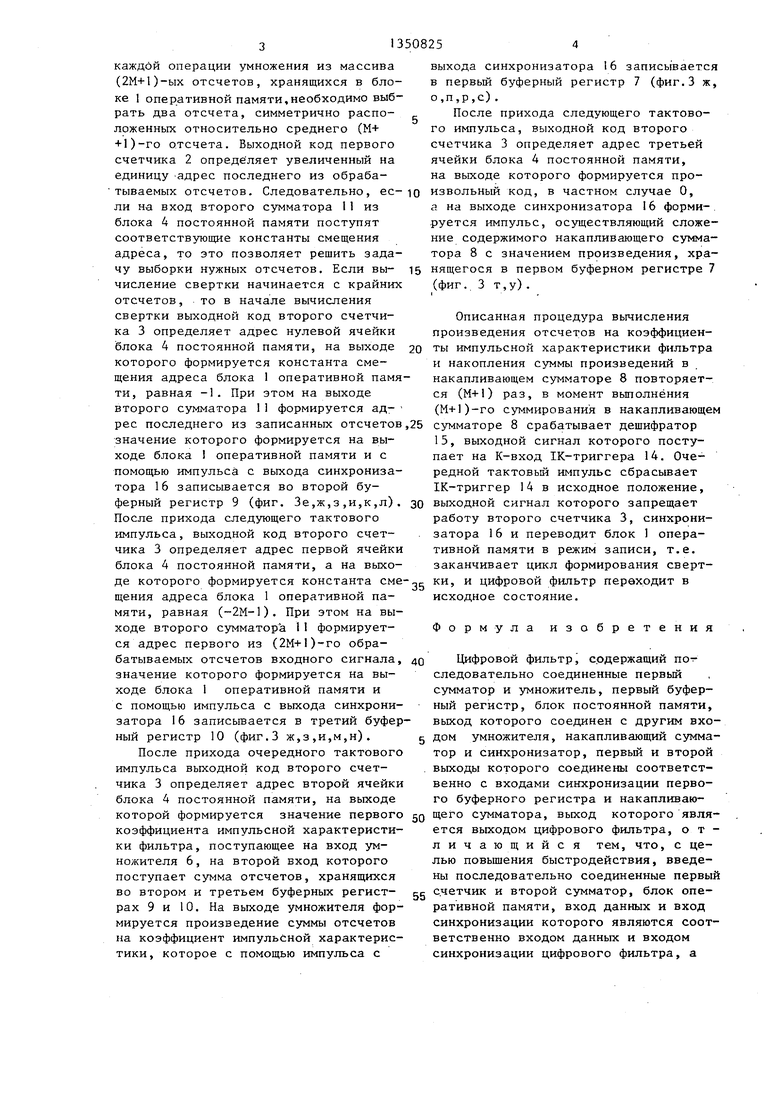

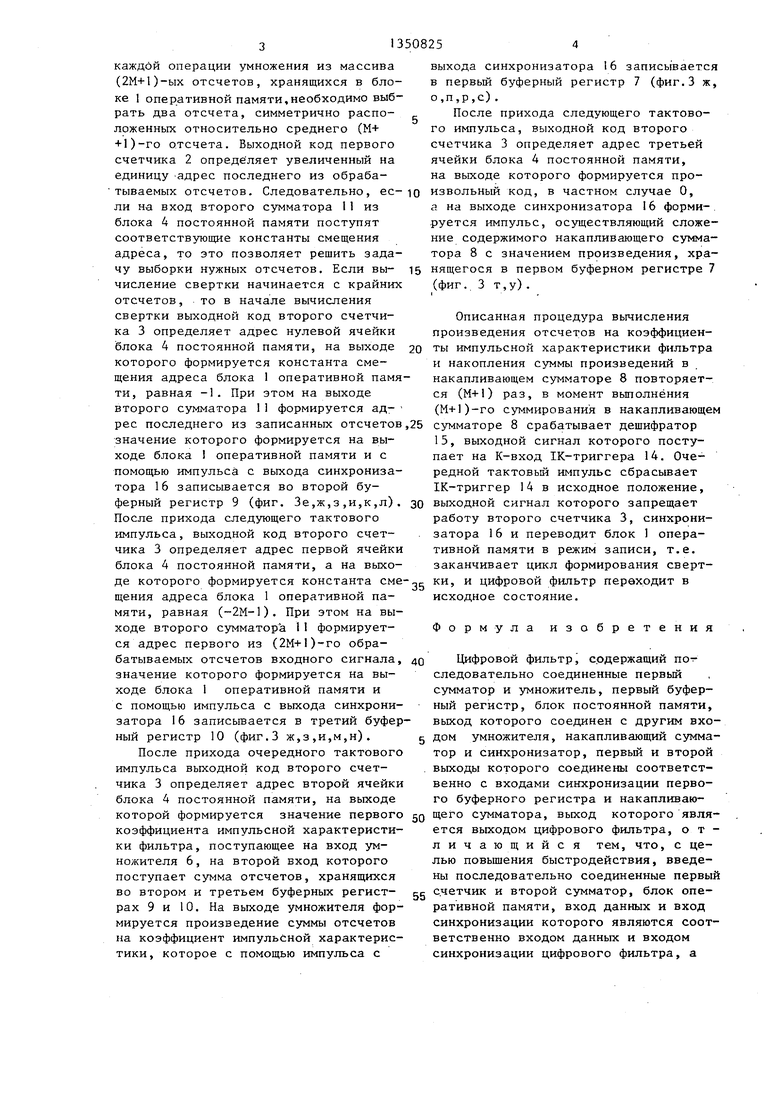

ра; на фиг. 2 - схема синхронизатора; ю 58 синхронизации цифрового фильтра на фиг. 3 - временные диаграммы, поясняющие работу цифрового фильтра.

Цифровой фильтр (фиг. 1) содержит блок 1 оперативной памяти, первый 2 и второй 3 счетчики, блок 4 постоян- рйй памяти, первый сумматор 5, умножитель 6, первый буферный регистр 7, накапливающий сумматор 8, второй и третий буферные регистры 9 и 1Q, второй сумматор II, RS-триггер 12, D- триггер 13, 1К-триггер 14, дешифратор 15, снихронизатор 16,вход 17 данных цифрового фильтра, вход 18 синхронизации цифрового фильтра, тактовый вход 19 цифрового фильтра, выход 20 цифрового фильтра.

Синхронизатор 16 (фиг. 2) содержит элементы НЕ 21 и 22, элементы И 23-26.

Цифровой фильтр работает следующим образом.

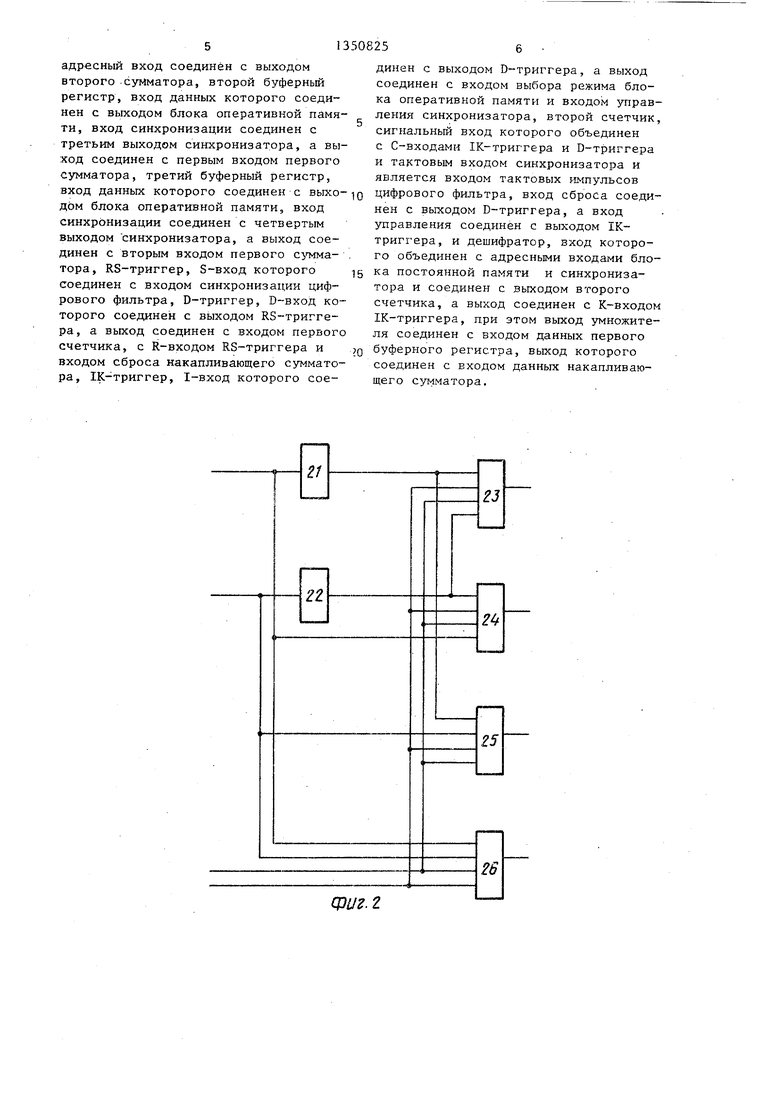

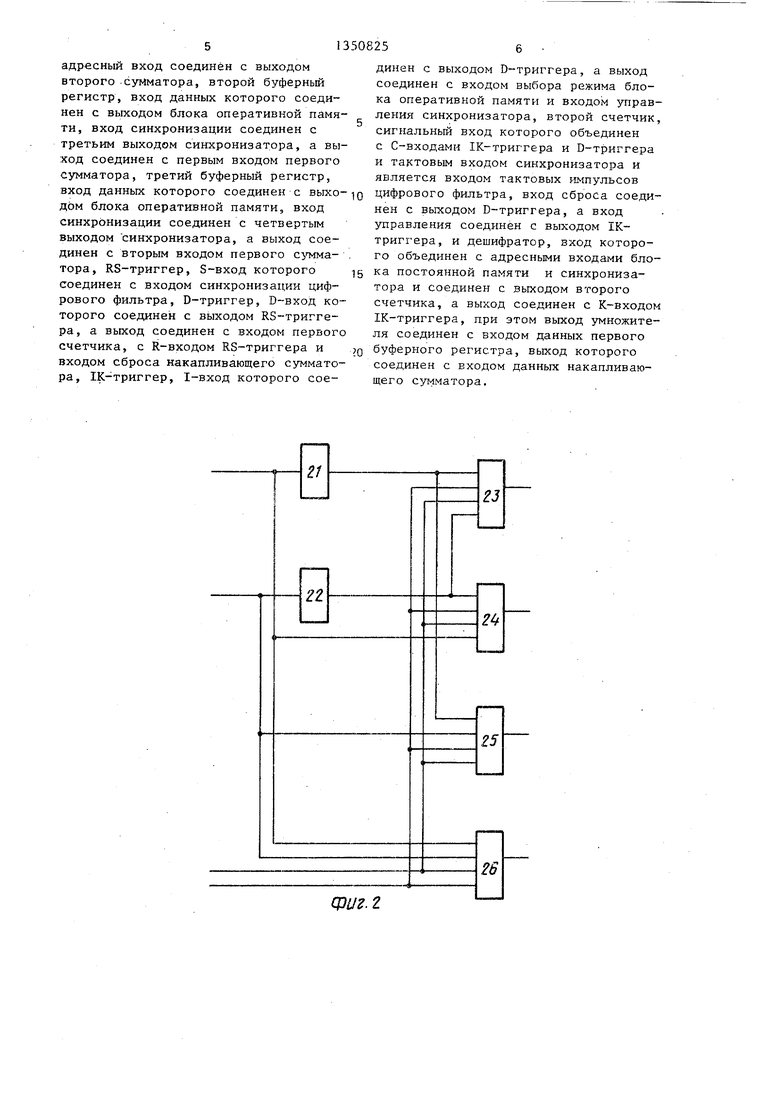

Его работа происходит в циклическом режиме. В начале цикла работы цифрового фильтра блок 1 оператив- ной памяти установлен в режим записи информации сигналом с выхода 1К-триг- гера 14. На вход 7 данных цифрового фильтра поступает очередной отсчет входного сигнала, на вход 18 синхронизации цифрового фильтра - тактовый импульс, сопровождающий отсчет входного сигнала. Тактовьш импульс входного сигнала производит запись очередного отсчета входного сигнала в блок 1 оперативной памяти по адресу, сформированному на выходе сумматора 11 как суммы выходного кода первого счетчика 2 и нулевого кода, поступающего с выхода блока 4 постоянной памяти. Одновременно тактовый импульс, сопровождающий отсчет входного сигнатактового импульса, сопровождающего очередной отсчет входного-сигнала, на выходе D-триггера 13 формируется импульс нормированной, равной перио ду тактовых импульсов, длительности Причем фронт и срез этого импульса совпадают с фронтами вспомогательны тактовых импульсов (фиг. 3 а,б,в, г,д) .

Импульс с выхода D-триггера 13 п ступает на сигнальньй вход первого счетчика 2,увеличивая кОд на его выхо на единицу,на входы сброса накопитель ного сумматора 8 и второго счетчика 3 и 1-вход 1К-триггера 14. Следующи тактовый импульс переводит 1К-триг- гер 14 в единичное состояние. Сигна с его выхода разрешает работу цифро вого фильтра в режиме формирования свертки отсчетов входных данных и отсчетов импульсной характеристики фильтра.

При этом выходной сигнал 1К-триг гера 14 переводит блок 1 оперативной памяти в режим считывания и раз решает работу синхронизатора 16 и второго счетчика 3.

Цифровой .фильтр осуществляет све ку 2М+1 последних поступивших на вх Q цифрового фщ1ьтра данных, соответст вующих отсчетам входного сигнала, хранящихся в блоке 1 оперативной памяти, и М+1 отсчетов импульсной х рактеристики цифрового фильтра, хра С5 щихся в блоке 4 постоянной памяти, соответствии с соотношением

. У :(.,)h, (1

30

35

fn-o

i.

где h - коэффициенты модифицирован

50

ной импульсной характеристики;h при при .

ла, переводит RS-триггер 12 в единичное состояние, которое используется в качестве сигнала начала работы цифрового фильтра.

Сигнал с выхода RS-триггера 12 поступает на D-вход В-триггера 13, первый тактовый импульс, пришедший на тактовый вход 19 цифроаналогового фильтра, устанавливает в единичное состояние D-триггер 13, выходной сигнал которого поступает на R-вход RS-триггера 12 и сбрасывает его в исходное положение. Следующий тактовый импульс переводит D-триггер 13 в исходное положение. Таким образом, независимо от момента поступления на вход

58 синхронизации цифрового фильтра

тактового импульса, сопровождающего очередной отсчет входного-сигнала, на выходе D-триггера 13 формируется импульс нормированной, равной периоду тактовых импульсов, длительности. Причем фронт и срез этого импульса совпадают с фронтами вспомогательных тактовых импульсов (фиг. 3 а,б,в, г,д) .

Импульс с выхода D-триггера 13 поступает на сигнальньй вход первого счетчика 2,увеличивая кОд на его выходе на единицу,на входы сброса накопительного сумматора 8 и второго счетчика 3 и 1-вход 1К-триггера 14. Следующий тактовый импульс переводит 1К-триг- гер 14 в единичное состояние. Сигнал с его выхода разрешает работу цифрового фильтра в режиме формирования свертки отсчетов входных данных и отсчетов импульсной характеристики фильтра.

При этом выходной сигнал 1К-триг- гера 14 переводит блок 1 оперативной памяти в режим считывания и раз- . решает работу синхронизатора 16 и второго счетчика 3.

Цифровой .фильтр осуществляет свертку 2М+1 последних поступивших на вход цифрового фщ1ьтра данных, соответствующих отсчетам входного сигнала, хранящихся в блоке 1 оперативной памяти, и М+1 отсчетов импульсной характеристики цифрового фильтра, храня- щихся в блоке 4 постоянной памяти, в соответствии с соотношением

. У :(.,)h, (1)

fn-o

i.

где h - коэффициенты модифицирован0

ной импульсной характеристики;h при при .

h

п В соотношении (1) используется

5Е

свойство симметрии импульсной характеристики цифрового фильтра, в соответствии с которым

При реализации такого алгоритма вычисления свертки для выполнения

каждой операции умножения из массива (2М+1)-ых отсчетов, хранящихся в блоке 1 оперативной памяти,необходимо выбрать два отсчета, симметрично расположенных относительно среднего (М+ +1)-го отсчета. Выходной код первого счетчика 2 определяет увеличенный на единицу адрес последнего из обрабатываемых отсчетов. Следовательно, ее- ю извольный код, в частном случае О,

ли на вход второго сумматора I1 из блока 4 постоянной памяти поступят соответствующие константы смещения адреса, то это позволяет решить задачу выборки нужных отсчетов. Если вычисление свертки начинается с крайних отсчетов, то в начале вычисления свертки выходной код второго счетчика 3 определяет адрес нулевой ячейки блока 4 постоянной памяти, на выходе которого формируется константа смещения адреса блока 1 оперативной памяти, равная -1. При этом на выходе

Описанная процедура вычисления произведения отсчетов на коэффициен- 20 ты импульсной характеристики фильтра и накопления суммы произведений в накапливающем сумматоре 8 повторяется (М+1) раз, в момент вьтолнёния (И+1)-го суммирования в накапливающем

второго сумматора 11 формируется ад- рее последнего из записанных отсчетов,25 сумматоре 8 срабатывает дешифратор значение которого формируется на вы- 15, выходной сигнал которого поступает на К-вход 1К-триггера 14. Очередной тактовый импульс сбрасывает 1К-триггер 14 в исходное положение, выходной сигнал которого запрещает работу второго счетчика 3, синхронизатора 16 и переводит блок 1 операходе блока оперативной памяти и с помощью импульса с выхода синхронизатора 16 записывается во второй буферный регистр 9 (фиг. Зе,ж,з,и,к,л). После прихода следующего тактового импульса, выходной код второго счетчика 3 определяет адрес первой ячейки блока 4 постоянной памяти, а на выхо30

тивной памяти в режим записи, т.е. заканчивает цикл формирования свертде которого формируется константа CMe-,,g ки, и цифровой фильтр переходит в щения адреса блока 1 оперативной па- исходное состояние, мяти, равная (-2М-1). При этом на выходе второго сумматора 1I формируется адрес первого из (2М+)- ГО обрабатываемых отсчетов входного сигнала, значение которого формируется на выходе блока 1 оперативной памяти и с помощью импульса с выхода синхронизатора 16 записывается в третий буферный регистр 10 (фиг.З ж,з,и,м,н).

После прихода очередного тактового импульса выходной код второго счетчика 3 определяет адрес второй ячейки блока 4 постоянной памяти, на выходе

Формула изобретени

40 Цифровой фильтр, содержащий последовательно соединенные первый сумматор и умножитель, первый буфе ный регистр, блок постоянной памят выход которого соединен с другим в 5 дом умножителя, накапливающий сум тор и синхронизатор, первый и втор . выходы которого соединены соответс венно с входами синхронизации перв го буферного регистра и накапливаю

которой формируется значение первого 50 Щего сумматора, вькод которого явля- коэффициента импульсной характеристи- ется выходом цифрового фильтра, о т ки фильтра, поступающее на вход умножителя 6, на второй вход которого поступает сумма отсчетов, хранящихся во втором и третьем буферных регистрах 9 и 10. На выходе умножителя формируется произведение суммы отсчетов на коэффициент импульсной характеристики, которое с помощью импульса с

выхода синхронизатора 16 записывается в первый буферный регистр 7 (фиг.З ж, о,п,р,с).

После прихода следующего тактового импульса, выходной код второго счетчика 3 определяет адрес третьей ячейки блока 4 постоянной памяти, на выходе которого формируется проа на выходе синхронизатора 16 формируется импульс, осуществляющий сложение содержимого накапливающего сумматора 8 с значением произведения, хра- нящегося в первом буферном регистре 7 (фиг. 3 т,у).

Описанная процедура вычисления произведения отсчетов на коэффициен- ты импульсной характеристики фильтра и накопления суммы произведений в накапливающем сумматоре 8 повторяется (М+1) раз, в момент вьтолнёния (И+1)-го суммирования в накапливающем

сумматоре 8 срабатывает дешифратор 15, выходной сигнал которого поступает на К-вход 1К-триггера 14. Очередной тактовый импульс сбрасывает 1К-триггер 14 в исходное положение, выходной сигнал которого запрещает работу второго счетчика 3, синхронизатора 16 и переводит блок 1 опера25

30

тивной памяти в режим записи, т.е. заканчивает цикл формирования свертки, и цифровой фильтр переходит в исходное состояние,

ормула изобретения

Цифровой фильтр, содержащий последовательно соединенные первый сумматор и умножитель, первый буферный регистр, блок постоянной памяти, выход которого соединен с другим вхо- дом умножителя, накапливающий сумматор и синхронизатор, первый и второй выходы которого соединены соответственно с входами синхронизации первого буферного регистра и накапливаю55

личающийся тем, что, с целью повышения быстродействия, введены последовательно соединенные первый счетчик и второй сумматор, блок оперативной памяти, вход данных и вход синхронизации которого являются соответственно входом данных и входом синхронизации цифрового фильтра, а

адресный вход соединён с выходом второго сумматора, второй буферный регистр, вход данных которого соединен с выходом блока оперативной памяти, вход синхронизации соединен с третьим выходом синхронизатора, а выход соединен с первым входом первого сумматора, третий буферный регистр, вход данных которого соединен с выходом блока оперативной памяти, вход синхронизации соединен с четвертым выходом синхронизатора, а выход соединен с вторым входом первого сумматора RS-триггер, S-вход которого соединен с входом синхронизации цифрового фильтра, D-триггер, D-вход которого соединен с выходом RS-тригге- ра, а выход соединен с входом первого счетчика, с R-входом КЗ-триггера и входом сброса накапливающего сумматора, 1К-триггер, 1-вход которого соефиг. 2

динен с выходом D-триггера, а выход соединен с входом выбора режима блока оперативной памяти и входом управления синхронизатора, второй счетчик, сигнальный вход которого объединен с С-входами 1К-триггера и D-триггера и тактовым входом синхронизатора и является входом тактовых импульсов

цифрового фильтра, вход сброса соединен с выходом D-триггера, а вход управления соединен с выходом IK- триггера, и дешифратор, вход которого объединен с адресными входами блока постоянной памяти и синхронизатора и соединен с выходом второго счетчика, а выход соединен с К-входом 1К-триггера, при этом выход умножителя соединен с входом данных первого

буферного регистра, выход которого соединен с входом данных накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Цифровой согласованный фильтр | 1988 |

|

SU1596267A1 |

| Устройство для определения технического состояния механизмов циклического действия | 1989 |

|

SU1686334A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьше- ние быстродействия. Цифровой фильтр содержит блок оперативной памяти (БОП) i, счетчики 2 и 3, блок постоянной памяти 4, сумматоры 5 и 11, умножитель 6, буферные регистры 7, 9 и 10, накапливающий сумматор (НС) 8, RS-триггер 12, D-триггер 13, 1К-триг(. / гер 14, дешифратор 15 и синхронизатор 16. Работа фильтра осуществляется в циклическом режиме. При этом в начале цикла устанавливается режим записи информации в БОП 1, а затем режим формирования свертки отсчетов входных данных и отсчетов импульсной х-ки фильтра, при котором повторяется процедура вычисления произведения отсчетов на коэффициенты импульсной х-ки фильтра и накопления суммы произведений в НС 8. Цель достигается введением БОП 1, счетчиков 2 и .3, регистров 9 и 10, сумматора 11, триггеров 12, 13 и 14 и дешифратора 15. Дана ил. выполнения синхронизатора 16. 3 ил. (Л с

| Цифровой нерекурсивный фильтр | 1980 |

|

SU942247A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-07—Публикация

1986-02-06—Подача