4 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Многоканальный цифровой интерполирующий фильтр для частотного уплотнения каналов | 1987 |

|

SU1525716A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Цифровой фильтр | 1986 |

|

SU1350825A1 |

| Цифровой фильтр | 1990 |

|

SU1780089A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано в устройствах для цифровой обработки сигналов, в частности для повышения точности представления сигналов на выходе цифровой линии связи. Цель изобретения - повьшение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входят блок памяти 1, накапливающий сумматор 2, умножитель 3, накапливающий сумматор 4, блок постоянной памяти 5, очетчик 6 канала, блок 7 злементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, сумматор 8, синхронизатор 9, элемент ИЛИ 10, счетчик выборки 11, счетчики 12, 13. 2 ид. с 9 /7 О) С

./

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано в устройствах для цифровой обработки сигналов, в част- ности. для повышения точности представления сигналов на выходе цифровой линии связи.

Целью изобретения является повышение быстродействия (за счет умень- шения операций умножения и сложения).

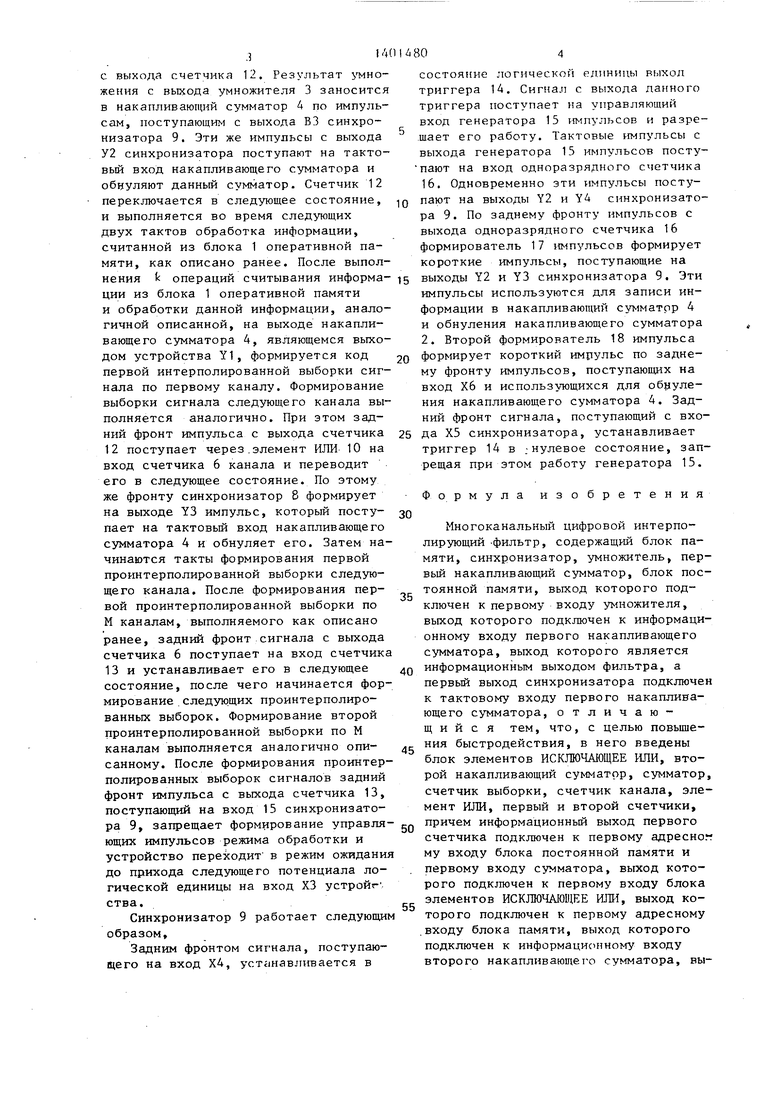

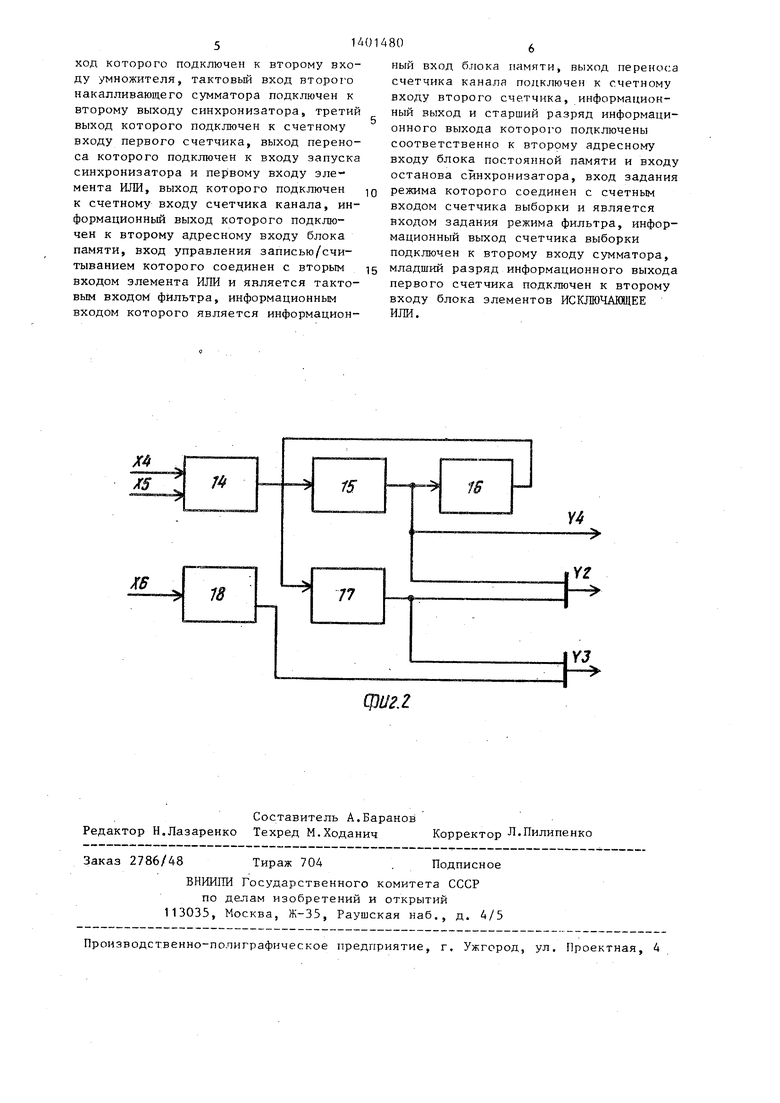

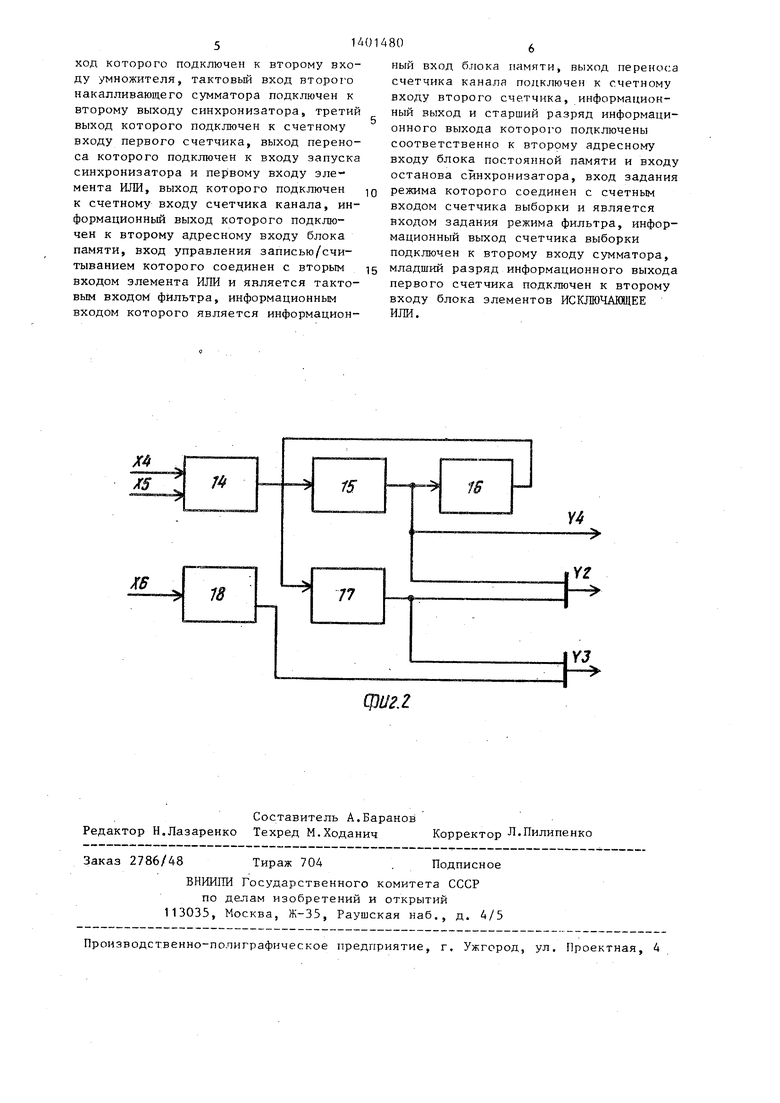

На фиг.1 приведена структурная схема многоканального цифрового ин терполирующего фильтра; на фиг.2 - функциональная схема синхронизатора.

Многоканальный цифровой интерполирующий фильтр содержит блок (оперативной памяти) 1, накапливающий сумматор 2, умножитель 3, накапливающий сумматор 4, блок 5 постоянной памяти, счетчик 6 канала, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7,(адресный) сумматор 8, синхронизатор 9, элемент ИЛИ 10, счетчик 11 выборки, счетчики 12 и 13.

Синхронизатор содержит триггер 14, генератор 15 синхроимпульсов, одноразрядный счетчик 16, первый 17 и второй 18 формирователи импульсов.

Повышение част оты дискретизации сигнала предполагает формирование последовательности из L-1 отсчетов с нулевой амплитудой в интервале между выборками исходной последовательности, которая затем пропускается через фильтр нижних частот с линейной фазовой характеристикой. Исключая операции умножения на нулевые выборки, цифровой фильтр работает в соответствии с выражением

y.j(n)Lh(Li-H)X(n-i), при

-о

сигнала;

h(L.+I) - коэффициенты импульсной характеристики фильтров; у.,(п) - проинтерполированные выборки сигнала.

С учетом симметрии импульсной характеристики фильтра формирование проинтерполированных выборок в устройстве производится в соответствии с выражением К/г

У7(п) Г h(L; +k)rx(n-i)+X(k-n+1) l L- J

Для формирования одной проинтерпо лированной выборки сигнала необходим

-

5

0

5 0

0

5

0

5

выполнить V/2 операций умножения и k операций сложения.

Многоканальный дифровоГ) интерполи- РУЮ0ШЙ фильтр работает следующим образом.

При появлении высокого потенциала на входе ХЗ. устройства производится запись входных выборок сигналов по М каналам, в блок 1 оперативной памяти. На выход адресного сумматора 8 передается при этом код с выхода счетчика 11 выборки. На вход устройства Х2 nor ступают в режиме записи импульсы сопровождения информации по каждому каналу. После занесения в блок 1 оперативной памяти выборки сигнала по одному каналу, импульс сопровождения переключает счетчик каналов в следзто- щее состояние и по очередному импулы су сопровождения производится запись выборки сигнала следующего канала. После занесения выборок сигнала по М каналам высокий уровень с входа ХЗ снимается, при этом счетчик 11 выборки переключается в следующее состояние и синхрон изатор начинает формировать управляющие сигналы для выполнения режима обработки.

Режим обработки в устройстве выполняется следующим образом.

С третьего выхода Y4 синхронизатора 9 на вход счетчика 12 поступают тактовые импульсы, на выходе данного счетчика последовательно формируются коды, которые поступают на вход адресного сумматора 8. На другой вход адресного сумматора 8 поступает код с выхода счетчика выборки. На первом такте информация из блока 1 оперативной памяти считывается по адресу, сформированному на выходе адресного сумматора 8, и поступает на вход накапливающего сумматора 2. Во время второго такта на вход управления инверсии кода блока 7 поступает с выхода счетчика 12 уровень логической единицы и информация считывается из оперативной памяти 1 по преобразованному блокам 7 коду ...адреса и суммируется в накапливающем сумматоре 2. :. После двух тактов считывания код с выхода накапливающего сумматора 2 поступает на вход умножителя 3, на другой вход которого с выхода..блока 5 постоянной памяти поступает значение коэффициента импульсной характеристики фильтра. Адрес для считывания импульсной характеристики поступает

,314

с выхода счетчика 12. Результат умножения с выхода умножителя 3 заносится в накапливающий сумматор 4 по импульсам, поступающим с выхода ВЗ синхронизатора 9. Эти же импульсы с выхода У2 синхронизатора поступают на тактовый вход накапливающего сумматора и обнуляют данный сумматор. Счетчик 12 переключается в следующее состояние, и выполняется во время следующих двух тактов обработка информации, считанной из блока 1 оперативной памяти, как описано ранее. После выпол

нения fe операций считывания информа- 15 выходы Y2 и Y3 синхронизатора 9. Эти

ции из блока 1 оперативной памяти и обработки данной информации, аналогичной описанной, на выходе накапливающего сумматора 4, являющемся выходом устройства Y1, формируется код первой интерполированной выборки сигнала по первому каналу. Формирование выборки сигнала следующего канала выполняется аналогично. При зтом задний фронт импульса с выхода счетчика 25 да Х5 синхронизатора, устанавливает

12поступает через.элемент ИЛИ 10 на вход счетчика 6 канала и переводит его в следующее состояние. По этому же фронту синхронизатор 8 формирует на выходе Y3 импульс, который поступает на тактовый вход накапливающего сумматора 4 и обнуляет его. Затем начинаются такты формирования первой проинтерполированной выборки следующего канала. После формирования первой проинтерполированной выборки по

М каналам, выполняемого как описано ранее, задний фронт сигнала с выхода счетчика 6 поступает на вход счетчика

13и устанавливает его в следующее состояние, после чего начинается формирование следующих проинтерполиро- ванных выборок. Формирование второй проинтерполированной выборки по М каналам выполняется аналогично описанному. После формирования проинтер- полированных выборок сигналов задний фронт импульса с выхода счетчика 13, поступающий на вход 15 синхронизатора 9, запрещает формирование управляющих импульсов режима обработки и устройство переходит в режим ожидания до прихода следующего потенциала логической единицы на вход ХЗ устрой - ства.

Синхронизатор 9 работает следующим образом.

Задним фронтом сигнала, поступающего на вход Х4, устг1навливается в

30

35

40

45

50

55

триггер 14 в ;нулевое состояние, зап рещая при этом работу генератора 15.

Формула изобретения

Многоканальный цифровой интерполирующий -фильтр, содержащий блок памяти, синхронизатор, умножитель, пер вый накапливающий сумматор, блок пос тоянной памяти, выход которого подключен к первому входу умножителя, выход которого подключен к информаци онному входу первого накапливающего сумматора, выход которого является информационным выходом фильтра, а первьй выход синхронизатора подключе к тактовому входу первого накапливающего сумматора, отличающийся тем, что, с целью повьщ1е- ния быстродействия, в него введены блок элементов ИСКЛЮЧАЮЩЕЕ РШИ, второй накапливающий сумматор, сумматор счетчик выборки, счетчик канала, эле мент ИЛИ, первый и второй счетчики, причем информационный выход первого счетчика подключен к первому адресно му входу блока постоянной памяти и первому входу сумматора, выход которого подключен к первому входу блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому адресному .входу блока памяти, выход которого подключен к информацж нному входу второго накапливающет о сумматора, вы

состояние логической единицы выход триггера 14. с выхода данного триггера поступает на управляющий вход генератора 15 импульсов и разрешает его работу. Тактовые импульсы с выхода генератора 15 импульсов посту- пают на вход одноразрядного счетчика 16. Одновременно эти импульсы поступают на выходы Y2 и Y4 синхронизатора 9. По заднему фронту импульсов с выхода одноразрядного счетчика 16 формирователь 17 импульсов формирует короткие импульсы, поступающие на

импульсы используются для записи информации в накапливающий сумматор 4 и обнуления накапливающего сумматора 2. Второй формирователь 18 импульса формирует короткий имрульс по заднему фронту импульсов, поступающих на вход Хб и использующихся для обнуления накапливающего сумматора 4. Задний фронт сигнала, поступающий с вхо0

5

0

5

0

5

триггер 14 в ;нулевое состояние, запрещая при этом работу генератора 15.

Формула изобретения

Многоканальный цифровой интерполирующий -фильтр, содержащий блок памяти, синхронизатор, умножитель, первый накапливающий сумматор, блок постоянной памяти, выход которого подключен к первому входу умножителя, выход которого подключен к информационному входу первого накапливающего сумматора, выход которого является информационным выходом фильтра, а первьй выход синхронизатора подключен к тактовому входу первого накапливающего сумматора, отличающийся тем, что, с целью повьщ1е- ния быстродействия, в него введены блок элементов ИСКЛЮЧАЮЩЕЕ РШИ, второй накапливающий сумматор, сумматор, счетчик выборки, счетчик канала, элемент ИЛИ, первый и второй счетчики, причем информационный выход первого счетчика подключен к первому адресное; му входу блока постоянной памяти и первому входу сумматора, выход которого подключен к первому входу блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому адресному .входу блока памяти, выход которого подключен к информацж нному входу второго накапливающет о сумматора, выход которого подключен к второму входу умножителя, тактовый вход второго накапливающего сумматора подключен к второму выходу синхронизатораJ третий выход которого подключен к счетному входу первого счетчика, выход переноса которого подключен к входу запуска синхронизатора и первому входу эле мента ИЛИ, выход которого подключен к счетному входу счетчика канала, информационный выход которого подключен к второму адресному входу блока памяти, вход управления записью/считыванием которого соединен с вторым входом элемента ИЛИ и является тактовым входом фильтра, информационным входом которого является информационный вход блока памяти, выход переноса счетчика канала подключен к счетному входу второго счетчика, информационный выход и старший разряд информационного выхода которого подключены соответственно к второму адресному входу блока постоянной памяти и входу останова синхронизатора, вход задания

режима которого соединен с счетным входом счетчика выборки и является входом задания режима фильтра, информационный выход счетчика выборки подключен к второму входу сумматора,

младший разряд информационного выхода первого счетчика подключен к второму входу блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Фив2

| Цифровой интерполирующий фильтр | 1983 |

|

SU1223345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Флотационная машина | 1981 |

|

SU1093357A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-05—Подача