1 . , ,

Изобретение относится к вычислительной технике и может быть использо .вано в аппаратуре цифровой фильтрации и спектрального анализа.

Известны цифровые нерекурсивные , фильтры, содержащие регистр сдвига, блок памяти коэффициентов, умножители, сумматоры, регистры и осуществляющие выделейие сигналов из помех путем умножения входных выборок сигнала на JQ многоразрядные весовые коэффициенты и суммирования результатов умножения .

Недостатком таких устройств явля- 15 ется то,что при реализации высокой точности обработки необходимо исполь-. зевать многоразрядные весовые коэффициенты, что приводит к большому объему блока памяти коэффициентов, а так-го же Снижает быстродействие устройства при выполнении операций умножения. Для повышения быстродействия приходится применять матричные умножители.

что также ведет к увеличению объема оборудования устройства.

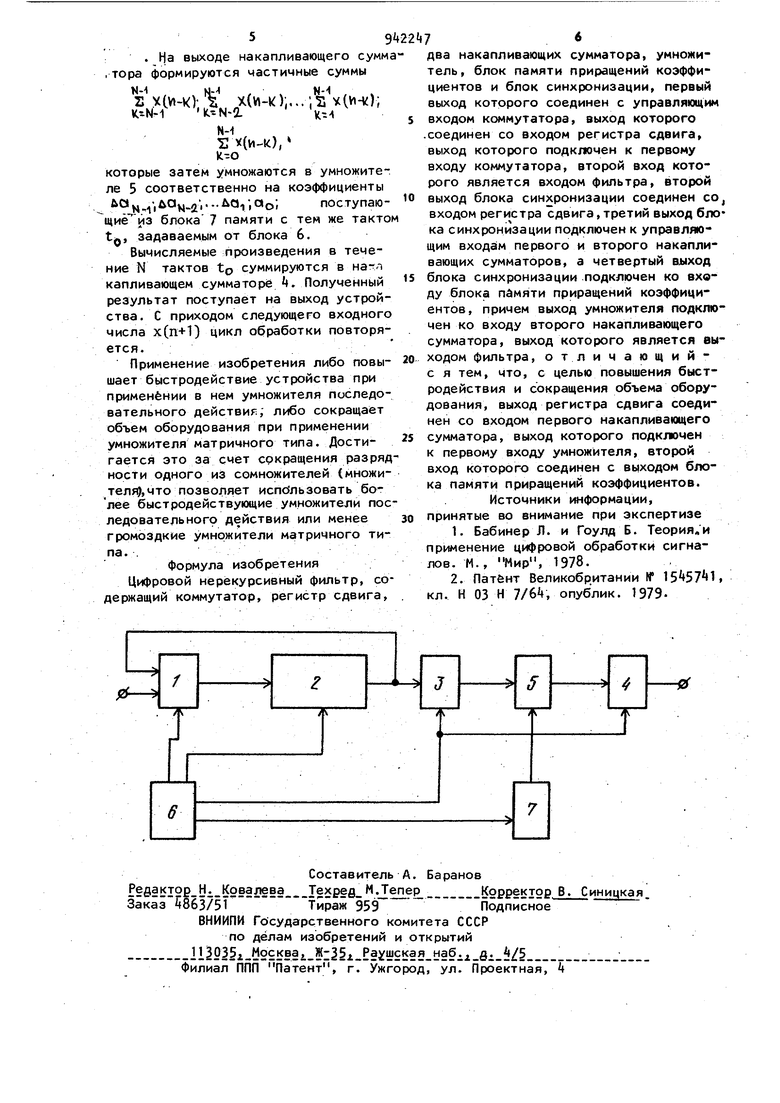

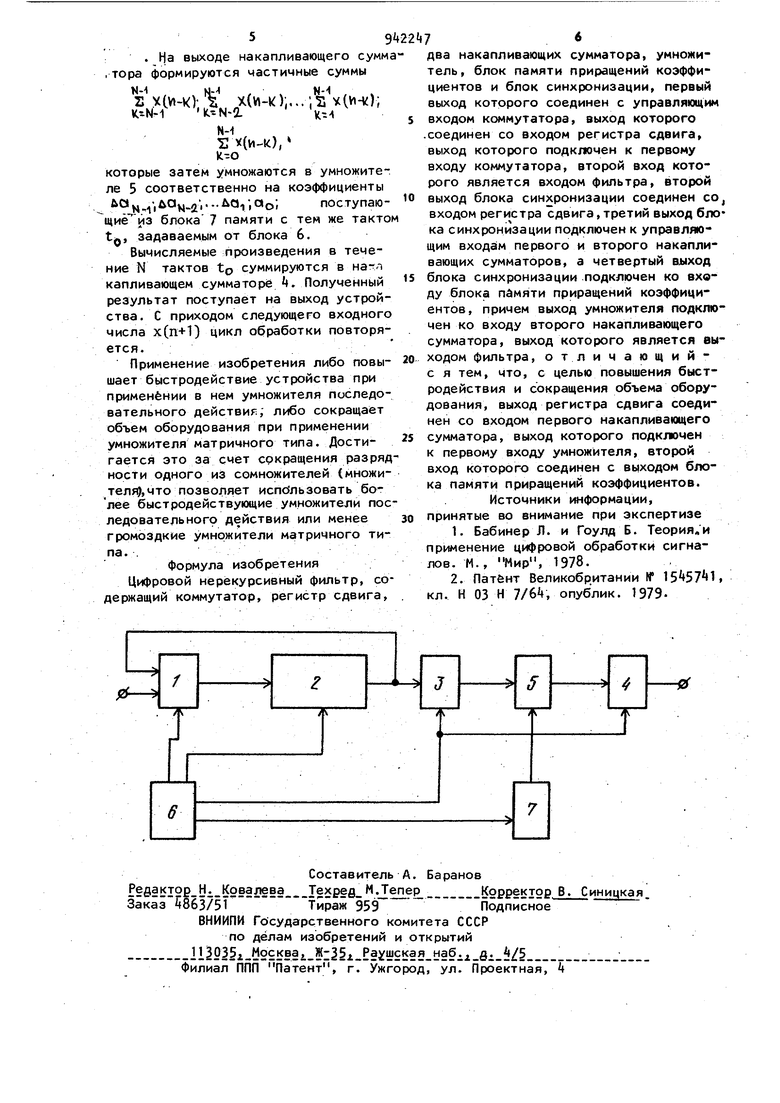

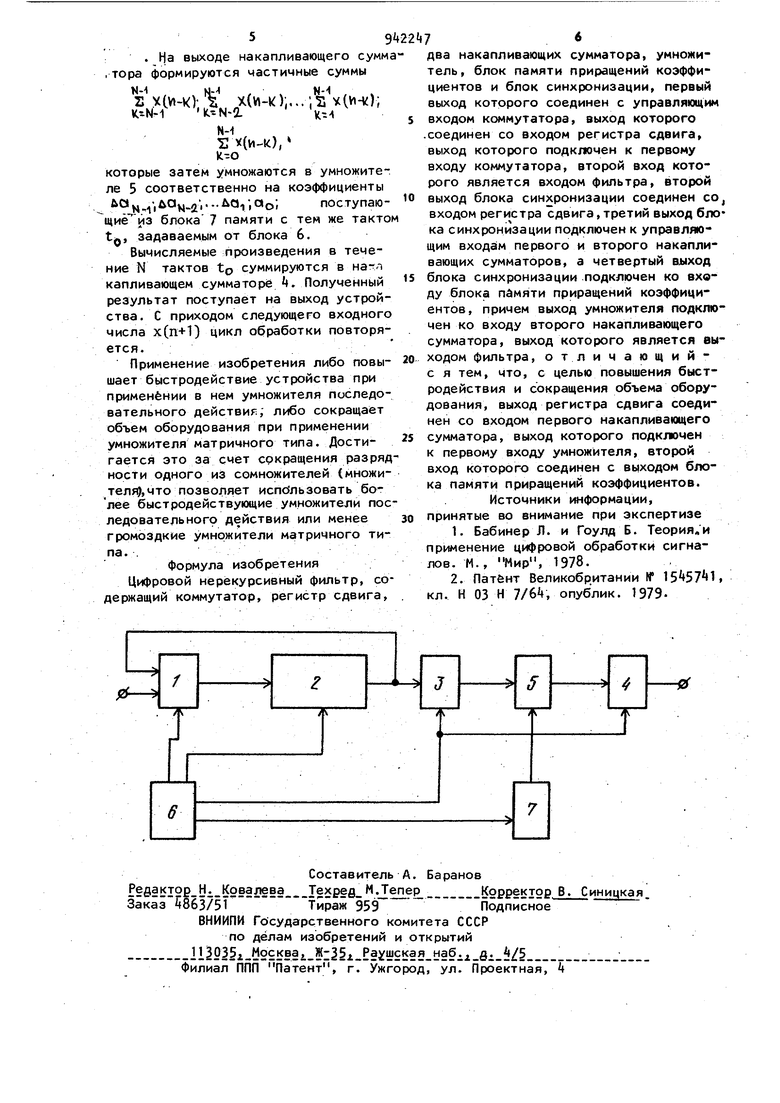

Наиболее близким к предлагаемому является цифровой фильтр, содержащий блок управления, пос ледова тел) но включенные коммутатор, регистр, умножи-; тель и накапливающий сумматор, а также, содержащий генератор весовых коэффициентов, состоящий из блока памяти приращений коэффициентов и соединенного с ним другого накапливающего сум матора, выход которого соединен со вторым входом умножителя L lИзвестное устройство отличается от указанных выше устройств тем, что в блоке памяти хранятся не многоразрядные значения весовых коэффициентов, а малоразрядные значения приращений этих коэффициентов, т.е. их первые разности. Значения же самих весовых коэффициентов получаются на выходе накапливающего сумматора при считывании в него приращений из блока памяти. За счёт сокращения объема 33 блока памяти, объем оборудования такого устройства в ряде случаев уменьшается. Однако быстродействие известного устройства также низкое из-за каличия операций умножения многоразрядных чисел. Применение же быстродействующих матричных умножителей увеличивает объем оборудования устройства. Цель изобретения - повышение быстродействия и сокращение объема оборудования цифрового фильтра. Поставленная цель достигается тем, что в устройстве, содержащем коммутатор, регистр сдвига, два накапливающих сумматора, умножитель, блок памяти приращений коэффициентов и блок синхронизации, первый выход которого соединен с управляющим входом коммутатора, выход которого соединен со входом регистра сдвига, выход которого подключен к первому входу коммутатора, второй вход которого является входом фильтра, второй выход блока синхронизации соединен со входом регистра сдвига, третий выход блока синхронизации подключен к управляю- щим входам первого и второго накапливающих cyjJ taTQpoB, а четвертый выход блока синхронизации подключен ко входу блока памяти приращений коэффициентов, причем выход умножителя подключен ко входу второго накапливающ§го сумматора, выход которого является выходом фильтра,выход регистра сдвига соединен со входом первого накапли вающего сумматора, выход которого под ключен к первому ВХОДУ умножителя, второй вход которого соединен с выходом блока памяти при|эащений коэффициентов . На чертеже приведена блок-схема предлагаемого устройства. Устройство Содержит коммутатор 1 регистр 2 сдвига, накапливающие сумматоры 3 и , умножитель 5 блок 6 синхронизации, блок 7 памяти приращений 1 Ъэффициентов. Для получения алгоритма работы предлагаемого устройства используется алгоритм сверки. 3(и) а хси-к), 1С.О(-1) где ytnj, - значение одного выходного отсчета в И-и момент време ни; x(ft-k) - значение входного (n-k)-ro отсчета; значение t-ro весового коэффициента; количество входных отсчетов, необходимое для вычисi ления одного выходного отсче та (N является длиной регистра сдвига). Выражение (1) можно преобразовать утем замены весовых коэффициентов их приращениями . При этом получим: Ки)-ОоХ Cvi-0 ) J X (ИИ) (... ....- да N-VlxCvi-lN-o r N-lМ-« :iao S ) + ikO,Т. XCifl-K) + K OК-Ч N-i. . x Cn-k)+... -fuOf.J () Из выражения (2) видно, что для бразования одного выходного отсчета следует сформировать N частичных сумм входных выборок, умножить их на соответствующие приращения коэффициентов и результаты сложить между собой. Цифровой нерекурсивный фильтр работает следующим образом. Входная информация через коммута тор 1 с заданным тактом Т поступает на вход регистра 2 сдвига. Очередное входное число х(п) записывается в первый элемент памяти регистра сдвига, а ранее записанные в регистре числа передвигаются вправо на один элемент, .причем последнее число из регистра выводится. Управление записью и сдвигом чисел осуществляется импульсом от блока 6, одновременно с этим производится обнуление накапливающих сумматоров 3 и 4. После этого блок 6 переключает коммутатор 1 и выдает на регистр сдвига 2 серию из N импульсов сдвига с тактом tg «с - . В результате действия этих импульсов производится считывание чисел из,регистра 2 в сумматор 3 Одновременно считываемые числа по цепи обратной связи через коммутатор 1подаются на вход регистра 2. После Ы тактов сдвига в регистре 2устанавливается первоначальное расположение чисел. Таким образом, на вход сумматора 3поступают по очереди числа xCH4N-i)))x (v)4N-2.));. . , х(ин)-,х(иА; .На выходе накапливающего сумма ,тора формируются частичные суммы s x(); х(и-к);...; sV(i-«); KiN-1 lc.N-2. КN--1i:v(n-k), которые затем умножаются в умножителе 5 соответственно на коэффициенты ,лац.,;,.ао; поступающиеijia блока 7 памяти с тем же такто trtj задаваемым от блока 6. Вычисляемые произведения в течение N тактов to суммируются в на-г.т капливающем сумматоре . Полученный результат поступает на выход устройства. С приходом следующего входного числа х(п+1) цикл обработки повторяется. Применение изобретения либо повышает быстродействие устройства при применении в нем умножителя последовательного действия; либо сокращает объем оборудования при применении умножителя матричного типа. Достигается это за счет сокращения разряд ности одного из сомножителей (множителя), что позволяет использовать более быстродействующие умножители пос ледователь ногр действия или менее громоздкие умножители матричного типа. . формула изобретения Цифровой нерекурсивный фильтр, со держащий коммутатор, регистр сдвига, два накапливающих сумматора, умножитель, блок памяти приращений коэффициентов и блок синхронизации, первый выход которого соединен с управляющим входом коммутатора, выход которого соединен со входом регистра сдвига, выход которого подключен к первому входу коммутатора, второй вход которого является входом фильтра, второй выход блока синхронизации соединен со, входом регистра сдвига,третий выход блока синхронизации подключен к управляющим входам первого и второго накапливающих сумматоров, а четвертый выход блока синхронизации подключен ко входу блока пймяти приращений коэффициентов, причем выход умножителя подключен ко входу второго накапливающего сумматора, выход которого является выходом фильтра, отличающийс я тем, что, с целью повышения быстродействия и Сокращения объема оборудования, выход регистра сдвига соединен со входом первого накапливающего сумматора, выход которого подключен к первому входу умножителя, второй вход которого соединен с выходом блока памяти приращений коэффициентов. Источники информации, принятые во внимание при экспертизе 1.Бабинер Л. и Гоулд Б. Теориями применение цифровой обработки сигналов. М., Мир, 1978. 2.Патент Великобритании ff кл. Н 03 Н 7/6, опублик. 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Нерекурсивный цифровой фильтр | 1984 |

|

SU1223346A1 |

| Нерекурсивный цифровой фильтр нижних частот | 1982 |

|

SU1037417A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1483608A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1998 |

|

RU2153698C2 |

Авторы

Даты

1982-07-07—Публикация

1980-10-27—Подача