1

Изобретение относится к контрольно-измерительной технике и может быть использовано в системах автоматического регулирования и управления с частотными сигналами первичных преобразователей .

Цель изобретения - повышение точности измерения.

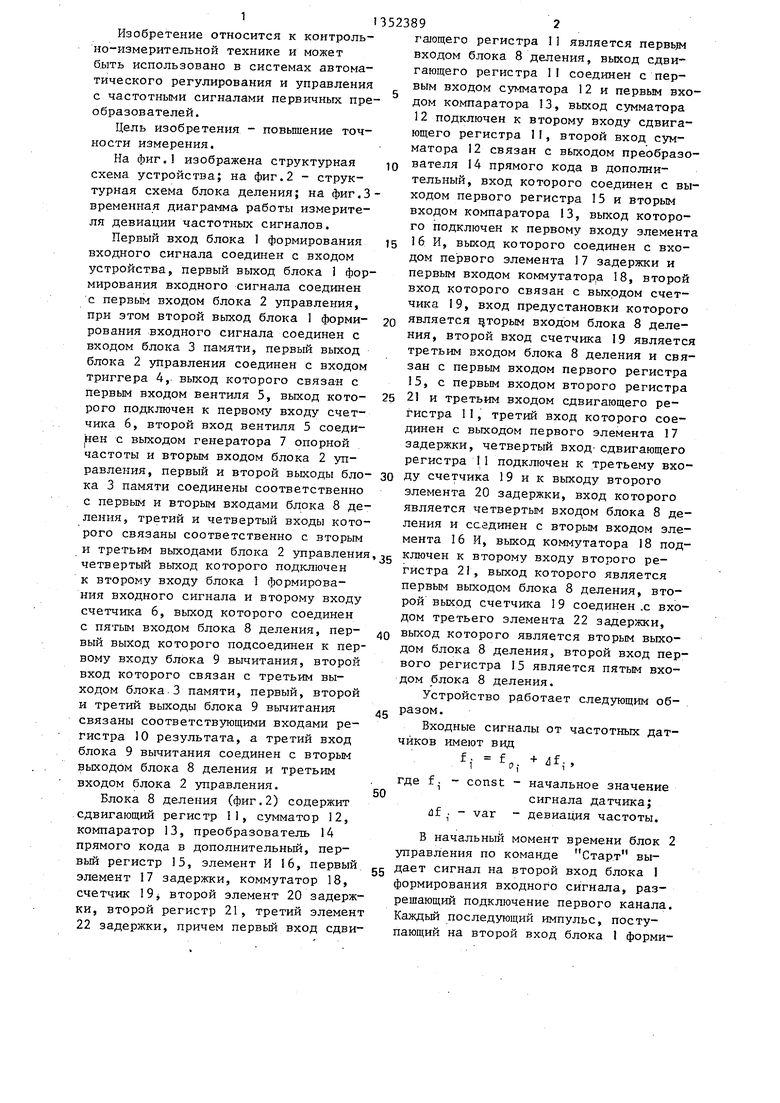

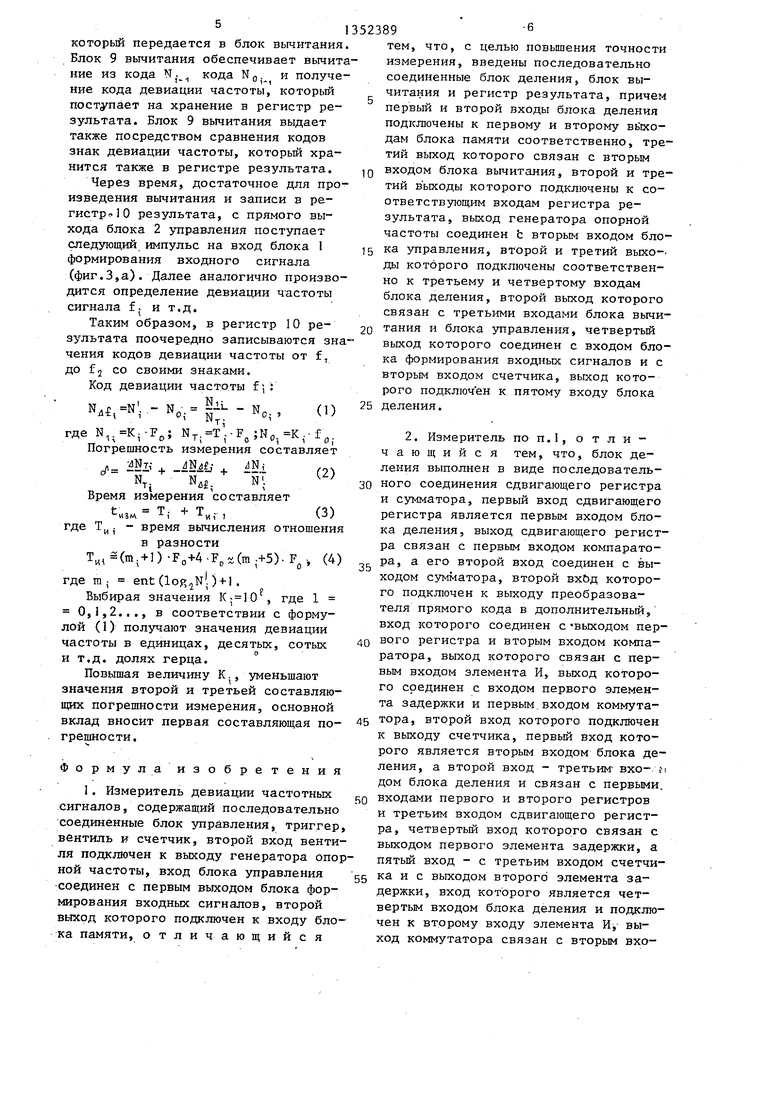

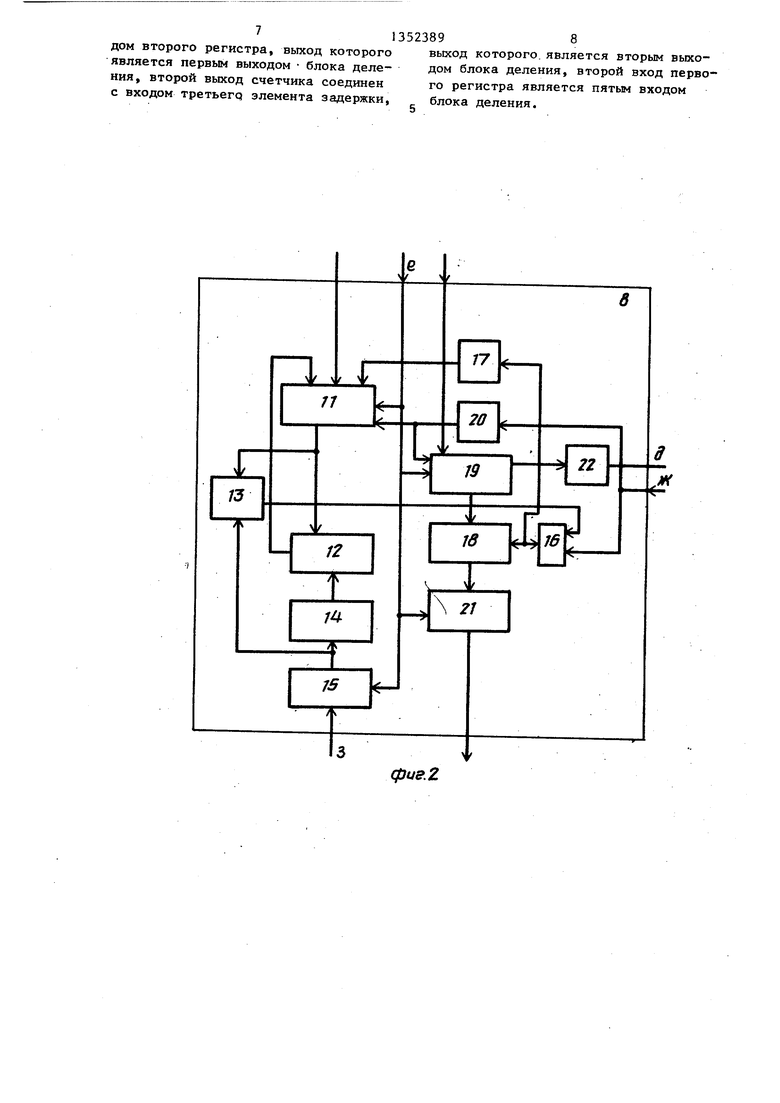

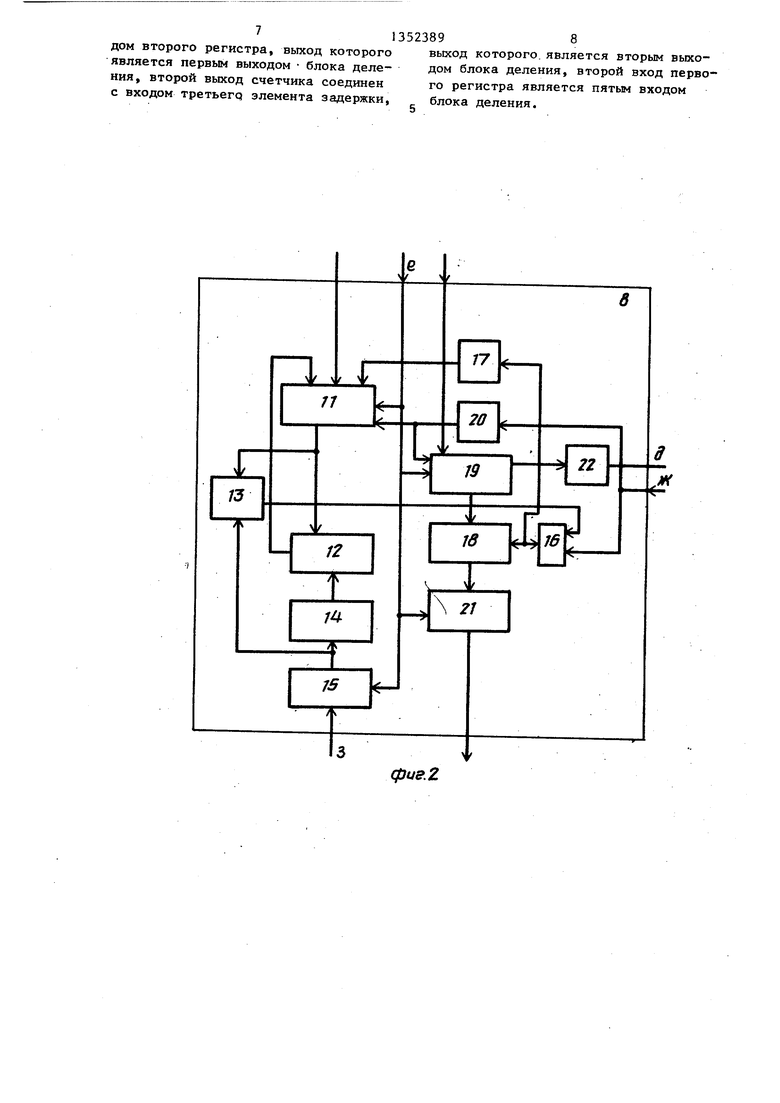

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурная схема блока деления; на фиг.3 временная диаграмма работы измерителя девиации частотных сигналов.

Первый вход блока 1 формирования входного сигнала соединен с входом устройства, первый выход блока i формирования входного сигнала соединен с первым входом блока 2 управления, при этом второй выход блока 1 форми- рования входного сигнала соединен с входом блока 3 памяти, первый выход блока 2 управления соединен с входом триггера 4, выход которого связан с первым входом вентиля 5, выход кото- рого подключен к первому входу счетчика 6, второй вход вентиля 5 соединен с выходом генератора 7 опорной частоты и вторым входом блока 2 управления, первый и второй выходы бло ка 3 памяти соединены соответственно с первым и вторым входами блока 8 деления, третий и четвертый входы которого связаны соответственно с вторым

и третьим выходами блока 2 управления, jg ключен к второму входу второго речетвертый выход которого подключен к второму входу блока 1 формирования входного сигнала и второму входу счетчика 6, выход которого соединен с пятым входом блока 8 деления, первый выход которого подсоединен к первому входу блока 9 вычитания, второй вход которого связан с третьим выходом блока.3 памяти, первый, второй и третий выходы блока 9 вычитания связаны соответствующими входами регистра 10 результата, а третий вход блока 9 вычитания соединен с вторым выходом блока 8 деления и третьим входом блока 2 управления.

Блока 8 деления (фиг.2) содержит сдвигающий регистр 11, сумматор 12, компаратор 13, преобразователь 14 прямого кода в дополнительный, первый регистр 15, элемент И 16, первый элемент 17 задержки, коммутатор 18, счетчик 19j второй элемент 20 задержки, второй регистр 21, третий элемент 22 задержки, причем первьш вход сдви40

45

50

55

гистра 21, выход которого является первым выходом блока 8 деления, вто рой выход счетчика 19 соединен .с вх дом третьего элемента 22 задержки, выход которого является вторым выхо дом блока 8 деления, второй вход пе вого регистра 15 является пятым вхо дом блока 8 деления.

Устройство работает следзтощим об разом.

Входные сигналы от частотных дат чиков имеют вид

f f.,- f,- где f- - const - начальное значение

сигнала датчика; й - var - девиация частоты.

В начальный момент времени блок управления по команде Старт выдает сигнал на второй вход блока 1 формирования входного сигнала, разрешающий подключение первого канала Каждый последующий импульс, поступающий на второй вход блока I форми

2

гшощего регистра 11 является первь м входом блока 8 деления, выход сдвигающего регистра II соединен с первым входом сумматора 12 и первым входом компаратора 13, выход сумматора 12 подключен к второму входу сдвигающего регистра П, второй вход сумматора 12 связан с выходом преобразователя I4 прямого кода в дополнительный, вход которого соедршен с выходом первого регистра 15 и вторым входом компаратора 13, выход которого подключен к первому входу элемента 16 И, выход которого соединен с входом первого элемента 17 задержки и первым входом коммутатора 18, второй вход которого связан с выходом счетчика 19, вход предустановки которого является торым входом блока 8 деления, второй вход счетчика 19 является третьим входом блока 8 деления и связан с первым входом первого регистра 15, с первым входом второго регистра 21 и третьим входом сдвигающего регистра 1I, третий вход которого соединен с выходом первого элемента 17 задержки, четвертый вход- сдвигающего регистра 11 подключен к третьему входу счетчика 19 и к выходу второго элемента 20 задержки, вход которого является четвертым входом блока 8 деления и ссадинен с вторым входом элемента 16 И, выход коммутатора 18 подключен к второму входу второго ре

гистра 21, выход которого является первым выходом блока 8 деления, второй выход счетчика 19 соединен .с входом третьего элемента 22 задержки, выход которого является вторым выходом блока 8 деления, второй вход первого регистра 15 является пятым входом блока 8 деления.

Устройство работает следзтощим образом.

Входные сигналы от частотных датчиков имеют вид

f f.,- f,- где f- - const - начальное значение

сигнала датчика; й - var - девиация частоты.

В начальный момент времени блок 2 управления по команде Старт выдает сигнал на второй вход блока 1 формирования входного сигнала, разрешающий подключение первого канала. Каждый последующий импульс, поступающий на второй вход блока I формирования входного сигнала, подключает очередной входной сигнал f. , ив соответствии с ним поступает импульс на вход блока 3 памяти, который подключает очередные значения, хранящиеся в блоке 3 памяти, соответствующие сигналу f..

На фиг.З представлена временная диаграмма работы устройства. ю

Рассмотрим работу устройства при поочередном включении датчика.

В момент подключения (i-l)-ro канала блок I формирования входного сигнала вырабатьшает сигнал на управ- is ии тактового импульса элемент И 16

полнения этих операций, с третьего выхода блока 2 управления на четвертый вход блока 8 деления начинают по ступать импульсы тактовой частоты F (фиг.З,ж). Сдвигающий регистр 11 име ет разрядность m+n+1, в разряды 1 - (m+n) записан код Ni,-,, в старший (т+п+1)-й разряд - О.

Компаратор 13 сравнивает число, записанное в (п+1) старших разрядах сдвигающего регистра 11, и число,

записанное в регистре

П-И

15 NT-.

1

Если N, э то при поступле

ление блоком 3 памяти.

Блок 3 памяти устанавливает при поступлении на его вход (i-l)-ro импульса от блока 1 формирования входного сигнала на первом выходе код, пропорциональньш частоте F опорного генератора 7: N. К (К . - коэффициент пропорциональности), на втором выходе - код предустановки счетчика 19 блока 8 деления, опреде- ляющий точность деления (т +1), на третьем выходе - код, пропорциональный начальной частоте (i-l)-ro датчика, используемый в блоке вычитания: NO. К-.,- fo..

При поступлении входного, сигнала f блок 1 формирования входного сигнала формирует импульс, которьш поступает на первый вход блока 2 уп-г равления (фиг.З.б). Импульс с перво- го выхода блока 2 управления (фиг.З, переводит триггер 4 из нулевого в. . единичное состояние. Триггер 4 открывает вентиль 5 и пропускает на счетчик 6 импульсы опорной частоты FQ с генератора 7 опорной частоты. По окочании периода Т; с выхода блока 1 формирования входного сигнала на первый вход блока 2 управления пос- тупает второй импульс, который, проходя на вход триггера 4, переводи его в нулевое состояние, закрьтая вентиль 5. К этому времени в счетчике 6 будет записан код Nj, F . Т,

. V J -I

пропорциональный периоду частоты входного сигнала. После этого с второго вькода блока 2 управления (фиг.3,е),проходит импульс на третий вход блока 8 деления, при поступлении которого производится запись ко- да N. в сдвигающий регистр 11, кода NT- в регистр 15, предустановка счетчика 19 и обнуление регистра 21. Через время, достаточное для выполнения этих операций, с третьего выхода блока 2 управления на четвертый вход блока 8 деления начинают поступать импульсы тактовой частоты F (фиг.З,ж). Сдвигающий регистр 11 имеет разрядность m+n+1, в разряды 1 - (m+n) записан код Ni,-,, в старший (т+п+1)-й разряд - О.

Компаратор 13 сравнивает число, записанное в (п+1) старших разрядах сдвигающего регистра 11, и число,

ии тактового импульса элемент И 16

записанное в регистре

П-И

15 NT-.

1

Если N, э то при поступлезакрыт и в (iTi +1)-м разряде регистра 21 сохраняется О, через время задержки 1 второго элемента 20 задерки импульс поступает на счетчик 19, уменьшая его содержимое на единицу и тем самым переключая вьпсод коммутатора на разряд т. регистра 21, одновременно импульс, поступая на пятый вход сдвигающего регистра 11, осуществляет сдвиг его содержимого ., на единицу в сторону старщих разрядов. Компаратор 13 снова сравнивает значение нового кода с кодом N .

В случае если N J N-,-. . то

1-1 1-1 при поступлении тактового импульса

элемент И 16 открыт, через коммутатор 18 на вход (т. +1)-го разряда регистра 21 поступает импульс и в регистре 21 записьшается 1. Из кода (п+1) старших разрядов регистра 11 вычитается код М с пoмoIr ью преобразователя 14 прямого кода в дополнительный и сумматора 12. Разность записывается в (п+1)-и старший разряд сдвигающего регистра 11 при поступлении импульса с выхода элемента 17 задержки через время С, через время f i - с) поступает импульс сдвига содержимого регистра 11 в сторону старших разрядов. Далее процесс повторяется до тех пор, пока не обнулится счетчик 19. №1пульс с выхода счетчика 19 через элемент 22 задержки через время i)j поступает на второй вход блока 8 деления и далее на третий вход блока 2 управления (фиг.3,д), подача импульсов тактовой частоты Fp на блок 8 деления прекращается. В регистре 21 к этому времени хранится код частного от деления дв5 кодов

- NT....

который передается в блок вычитания Блок 9 вычитания обеспечивает вычитание из кода Nf кода Ng. и получение кода девиации частоты, который поступает на хранение в регистр результата. Блок 9 вь читания выдает также посредством сравнения кодов знак девиации частоты, который хранится также в регистре результата.

Через время, достаточное для произведения вычитания и записи в регистр 10 результата, с прямого выхода блока 2 управления поступает следующий импульс на вход блока 1 формирования входного сигнала (фиг.3,а). Далее аналогично производится определение девиации частоты сигнала f; и т.д.

Таким образом, в регистр 10 результата поочередно записываются значения кодов девиации частоты от f, до fj со своими знаками.

Код девиации частоты

N.i,N;

где N

(1)

м . N

; NT-. °

.-F,; N,..K..f,. Погрешность измерения составляет

+

JNi

uf N ., oi- ,

Время измерения составляет

/ N..

,- N,

(2)

где Т

-vlJW

Т; + Т

Ml 1

(3) - время вычисления отношения

в разности Т,, (1П; + 1) -FO+A -F,-(т ;+5). F , (4)

где га. ent (los.oN. ) + 1 .

i 1rt

Выбирая значения , где 1 О,,2..., в соответствии с формулой (1) получают значения девиации частоты в единицах, десятых, сотых и т.д. долях герца.

Повьпиая величину К., уменьшают значения второй и третьей составляющих погрешности измерения, основной вклад вносит первая составляюш;ая погрешности.

Формула изобретения

1. Измеритель девиации частотных сигналов, содержащий последовательно соединенные блок управления, триггер вентиль и счетчик, второй вход вентиля подключен к выходу генератора опоной частоты, вход блока управления соединен с первым выходом блока формирования входных сигналов, второй выход которого подключен к входу блока памяти, отличающийся

5

0

тем, что, с целью повышения точности измерения, введены последовательно соединенные блок деления, блок вычитания и регистр результата, причем первый и второй входы блока деления подключены к первому и второму вйко- дам блока памяти соответственно, третий в1згход которого связан с вторым входом блока вычитания, второй и третий в ыходы которого подключены к соответствующим входам регистра результата, выход генератора опорной частоты соединен fc вторым входом блока управления, второй и третий выхо-. ды которого подключены соответственно к третьему и четвертому входам блока деления, второй выход которого связан с третьими входами блока вычитания и блока зшравлення, четвертьй выход которого соединен с входом блока формирования входных сигналов и с вторым входом счетчика, выход кото25

рого подключен деления.

к пятому входу блока

2. Измеритель по п.1, о т л и 5

чающийся ления выполнен в

тем, что, блок де- виде последователь0 ного соединения сдвигающего регистра и сумматора, первый вход сдвигающего регистра является первым входом блока деления, выход сдвигающего регистра связан с первым входом компаратора, а его второй вход соединен с выходом сумматора, второй вхбд которого подключен к выходу преобразователя прямого кода в дополнительный, вход которого соединен с -выходом перQ вого регистра и вторым входом компаратора, выход которого связан с первым входом элемента И, выход которого соединен с входом первого элемента задержки и первым.входом коммута5 тора, второй вход которого подключен к выходу счетчика, первьй вход которого является вторым входом блока деления, а второй вход - третьим- вхо- fi дом блока деления и связан с первыми.

0 входами первого и второго регистров и третьим входом сдвигающего регистра, четвертый вход которого связан с выходом первого элемента задержки, а пятьш вход - с третьим входом счетчи5 ка и с выходом второго элемента задержки, вход которого является четвертым входом блока деления и подключен к второму входу элемента И, выход коммутатора связан с вторым вхо-

13523898

дом второго регистра, выход которого выход которого, является вторым вькоявляется первым выходом блока деления, второй выход счетчика соединен с входом третьегр элемента задержки,

дом блока деления, второй вход первого регистра является пятым входом блока деления.

выход которого, является вторым вькодом блока деления, второй вход первого регистра является пятым входом блока деления.

фие.г

фиЗ:3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Преобразователь отношения двух частот в код | 1976 |

|

SU660231A1 |

| Измеритель девиации частоты | 1990 |

|

SU1711088A1 |

| Частотно-импульсное делительное устройство | 1980 |

|

SU898429A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для прогнозирования состояния технических объектов | 1982 |

|

SU1104533A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Умножитель частоты | 1983 |

|

SU1167692A2 |

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

Изобретение может быть использовано в системах автоматического регулирования и управления с частотными сигналами первичных преобразователей. Цель изобретения - повьшение точности измерения. Устройство содер- . жит блоки I, 2 и 3 формирования входного сигнала, управления и памяти, триггер 4, вентиль 5, счетчик 6 и генератор 7 опорной частоты. Для достижения поставленной цели в устройство введены блок 8 деления, блок 9 вычитания и регистр 10 результата и дан пример конкретного выполнения блока 8 деления. I з.п. ф-лы, 3 ил. с (Л со сд N3 00 оо со

| Измеритель девиации частотных сигналов | 1979 |

|

SU864164A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-15—Публикация

1985-12-18—Подача