10

25

Изобретение относится к вычислительной технике и может быть исполь- .зовано при построении устройств обработки сигналов частотных датчиков.

Цель изобретения - повышение точ- ности умножителя.

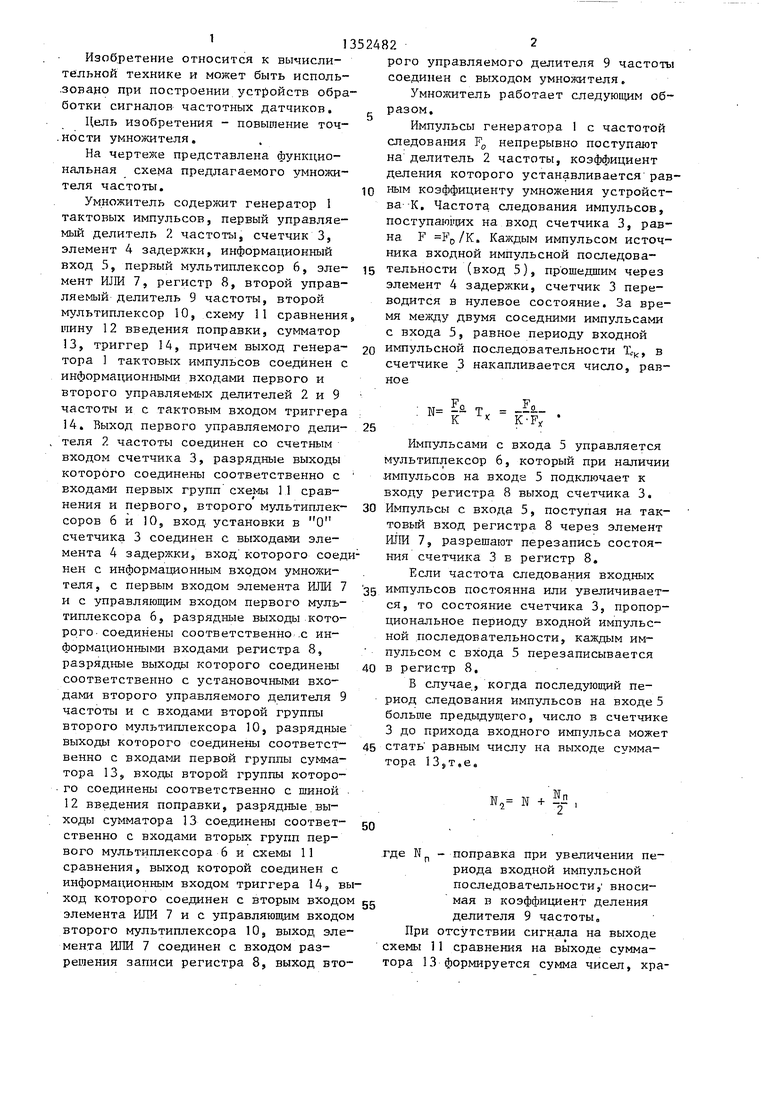

На чертеже представлена функциональная схема предлагаемого умножителя частоты.

Умножитель содерлсит генератор 1 тактовых импульсов, первый управляе- мьш делитель . частоты, счетчик 3, элемент 4 задержки, информационный вход 3, первый мультиплексор 6, элемент ШШ 7, регистр 8, второй управляемый делитель 9 частоты, второй мультиплексор 10, схему 11 сравнения шину 12 введения поправки, сумматор

13,триггер 14, причем выход генератора 1 тактовых импульсов соединен с информационными входами первого и второго управляемых делителей 2 и 9 частоты и с тактовым входом триггера

14.Выход первого управляемого дели- теля 2 частоты соединен со счетным

входом счетчика 3, разрядные выходы которого соединены соответственно с входами первых групп схемы 11 сравнения и первого, второго мультиплексоров 6 и 10, вход установки в О счетчика 3 соединен с выходами элемента 4 задержки, вход которого соединен с информационным входом умножителя , с первым входом элемента ИЛИ 7 и с управляющим входом первого мультиплексора 6, разрядные выходы которого- соединены соответственно .с информационными входами регистра 8, разрядные выходы которого соединены соответственно с установочными входами второго управляемого делителя 9 частоты и с входами второй группы второго мультиплексора 10, разрядные выходы которого соединены соответственно с входами первой группы сумматора 13, входы второй группы которо- го соединены соответственно с шиной . 12 введения поправки, разрядные выходы сумматора 13 соединены соответственно с входами вторых групп первого мультиплексора 6 и схемы 11 сравнения, выход которой соединен с информационным входом триггера 14, выход которого соединен с вторым входом gg элемента ИЛИ 7 и с управляющим входом второго мультиплексора 10, выход элемента ИЛИ 7 соединен с входом разрешения записи регистра 8, выход вто15

20

30

35

40

45

50

рого управляемого делителя 9 частоты соединен с выходом умножителя,

Умножитель работает следующим образом.

Импульсы генератора 1 с частотой следования F непрерывно поступают на делитель 2 частоты, коэффициент деления которого устанавливается равным коэффициенту умножения устройства- -К. Частота следования импульсов, поступаю1 1их на вход счетчика 3, равна F F(5/K. Каждым импульсом источника входной импульсной последовательности (вход 5), прощедшим через элемент 4 задержки, счетчик 3 переводится в нулевое состояние. За время между двумя соседними импульсами с входа 5, равное периоду входной

импульсной последовательности 1,, в 3 накапливается число, равсчетчикеное

TVT-

N--Т K-F.

Импульсами с входа 5 управляется ультиплексор 6, который при наличии мпульсов на входе 5 подключает к ходу регистра 8 выход счетчика 3 Импульсы с входа 5, поступая на тактовый вход регистра 8 через элемент И11И 7, разрешают перезапись состояния счетчика 3 в регистр 8,

Если частота следования входных импульсов постоянна или увеличивается, то состояние счетчика 3, пропорциональное периоду входной импульсной последовательности, каждым импульсом с входа 5 перезаписывается в регистр 8. В случае, когда последующий период следования импульсов на входе 5 больше предыдущего, число в счетчике 3 до прихода входного импульса может стать равным числу на выходе сумматора 135Т,е,

К,

N

.5.

где Nj - поправка при увеличении периода входной импульсной последовательности, вноси- мая в коэффициент деления

делителя 9 частоты. При отсутствии сигнала на выходе схемы 11 сравнения на выходе сумматора 13 формируется сумма чисел, хра

нящихся в регистре 8 и на шине 12.

-:::,

На вгану 1 . подано число 2

Если период входной импульсной последовательности увеличивается на столько, что число счетчика 3 становится равным (N+ -), то срабатывает схема 11 сравнения. Сигналом с ее. выхода переключается триггер 14, а мультиплексор 10 при этом подключает к второму входу сумматора 13 выход счетчика 3. На выходе сумматора

формируется число (N+ 5-) п р

поступающее через мультиплексор 6 на вход регистра 8, который перезаписывает это число, так как перезапись разрешена сигналом с триггера 14, прошедшим через элемент ИЛИ 7,

Как только на выходе сумматора 13 формируется число (N+N,,), схема 11 сравнения снимает сигнал с информационного входа триггера l4, но он rfe переключается, так как действие оче- редного импзшьса генератора 1 заканчивается.

Следзпощим импульсом триггер 14 переключается, сигнал разрешения перезаписи с тактового входа регистра 8 снимается.

При следующем равенстве чисел в счетчике 3 -и на выходе сумматора 13 процессы повторяются.

Сравнение числа в счетчике 3 с

N ч

числом () усредняет погрешность

при внесении поправки N, Внесение определенной, а не случайной поправки в коэффициент деления делителя 9 частоты позволяет повысить точность умножителя.

Делитель 9 частоты осуш;ествляет деление частоты генератора 1 на число, хранящееся в регистре 8. На вы- ходе устройства настота импульсной последовательности при установившейся входной частоте равна

Fn,-K - Fv

N

K-F,

При уменьшении частоты импульсной последовательности на входе 5 изменение частоты на выходе устройства Происходит в изменившемся периоде.

Формула изо. бретения

Умножитель частоты, содержащий генератор тактовых импульсов, первый

fO

15

25

20

30

35

40

45

50

55

и второй управляемые делители частоты, регистр, счетчик, схему сравнения, триггер и элемент задержки, причем выход генератора тактовь х импульсов соединен с информационным входом первого управляемого делителя частоты, установочные входы которого соединены соответственно с установочными входами умножителя. информационный вход которого соединен с входом элемента задержки, выход которого соединен с входом установки в О счетчика, счетный вход которого соединен с выходом Первого управляемого делителя частоты, разрядные выходы счетчика соединены соответственно с входами первой группы схемы сравнения, выход которой соединен с информационным входом триггера, тактовый вход которого соединен с выходом генератора тактовых импульсов, разрядные выходы регистра соединены соответственно с установочными входами второго управляемого делителя частоты, информа1, вход которого соединен с выходом Генератора тактовых импульсов, а выход второго управляемого делителя частоты соединен с вы ходом умножителя отличаю- щ и и с я тем, что, с целью повышения точности умножителя 5 в него введены первый и второй мультиплексоры, сумматор и элемент HJli, причем разрядные выходы счетчика соединены соответственно с входами первых групп первого и второго мультиплексоров, входы второй группы первого мультиплексора соединены соответственно с разрядными выходами сумматора и с входами второй группы схеь-ы сравнения, выходы первого мультиплексора соединены соответственно с информационными BxonaMi регистра, вход разрешения записи которого соединен с выходом элемента ИЛИ, управляюш,ий вход первого мультиплексора соединен с первым входом элемента ИЛИ и с ин- формацион1-1ым входом умножителя, разрядные выходы регистра соединены соответственно с входами второй группы вто рого мультиплексора, выходы которого соединены соответственно с входгами первой группы сумматора, входы второй группы которого соединены с шиной введения поправки умножителя, выход.триггера соединен с вторым вхо-. дом элемента ИЛИ и с управляющим входом второго мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1547050A1 |

| ГЕНЕРАТОР ПОСЛЕДОВАТЕЛЬНОСТЕЙ КОДА СТИФФЛЕРА | 2017 |

|

RU2668742C1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| ГЕНЕРАТОР ДИСКРЕТНЫХ ОРТОГОНАЛЬНЫХ СИГНАЛОВ | 2017 |

|

RU2634234C1 |

| МОДУЛЯТОР ДИСКРЕТНОГО СИГНАЛА ПО ВРЕМЕННОМУ ПОЛОЖЕНИЮ | 2018 |

|

RU2677358C1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств обработки сигналов частотных датчиков. Цель изобретения - повышение точности умножителя. Предложен:ный умножитель содержит генератор 1 тактовых импульсов, первый управляемый делитель частоты, сЧетчик 3, элемент 4 задержки, информационный вход 5, первый мультиплексор 6, элемент ИЛИ 7, регистр 8, второй управляемый делитель 9 частоты, второй мультиплексор 10, схему 11 сравнения, шину 12 введения поправки, сумматор 13 и триггер 14 с соответствующими связями. Умножитель осуществляет перемножение входного частотного сигнала, поступающего на информационный вход, на коэффициент, записанный в первый управляемый делитель частоты, осуществляя поправку коэффициента умножения при уменьшении часто-ш входного сигнала. 1 шт. W со ел го 00

| Умножитель частоты следования импульсов | 1981 |

|

SU1008740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения частотыСлЕдОВАНия иМпульСОВ | 1979 |

|

SU817711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1985-12-13—Подача