триггеров объединены, группа из п регистров (где п - округление до ближайшего большего числа отношения максимальной к минимальной входных частот), группа из (п-2) элементов и группа из (п-1) триггеров, причем 1-й триггер ( 1 1,...,и-1) инверсным выходом соединен с первым входо 1-го элемента И, прямым выходом - с вторым входом (i-l)-ro элемента И, вход установки в 1 i-ro триггера соединен с выходом i-ro элемента И, входом установки в О (i+1)-ro триггера и входом разрешения записи (i+1)-ro регистра, входы синхронизации триггеров с первого по (п-1)й соединены с выходом элемента НЕ, вход которого соединен с выходом генератора тактовых импульсов, входом синхронизации И-триггеров тактирушщего блока, третьими входами элементов И с первого по (п-2)-и, стробирующим входом второй схемы сравнения, выход которой соединен с входом разрешения записи h-ro регистра, входом установки в 1 (n-l)-ro триггера, первым входом элемента ИЛИ, входы первой группы второй схемы сравнения соединены соответственно с разрядными выходами первого

51959

делителя частоты и младшими разрядными входами первого регистра группы, входы второй группы - с разрядными выходами,второго счетчика и старшими разрядными входами первого регистра группы, а входы третьей группы - с разрядными выходами п-го регистра и входами преобразователя прямого кода в дополнительньш, разрядные выходы которого соединены соответственно с входами первой группы второго сумматора, младшие разрядные выхода которого соединены соответственно с входами второго регистра, а старшие разрядные выходы - с входами третьего регистра, входы второй группы второго сумматора соединены соответственно с разрядными выходами (n-l)-ro регистра, разрядные выходы i-ro регистра соединены соответственно с разрядными входами (i+1)-ro регистра, выход элемента И тактирующего блока соединен с входом разрешения записи первого регистра групгы и входом установки в О первого триггера группы, установочный , вход первого Е-триггера тактирующего блока соединен с входной инфор-; мационной шиной умножителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

УМНОЖИТЕЛЬ ЧАСТОТЫ, содержащий генератор тактовых импульсов, первый и второй делители частоты, первьй и второй элементы И, первую схему сравнения, блок синхронизации, элемент ИЛИ, первый и второй счетчики, триггер, первый сумматор, первый, второй и третий регистры, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, тактовым входом блока синхронизации и счетным входом первого делителя частоты, второй вход первого элемента И соединен с выходом блока синхронизации, а выход - со счетным входом первого счетчика, вход установки в О блока синхронизации соединен с выходом первой схемы сравнения, с первым входом установки в О первого счетчика, первым входом второго элемента И, счетным входом второго делителя частоты и входом разрешения записи первого регистра, информационный вход блока синхронизации соединен со старшим разрядным выходом сумматора, остальные разрядные выходы сумматора соединены соответственно с информационными входами первого регистра, входы первой группы сумматора соединены соответственно с разрядными выходами второго регистра, входы второй группы сумматора соединены соответственно с разрядными выходами nepBoko регистра, вход установки в О которого соединен с вторьм входом установки в О первого счетчика, входами разрешения записи второго и третьего регистров, входом установки в О второго делителя частоты, первым входом триггера и первым входом элемента ИЛИ, выход которого является выходом умножителя частоты, а второй вход соединен с выходом второго элемента И, (Л второй вход которого соединен, с выходом триггера, второй вход триггера соединен с выходом второго делителя частоты, выход старшего разряда первого делителя частоты соединен со счетным входом второго счетчика, первая и вторая группы входов первой схемы сравнения соединены соответстсд венно с разрядными выходами третьего регистра и первого .счетчика, отлисо ел чающийся тем, что, с целью уменьшения динамической погрешности со умножения, в него введены второй сумматор, вторая схема сравнения, преобразователь прямого кода в дополнительньй, элемент НЕ, тактируюпщй блок, содержащий два В-триггера и элемент И, первый вход которого соединен с прямым выходом первого Dтриггера и установочным входом второго D-триггера, инверсный выход которого соединен с вторым входом элемента И, входы синхронизации двухБ

I

Изобретение относится к автоматике и вычислительной техйике и может быть использовано при обработке информации, представленной в виде часто тис- импульсных пЬследовательностей

Цель изобретения - уменьшение динамической погрешности умножения и повышение равномерности следования выходных импульсов при любой неравномерности следования вкодньк импульсов.

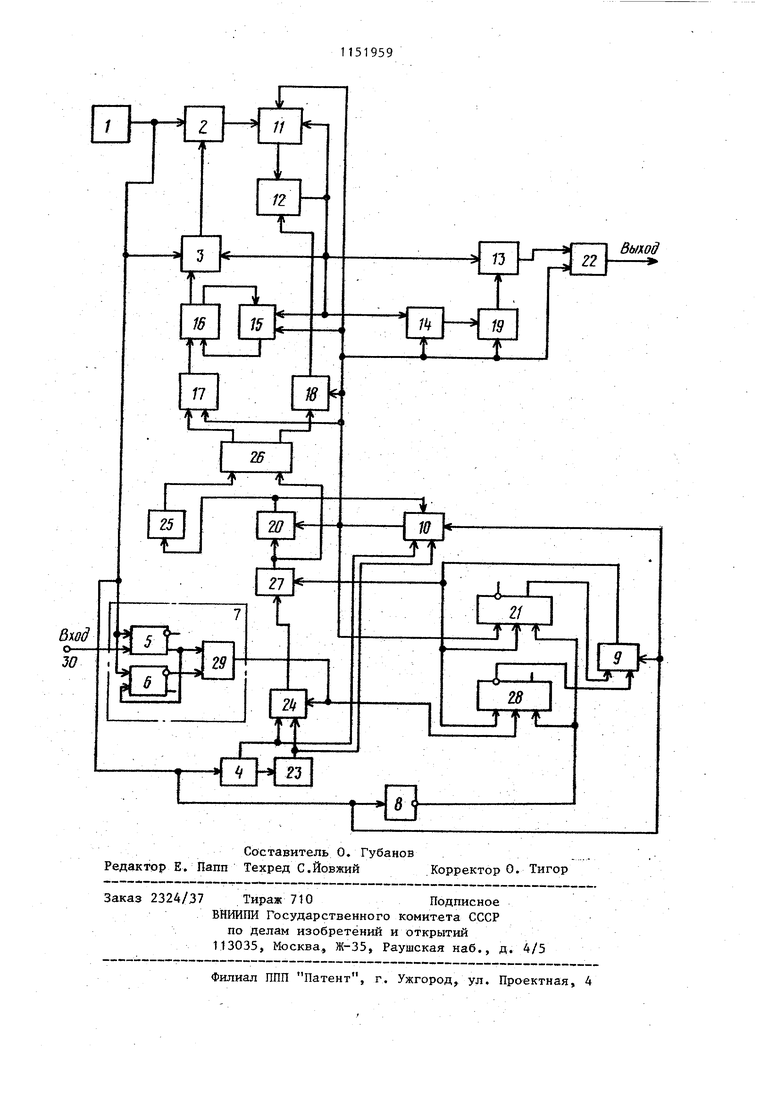

На чертеже изображена блок-схема умножителя частоты. Для наглядности примем п 3.

Умножитель частоты содержит генератор 1 тактовых импульсов, подключенный выходо 4 к первому входу первого элемента И 2, тактовому входу блока 3 синхронизации, к счетному входу первого делителя 4 частоты, к

входу синхронизации первого 5 и второго D-триггеров 6 тактирующего блока 7, входу элемента НЕ 8, третьему входу третьего элемента И 9, к стробирующему входу второй схемы 10 сравнения. Элемент И 2 соединен выходом со счетным входом.первого счетчика 11, а вторым входом - с выходом блока 3 синхронизации. Вход установки в О блока 3 синхронизации соединен с выходом первой схемы 12 сравнения, с первым входом установки в О счетчика 11, первым входом второго элемента И 13, счетным входом второго делителя 14 частоты и входом разрешения записи первого регистра 15 а информационным входом - со старшим разрядным выходом первого сумматора 16, Остальные разрядные выходы сумматора 16 соединены соответственно с информационными входами регистра 15. Входы первой группы сумматора 16 соединены соответственно с разрядными выходами второго регистра 17, а входы второй группы сумматора 16 с разрядными выходами регистра 15, вход установки в О которого соединен с выходом второй схемы 10 сравнения, с вторым входом установки в О счетчика 11, входами разрешения записи второго и третьего регистров 17 и 18, входом установки в О делителя 14 частоты, первым входом первого триггера 19, с входом разрешения записи четвертого регистра 20, с входом установки в 1 второго триггера 21 и первым входом элемента ИЛИ 22. Выход элемента ИЛИ 22 является выходом умножителя частоты, а второй вход элемента ИЛИ 22 соединен с выходом элемента И 13, второй вход которого подключен к выходу триггера 19, соединенного вторым входом с выходом делителя 14 частоты Выход старшего разряда делителя 4 частоты соединен со счетным входом второго счетчика 23. Первая и вторая группа входов первой схемы 12 сравнения соединены соответственно с разрядными выходами регистра 18 и счетчика 11. Входы первой группы схемы 10 сравнения соединены соответственно с разрядными выходами делителя 4 частоты и младшими разрядны ми входами пятого регистра 24, входы второй группы - с разрядными выходами счетчика 23 и старшими разрядными входами регистра 24 а входы третьей группы - с разрядными выходами регистра 20 и входами преобразователя 25, прямого кода в дополнительный, разрядные выходы которого соединены соответственно с входами первой группы второго сумматора 26. Младшие разрядные выходы сумматора 26 соединены соответственно с входами регистра 17, а старшие разрядные выходы - с входами регистра 18. Вход второй группы сумматора 26 соединены соответственно с разрядными выходам шестого регистра 27 и разрядными входами регистра 20. Информационные входы регистра 27 соединены соответственно с разрядными выходами регистра 24, а вход разрешения запис регистра 27 подключен к выходу элемента И 9, к ВХОДУ установки в О триггера 21 и к входу установки в 1 третьего триггера 28. Входы синхронизации триггеров 21 и 28 соединены с выходом элемента НЕ 8. Элемент И 9 первым входом соединен с прямым выходом триггера 21, а вторым входом - с инверсным выходом триггера 28. Тактирующий блок 7 представляет собой синхронизируемую импульсами генератора 1 схему привязки и содержит два D -триггера 5 и 6 и элемент И 29, первый вход которого соединен с прямым выходом триггера 5 и информационным входом триггера 6 инверсный выход которого соединен с вторым входом элемента И 29. Выход элемента И 29 тактирующего блока 7 соединен с входом разрешения записи регистра 24 и входом установки в О триггера 28. Информационный вход триггера 5 соединен с входной информационной шиной 30 умножителя частоты. Умножитель частоты работает следующим образом. Тактовые импульсы с периодом Т с выхода генератора 1 поступают через гп-разрядный делитель 4 с коэффициентом деления К, равным требуемому коэффициенту умножения умножителя, на вход Р-разрядного счетчика 23. В ответ на j-й входной импульс с входной информационной шины 30 умножителя частоты, поступающий на тактирующий блок 7, ближайший тактовый импульс генератора 1 появляется на выходе элемента И 29 тактирующего блока 7, этот импульс своим передним фронтом переносит число из делителя 4 и счетчика 23 в регистр 24, т.е. зафиксирует начало j-ro периода входного сигнала, и подготовит триггер 28 к установке в О. В этот же момент устанавливается триггер 28 в О фронтом тактового импульса с инвертора, подсчет тактовых импульсов делителем 4 и счетчиком 23 производится этим же фронтом тактового №Jпульса. Следующий после этого тактовый импульс проходит через схему И 9 и подготавливает триггер 21 к установке в О, а триггер 28 - к установке в 1. Передним фронтом этого импульса переносится информация из регистра 24 в регистр 27, а задним фронтом устанавливаются триггер 28 в 1, а триггер 21 в О. В результате совпадения кодов в регистре 20, делителе 4 к счетчике 23 очередной тактовый импульс переносит информацию из регистра 27 в регистр 20, устанавливает счетчик 11 в О, а триггер 21 - в 1, этот же импуль переносит информацию с выходов сумматора 26 в регистры 17 и 18, обнуляет регистр 15, делитель 14, триггер 19 и проходит через элемент ИЛИ 22 на выход умножителя. Следующее срабатывание схемы 10 сравнения происходит тогда, когда число в регистре 20 равно числу, запи санному в делителе 4 и счетчике 23, т.е.- через время равное после рассмотренной записи числа в регистр Г вхтах 24, где N КГ округленное до ближайшего большего целого числа выражение , N - емкость счетчика 23 (для н ашего примера 6Х.1Т.01Х Ъ . TO-K irl при Г1 3 М Так как время т больше максимального периодавходных импульсов то за это время по крайней мере хотя бы один импульс переносит число из делителя 4 и счетчика 23 в регистр 24 и вызывает установку триггера 28 в О. Каждый импульс переноса информа-ции в регистр 20 вызывает установку в 1 триггера 21 и тем самым разрешает следующему тактовому импульсу пройти через схему И 9 и перенести информацию из регистра 24 в регистр 27. С другой стороны каждьй импульс с выхода схемы 10 сравнения появляется через время Т после поступления импульса с выхода тактирующего блока 7 на вход разрешения записи регистра 24 и вход установки в О триггера 28 Таким образом, период импульсов на выходе схемы 10 сравнения кодов равен периоду входных импульсов с задержкой на время Т. При этом число, записанное в регистре 20 в момент поступления какого-либо задержанного импульса с выхода схемы 10, равно числу, записанному в регистр 24 в момент поступления соответствующего ему входного импульса с выхода тактирующего блока 7, а число, зафиксированное в этот момент в регистре 27, равно числу, записанному в ре- f гистр 24 следующим входньм импульсом с выхода блока 7. Иными словами, если входной j импульс поступил в момент .j , то соответствующий ему задержанный импульс поступает с выхода схемы 10 сравнения в момент tj. ig,(+T, так как именно в этот моментчисло, занесенное в регистр 24 в момент , снова появляется на выходах делителя 4 и счетчика 23 после их переполнения. В этот же момент -tjj в регистре 27 находится число, которое было в делителе 4 и счетчике 23 в момент tbx.Cj+f) поступления следующего (j+1)-ro входного импульса. Таким образом, к моменту i jj на входы сумматора 26 поступают прямой код числа, записанного в регистре 27, и дополнитель числа, записанного в регистре 20, который сформировывает преобразователь 25 кода. В результате на выходе сумматора 26 формирует код Nj разности этих чисел. Это и есть код j-ro периода .входного сигнала.в момент - ладшие. m разрядов кода N; переносятся в регистр 17, а старшие разрядов регистр 18. В этот же момент обнуляются регистр 15, счетчик 11, дели ь 14, триггер 19. Таким образом, в регистрах 17 и 18 фиксируются соответственно дробная и целая части ° деления количества тактовых импуль сов (Ny), поступающих на вход делителя 4 за j-й период входного сигнала, на коэффициент К. В следующий отрезок времени. Равный Т, работа описанной части умножителя происходит аналогично. -.....-.гчт-,„„ „ , В течение задержанного j-го периода результат N., записанный в регистре 18, сравнивается посредством схемы 12 сравнения с текущим значением числа импульсов, сосчитанных счетчи о 11. В момент совпадения кодов на входах схемы 12 сравнения на его выходе формируется импульс, который сбрасывает счетчик t1, и через эле 13 элемент ИЛИ 22 проходит выход умножителя. Если при этом элемент И 2 открыт в течение всего периода умножаемой частоты, то импульсы на выходе схемы 12 сравнения появляются через интервалы времени появляются через интерн .-И.,,™е 4 целая часть отношения. В результате на выходе умножителя каждый Р-й импульс появляется с опережением (ошибкой) на время tp

И1

i i

дробная часть

.T.p

где 1 I-

отношения.

Уменьшение данной ошибки статического характера при.работе умножителя происходит следующим образом. Код

остатка лМ; от деления N; на К с выN.

хода регистра 17 поступает на первый вход сумматора 16. По приходу первого импульса с выхода схемы 12 сравнения этот код с сумматора 16 переписывается в регистр 15, и с выхода регистра 15 подается на второй вход сумматора 16. Таким образом, в течение периода умножаемой частоты сумматором 16 производится сложение кодов остатков, причем результат увеличивается на uN; с приходом каждого импульса с выхода схемы 12. Если текущее значение суммы остатков равно или превышает число К, то на выходе старшего разряда сумматора 16 формируется сигнал логической 1. Этот сигнал с выхода сумматора 16 поступает на информационный вход блока 3,. приведенного в исходное состояние импульсом со схемы Т2 и управляемого импульсами генератора 1. Блок 3 вырабатывает импульс длительностью Т, который закрьшает на время Т элемент И 2, запрещая прохождение на вход счетчика 11 одного импульса с выхода генератора 1.

В результате благодаря тому, что для формирования выходных импульсов в течение j-го периода входного сигнала используется не код (j-1)-ro периода (как в известном устройстве) а значение кода j-ro периода, исключается динамическая ошибка умножителя. Ошибка умножителя практически определяется ошибкой статического характера, не превьш1ающей т .

Дпя синхронизации и привязки последнего выходного импульса к концу периода умножаемой частоты импульсы выхода схемы 12 сравнения поступают на счетный вход делителя 14 с коэффициентом (К-1). Если на счетньй вход делителя 14 успевает поступить (К-1) импульсов, а период умножаемой частоты еще не окончился, то сигнал с выхода делителя 14 закрывает через триггер 19 элемент И 13 и прекращает подачу импульсов на выход умножителя I

Таким образом, предлагаемый умножитель позволяет по сравнению с известным уменьшить неравномерность следования импульсов выходной послещовательности при большой скорости изменения периода входного сигнала и исключить динамическую ошибку умножения частоты.

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-03-11—Подача