Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных сис- тема Хд а также в терминальной аппаратуре.

Целью изобретения является повышение быстродействия устройства.

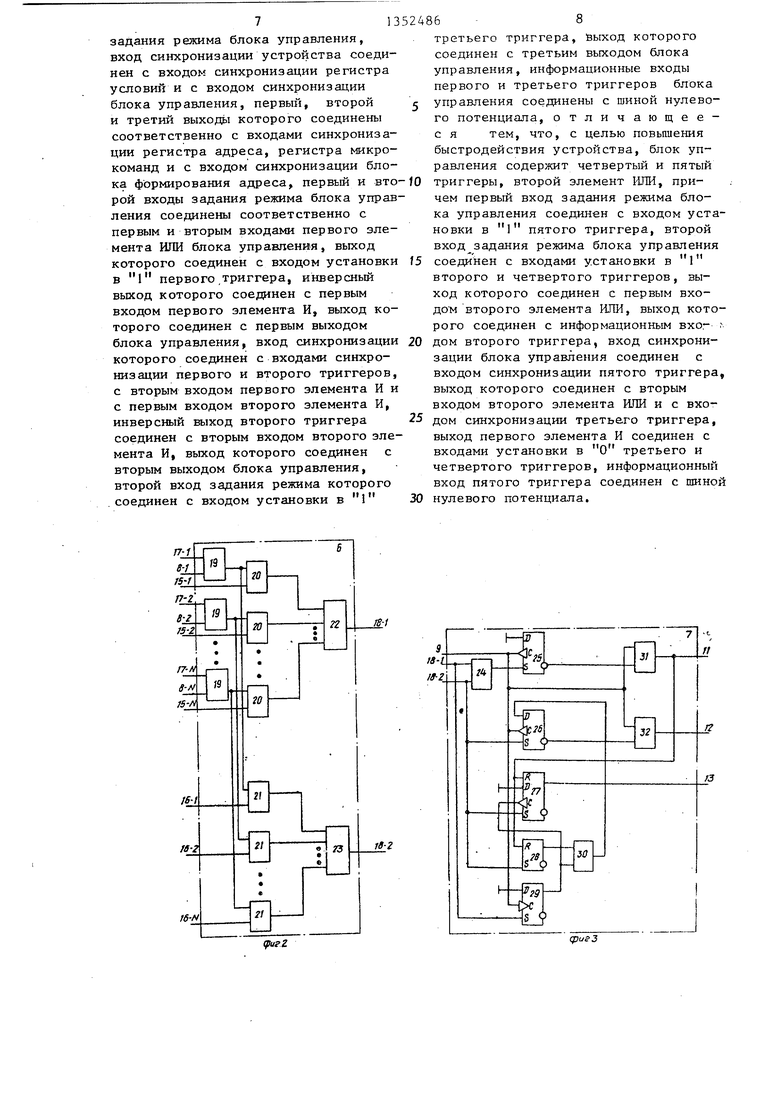

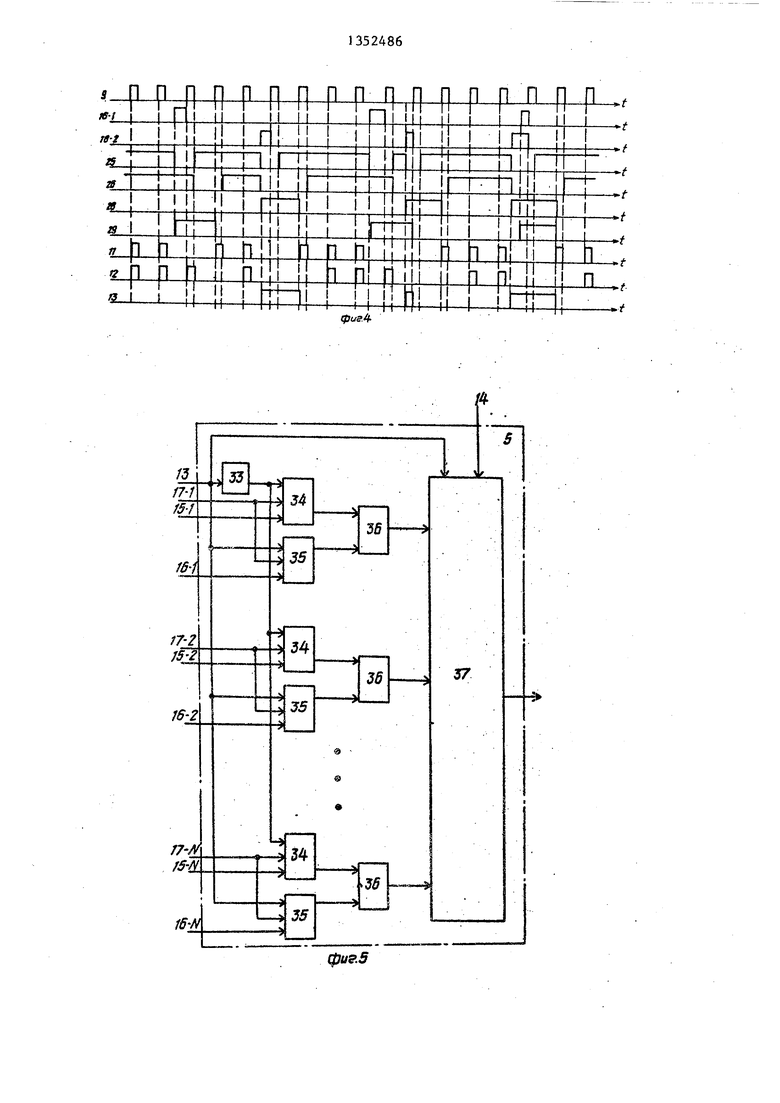

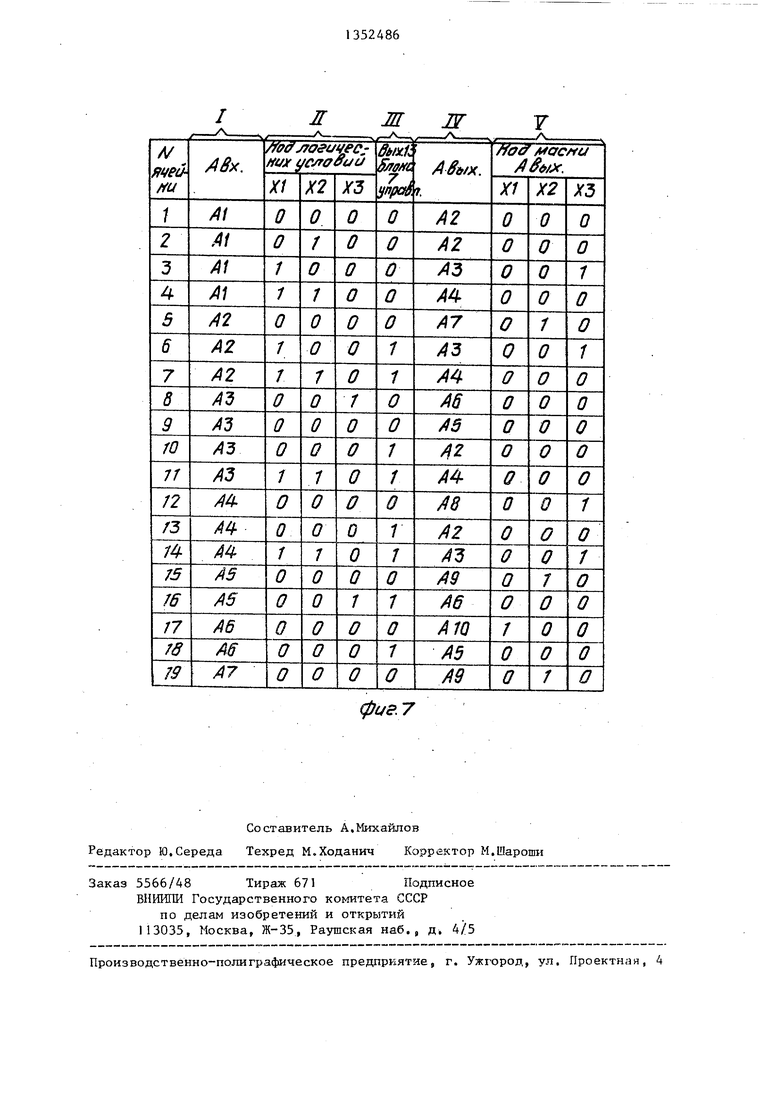

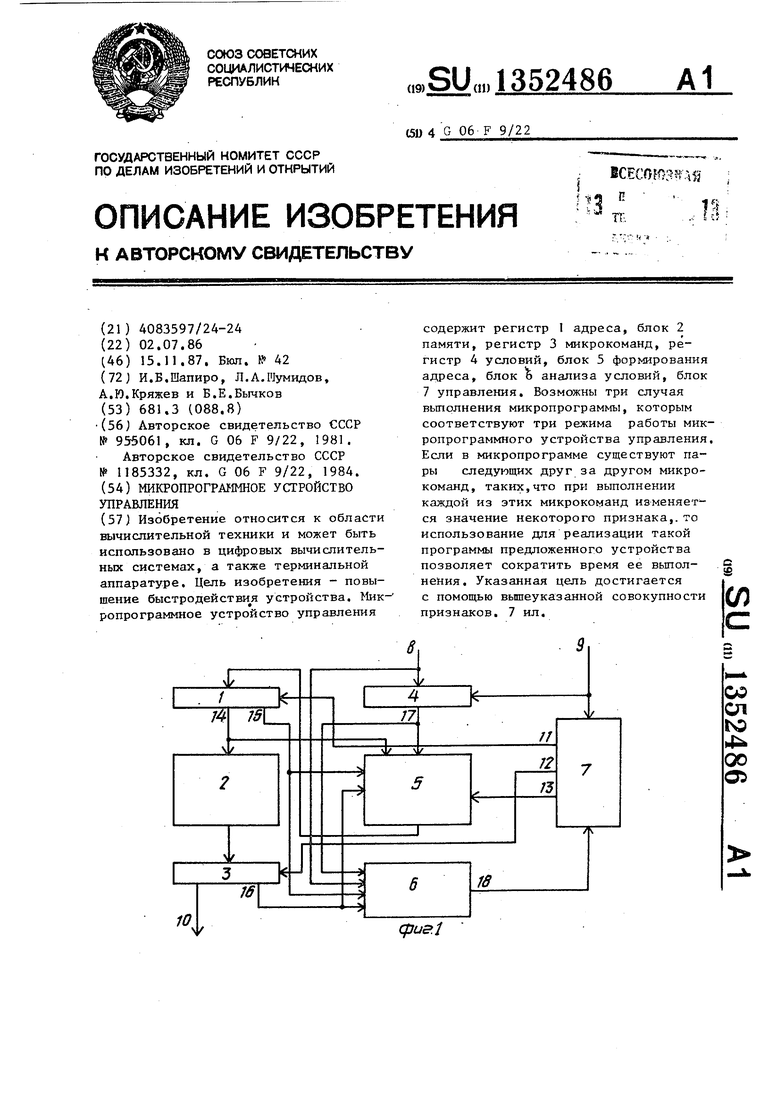

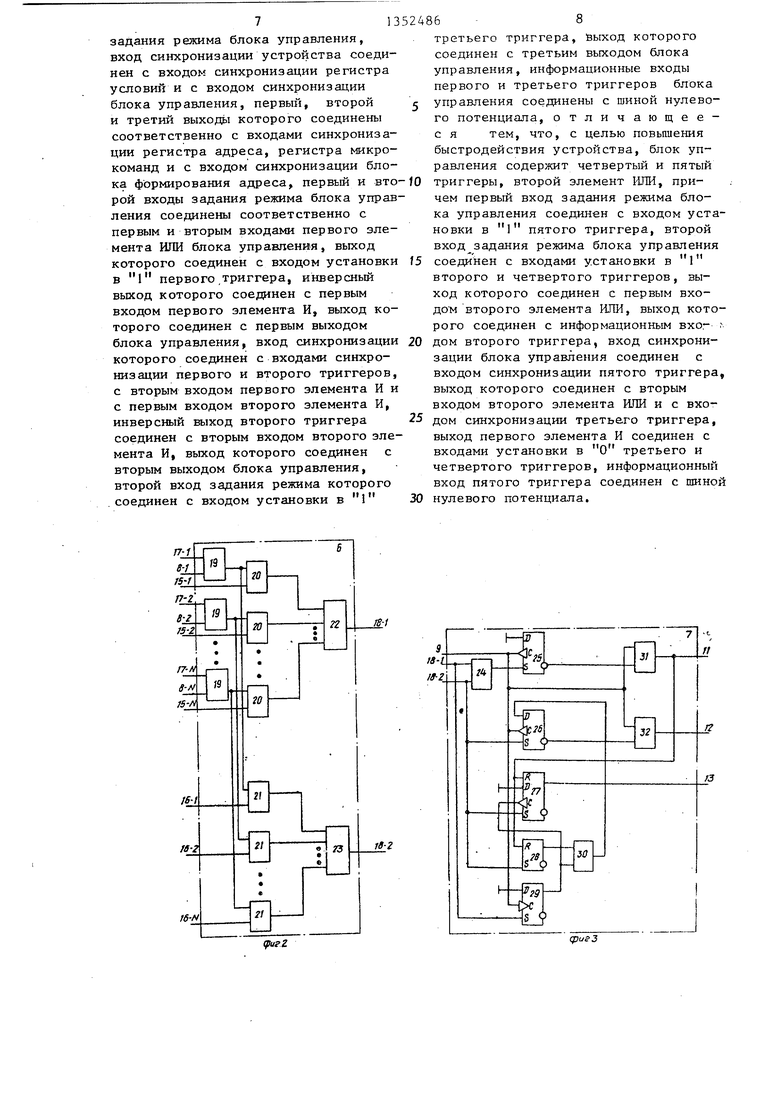

На фиг.1 изображена функциональная схема микропрограммного устройства управления; на фиг.2 - функциональная схема блока анализа условий; на фиг.З - функциональная схема блока управления; на фиг,4 - временные диаграммы работы блока управления; на фиг,5 - функциональная схема блока формирования адреса; на фиг.6 - фрагмент граф-схемы микропрограммы, реализуемой предлагаемым устройством; на фиг.7 - таблица содержимого ассоциативного запоминаюп;его устройства, входящего в блок формирования адреса.

Устройство содержит регистр I адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, регистр 4 условий, блок 5 формирования адреса, блок 6 анализа условий, блок 7 управления, группу 8 входов условий, синх- ровход 9, выход 10, первый 11, второй 12 и третий 13 выходы блока 7 управления, первую 14 и вторую 15 группу выходов регистра 1 адреса, группу 16 выходов поля анализируемых уоювий регистра 3 микрокоманд, группу 17 выходов регистра 4 условий и первый 18-1 и второй 18-2 выходы блока 6 анализа.

Блок 6 (фиг,2} анализа условий содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ i 9, первую и вторую группы элементов И 20 и 21 и два элемента ИЛИ 22 и 23.

Блок 7 управления (фиг.З) содержит первьй элемент ИЛИ 24, первый 25, второй 26, третий 27, четвертый 2в и пятый 29 триггеры, второй элемент ИЛИ 30, первый 3 и второй 32 элементы И.

Блок 5 формирования адреса

при обнаружении совпадения со сл вом, записанным в ассоциативной час ти, соответствуюш;ий индикатор слова устанавливается в состояние чтение слова, записанного в информа ционной части, индикатор которого установлен в состояние О,

Работу микропрограммного устрой10 ства управления рассмотрим на приме ре вьшолнения фрагмента микропрогра мы, граф-с: jMa которой приведена на фиг.6. Каждую МК микропрогаммы будем идентифицировать адресом, по

15 которому она записана в блоке 2 памяти. Размещение фрагмента микропрограммы в АП 37 приведено на фиг.7,

Путь в первом такте работы уст20 ройств а выполняется в МК А (в регистре 3 микрокоманды находятся коды операции и маски МК, записанной в блоке 2 памяти по адресу А ), счи тывается МК А, (в регистре 1 адре25 са «аходится код адреса А ), а в

регистре 4 условий записан код усло вия 101, сформированный по значения логических условий, поступивших на вход 8 устройства в предьщущем такт

30 В этом случае при отсутствии 1 на выходе 13 блока 7 управления на выходе группы элементов ИЛИ 36 форми руется код 001.

При этом в АП 37 вырабатывается

25 сигнал совпадения .с содержанием ассоциативной части 8-й ячейки (фиг,7 и содержимое информационной части 8-й ячейки АП 37 поступает на выход блока 5 формирова:ния адреса. Таким

40 образом, в первом такте в блоке 5 формирования адреса формируется код адреса и код маски МК А,.

Возможны три спучая выполнения микропрограммы, которым соответству

45 ет три режима работы микропрограммн го устройства управления,

Первьй режим соответствует случа когда в течение такта работы устрой ства не происходит изменения значе(фнг.5) содержит элемент НЕ 33, пер- gQ ний логических усповий, влияющих ня вую группу элементов И 34, вторую выбор пути выполнения микропрограм- группу элементов И 35, группу элементов ИЛИ 36 и ассоциативную памят-ь

(АП) 37. Ассоциативная память состоит из двух частей: ассоциативной и информационной„

Алгоритм работы АП следующий: поиск в ассоциативной части по содержимому поискового входа;

55

мы: из МК., выполняемой в данном такт и МК, считываемой в данном такте из блока 2 памяти.

Второй режим соответствует случа когда в течение текущего такта изме няются значения логических условий, влияющих на выбор пути вьтолнения мг-1кропрограммы из МК, считываемой в

при обнаружении совпадения со словом, записанным в ассоциативной части, соответствуюш;ий индикатор слова устанавливается в состояние чтение слова, записанного в информационной части, индикатор которого установлен в состояние О,

Работу микропрограммного устройства управления рассмотрим на примере вьшолнения фрагмента микропрограммы, граф-с: jMa которой приведена на фиг.6. Каждую МК микропрогаммы будем идентифицировать адресом, по

которому она записана в блоке 2 памяти. Размещение фрагмента микропрограммы в АП 37 приведено на фиг.7,

Путь в первом такте работы устройств а выполняется в МК А (в регистре 3 микрокоманды находятся коды операции и маски МК, записанной в блоке 2 памяти по адресу А ), счи- тывается МК А, (в регистре 1 адреса «аходится код адреса А ), а в

регистре 4 условий записан код условия 101, сформированный по значениям логических условий, поступивших на вход 8 устройства в предьщущем такте.

В этом случае при отсутствии 1 на выходе 13 блока 7 управления на выходе группы элементов ИЛИ 36 формируется код 001.

При этом в АП 37 вырабатывается

сигнал совпадения .с содержанием ассоциативной части 8-й ячейки (фиг,7 и содержимое информационной части 8-й ячейки АП 37 поступает на выход блока 5 формирова:ния адреса. Таким

образом, в первом такте в блоке 5 формирования адреса формируется код адреса и код маски МК А,.

Возможны три спучая выполнения микропрограммы, которым соответствует три режима работы микропрограммного устройства управления,

Первьй режим соответствует случаю, когда в течение такта работы устройства не происходит изменения значений логических усповий, влияющих ня выбор пути выполнения микропрограм-

мы: из МК., выполняемой в данном такте и МК, считываемой в данном такте из блока 2 памяти.

Второй режим соответствует случаю, когда в течение текущего такта изменяются значения логических условий, влияющих на выбор пути вьтолнения мг-1кропрограммы из МК, считываемой в

352486 МК

Aj считывается из блока 2 памят

fO

15

данном такте из блока 2 памяти, а значения логических условий, влияющих на выбор пути вьтолнения микро- программы из МК, которая выполняется Б текущем такте (код операционной части которой присутствует на выходе 10 устройства) остаются неизменными.

Третий режим соответствует случаю, когда в текущем такте работы происходит изменение значений логических условий, влияющих на выбор пути выполнения микропрограммы из МК, которая выполняется в текущем такте.

Реализация первого и третьего режимов микропрограммного устройства управления осуществляется так же, как в устройстве прототипе.

Для нашего примера условием работы устройства в первом режиме является неизменность значений логических условий ,, в течение первого такта. При этом на выходе блока 6 анализа условий сохраняется код 00 и в следующем такте на вькодах 11 и 12 блока 7 управления вырабатывается синхроим-,;. пульс. Во втором такте на выход 10 устройства поступает операционная часть МК Aj, из блока 2 памяти микрокоманд считывается МК А,, а на выхо- де блока 5 формирования адреса формируется адрес .

Как и в прототипе в первом режиме работы устройства обеспечивается полное совмещение процессов выполне- 35 реса вьфабатывается адрес Ад. ния, считывания и формирования адре- Таким образом, в третьем режиме

20

25

Это происходит следую цим образом. На выходе блока 6 анализа условий вырабатывается код 10 (фиг,2). Во втором и третьем тактах работы уст ройства на синхровход регистра 3 м рокоманд с выхода 12 блока 7 управ ния не поступают синхроимпульсы, в втором такте работы синхроимпульсы с выхода 11 блока 7 управления не поступают также на синхровход реги ра 1 адреса, кроме того во втором такте работы устройства на выходе блока. 7 управления формируется сиг нал логической 1 (фиг , 4). При эт во втором такте на вход блока 5 формирования адреса поступают: код адреса код условия 001; сигнал 1 с выхода 13 блока 7 управления

В этом случае на выходе группы элементов {ШИ -Зб формируется код 00...О, а на выходе блока 5 формиро вания адреса - коды адреса и маски МК Aj (-фиг, 7). В третьем такте МК AJ считывается из блока 2 памяти, в блоке 5 формирования адреса вырабатывается адрес А, (фиг, 7), а на выходе 10 устройства будет по-преж нему находиться код операционной части МК Af, В четвертом такте на выход 10 устройства поступит код операционной части МК А.,. При этом из блока 2 памяти будет считываться МК А, а в блоке 5 формирования адса МК, При этом на выполнение двух следующих друг за другом МК (А, AJ).затрачивается два такта.

При выполнении линейньрс 55частков микропрограммы устройство всегда работает в первом режиме, поскольку в этом случае логические условия не влияют на траекторию микропрограммы

В нашем примере устройство переходит в третий режим работы, если в течение первого такта изменились значения X., или Х, Пусть в первом такте меняется значение X., , В этом случае значения логических условий в конце первого такта будут следующие: X, 0;Xi , При этихзначениях логических условий после МК А, в микропрограмме следуе МК Aj, Поэтому в течение второго такта работы устройства в блоке 5 формирования адреса вьфабатывается адрес Aj, а в течение третьего такт

52486 МК

Aj считывается из блока 2 памяти,

fO

15

,

.

35 реса вьфабатывается адрес Ад. Таким образом, в третьем режиме

20

25

Это происходит следую цим образом. На выходе блока 6 анализа условий вырабатывается код 10 (фиг,2). Во втором и третьем тактах работы устройства на синхровход регистра 3 микрокоманд с выхода 12 блока 7 управления не поступают синхроимпульсы, во втором такте работы синхроимпульсы с выхода 11 блока 7 управления не поступают также на синхровход регистра 1 адреса, кроме того во втором такте работы устройства на выходе 13 блока. 7 управления формируется сигнал логической 1 (фиг , 4). При этом во втором такте на вход блока 5 формирования адреса поступают: код адреса код условия 001; сигнал 1 с выхода 13 блока 7 управления,

В этом случае на выходе группы элементов {ШИ -Зб формируется код 00...О, а на выходе блока 5 формирования адреса - коды адреса и маски МК Aj (-фиг, 7). В третьем такте МК AJ считывается из блока 2 памяти, в блоке 5 формирования адреса вырабатывается адрес А, (фиг, 7), а на выходе 10 устройства будет по-преж нему находиться код операционной части МК Af, В четвертом такте на выход 10 устройства поступит код операционной части МК А.,. При этом из блока 2 памяти будет считываться МК А, а в блоке 5 формирования ад0

5

0

5

работы на выполнение двух следующих друг за другом МК А, и А) затрачивается четыре такта (два дополнительных такта ).

Рассмотрим работу устройства при реализации второго режима,

В нашем примере устройство переходит во второй режим работы, если в течение первого такта значения логических условий X, и Х остаются неизмененными (Х., 1, Х 0), а значения Xj меняются (Х О),

В этом случае после МК Aj в микропрограмме должна выполняться МК AJ.. Поэтому во втором такте работы устройства в блоке 5 формирования адреса должен быть сформирован адрес А5, Это происходит следующим образом,

На выходе 18 блока 6 анализа условий вырабатывается код 01 (фиг,2). При атом во втором такте с выхода 11 блока 7 управления на синхровход

регистра 1 адреса не поступает синхроимпульс (фиг.4), На вход блока 5 формировлния адреса поступают код адреса А J код условия 100, сигнал логическог о О с выхода 13 блока 7 управления, В этом случае на выходах элементов ИЛИ формируется код 000,. а на выходе блока 5 формирования адреса - коды адреса и маски МК А (фиг, 7). Синхроимпульс, поступающий в начале второго такта на синхро- вход регистра 3 микрокоманд, осуществляет запись следующей по микропрограмме МК.

Таким образом, в регистре 1 адреса во втором такте по-прежнему находится код адреса А, а в регистре 3 микрокоманд появляются коды операции и маски МК АЗ.

Дальнейшая работа микропрограммного устройства зависит от того, произойдет ли во втором такте изменение значения логического условия X, под действием вырабатываемого в этом такте на выходе 10 устройства кода операции МК А,

Если значения Xg не меняются (Х., 0), то в устройстве сохраняется второй режим ;аботы и в третьем 30 ройства соединены с информационными

чакте работы на синхровход регистра 1 адреса поступает синхроимпульс, в то время как на сикхровход регист- ;ш 3 микрокома г1д с выхода 12 блока 7

управления синхроимпульс не поступа- og инфррмационных входов блока анализа ет. При этом в третьем такте работы условий и с первой группой информа- на выходе 10 устройства вырабатывается код операционной части МК А,, из

блока 2

5

памяти йудет считываться МК АС, а в блоке 5 формирования адреса вырабатывается адрес МК Ад и ai:алогично тому как это происходит 3 прототипе во втором ренсиме работы устройства на выполнение двух следующих друг за другом МК А, А затрачивается три такта.

Если под действием кода операции МК А значение признака Х меняется (Х, 1)5 устройство переходит в третий режим работы. Однако в этом случае н а выходе 1 3 блока 7 управления в третьем такте вырабатывается сигнал логического ,0 (фиг.4), При этом в третьем такте на вход блока 5 формирования адреса поступает: код адреса А, код условия 101, .сигнал логическог О О с выхода 13 блока 7. На выходах элементов ИЛИ 36 формируется код 001, а на выходе блока 5 .

ционных входов блока формирования адреса, выход которого соединен с информационным входом регистра адре40 са, первая группа выходов которого соединена с второй группой информационных входов блока формирования адреса и с адресньтм входом блока памяти микрокоманд, выход которого

45 соединен с информационным входом регистра микрокоманд, выход поля кикр операций которого соединен с выходо микроопераций устройства, вторая группа выходов регистра адреса .соединена с первыми группами входов ло гических условий, блоков формирования адреса и анализа условий, выход поля кода условий регистра микрокоманд соединен с вторыми группами

pjg входов логических условий блоков фор мифования адреса и анализа условий, перьъ1Й и второй выходы группы блока анализа условий, соединены соответ- CTseHHq с первым и вторым входами

50

формирования ,адреса - коды адреса и маски МК А (фиг,7), которые в четвертом такте по синхросигналу записываются в регистр 1 адреса. При этом в третьем и четвертом тактах на выходах 10 устройства сохраняется код операции МК А, В четвертом такте на вход блока 5 формирования адреса поступает: код адреса А, код условия 101, сигнал логического О с выхода 3 блока 7, На выходе блока 5 формирования адреса будет вырабатываться

адрес МК А

10

(фиг,7). Таким обра15 зом, на выполнение следующих друг

за другом МК А,

и А, потребуется в

этом случае четыре такта.

Формула изобретения

Микропрограммное устройство уп рав- ления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, блок анализа условий, регистр 25 условий, 6ciiOK формирования адреса, блок управления, который содержит первый,,второй и третий триггеры, первый элемент ИЛИ, первый и второй элементы И, причем входы условий уствходами регистра условий и с первой группой информационных входов блока анализа условий, выходы регистра условий соединены с второй группой

нфррмационных входов блока анализа словий и с первой группой информа-

ционных входов блока формирования адреса, выход которого соединен с информационным входом регистра адреса, первая группа выходов которого соединена с второй группой информационных входов блока формирования адреса и с адресньтм входом блока памяти микрокоманд, выход которого

соединен с информационным входом регистра микрокоманд, выход поля кикро- операций которого соединен с выходом микроопераций устройства, вторая группа выходов регистра адреса .соединена с первыми группами входов логических условий, блоков формирования адреса и анализа условий, выход поля кода условий регистра микрокоманд соединен с вторыми группами

входов логических условий блоков фор- мифования адреса и анализа условий, перьъ1Й и второй выходы группы блока анализа условий, соединены соответ- CTseHHq с первым и вторым входами

задания режима блока управления, вход синхронизации устройства соединен с входом синхронизации регистра условий и с входом синхронизации блока управления, первый, второй и третий выходь которого соединены соответственно с входами синхронизации регистра адреса, регистра микрокоманд и с входом синхронизации блока формирования адреса, первый и второй входы задания режима блока управления соединены соответственно с первым и вторым входами первого элемента ИЛИ блока управления, выход которого соединен с входом установки в 1 первого.триггера, инверсный выход которого соединен с первым входом первого элемента И, выход которого соединен с первым выходом блока управления, вход синхронизации которого соединен с входами синхронизации первого и второго триггеров, с вторым входом первого элемента И и с первым входом второго элемента И, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход которого соединен с вторым выходом блока управления, второй вход задания режима которого соединен с входом установки в 1

третьего триггера. Выход которого соединен с третьим выходом блока управления, информационные входы первого и третьего триггеров блока управления соединены с шиной нулевого потенциала, отличающее- с я тем, что, с целью повьпиения быстродействия устройства, блок управления содержит четвертый и пятый триггеры, второй элемент ИЛИ, причем первый вход задания режима блока управления соединен с входом установки в 1 пятого триггера, второй

вход задания режима блока управления

и 1 It

соединен с входами установки в 1 второго и четвертого триггеров, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с информационным вхо- дом второго триггера, вход синхронизации блока управления соединен с входом синхронизации пятого триггера, выход которого соединен с вторым входом второго элемента ИЛИ и с входом синхронизации третьего триггера, выход первого элемента И соединен с входами установки в О третьего и четвертого триггеров, информационный вход пятого триггера соединен с шиной

нулевого потенциала.

п-1

pufZ

Р PJ П Р П П Р Р

I I Г I и I Mill I

ft

I I

II I

I I

V ir

. Г I I ; г т т

I I 11

Ш

P I n П

npTp

11 I I

Mill

444

-ff-f-HфигЛ

WH

Р Р J П Р

f -

y

bJ

II

т т

йttr

l

№

4

Mt

л

-Hffi

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство управления | 1981 |

|

SU964641A1 |

фигЗ

« X

5$

«Э)

Cs Ч

К

/

Ж

м ж

фие.7

Авторы

Даты

1987-11-15—Публикация

1986-07-02—Подача