третий регистр микрокоманд, третий формирователь адреса, первый и вто-; рой блоки ассоциативной памяти, коммутатор логических условий и третий коммутатор кода операций, причем первый и второй .входы логических условий устройства соединены соответственно с первым и вторым информационньми входами коммутатора логических условий, выход которого соединен с первым входом третьего формирователя адреса, выход третьего формирователя адреса соединен с первьм информационным входом третьего регистра адреса, выход которого соединен с входом третьего блока памяти микрокоманд, выход третьего блока памяти микрокоманд соединен с информационным входом третьего регистра микрокоманд, выходы немодифицируемых разрядов адреса, модифицируемого разряда адреса и кода логических условий которого соединены соответственно с вторым информационным входом регисра адреса, вторым и третьим входами третьего формирователя адреса, первьй выход регистра кода операции соединен с входом первого блока ассоциативной памяти и первыми информационными входами первого, второго и третьего коммутаторов кода операции,, выходы которых соединены с третьими информационными входами первого, второго и третьего регистров адреса соответственно, вькод одновибратора соединен с вторым входом первого элемента ИЛИ, второй выход регистра кода операции соединен с входом второго блока ассоциативной памяти, вторыми информационньми входами первого, второго и третьего коммутаторов кода операции, выходы второго и третьего элементов ИЛИ соединены с первыми входами соответственно четвертого и пятого элементов И, выходы которых соединены с едничными входами первого и второго триггеров управления соответственно, первый выход генератора импульсов соединен с вторьми входами четвертог и пятого элементов И и первыми входами шестого, седьмого и восьмого элементов И, выходы которьк соединены с входами синхронизации первого, второго и третьего регистров адреса соответственно, второй выход генератора тактовых импульсов соединен с первыми входами второго, третьего и девятого элементов И, выход которого соединен с входами синхронизации третьего регистра микрокоманд, выход микрбопераций первого регистра микрокоманд соединен с первым и вторым информационными входами первого коммутатора микроопераций, группа выходов которого является первьм выходом микроопераций устройства, выход микроопераций второго регистра микрокоманд соединен с первым и вторым информационными входами. второго коммутатора микроопераций, группа выходов которого является вторым выходом микроопераций устройства, выход микроопераций третьего регистра микрокоманд соединен с третьими информационными входами второго коммутатора и первого коммутатора микроопераций, выход конца операции группы, выходов которого соединен с нулевым входом первоготриггера управления , выход конца операции группы выходов второго коммутатора микроопераций соединен с нулевым входом второго триггера управления, нулеВ1ОЙ выход которого соединен с вторьм входом первого элемента И, первьй выход первого блоки ассоциативной памяти соединен с первыми управляю-щийи входами первого коммутатора кода операции и первого коммутатора микроопераций, первым входом элемента ЗИ-ИЖ и первыми входами второго и четвертого элементов ИЛИ, выход которого соединен с вторыми входами второго и шестого элементов И, первый выход второго блока ассоциативной памяти соединен с вторыми входами второго, четвертого элементов ИЛИ и элемента ЗИ-Ш1И и вторыми упрввл ющими входами первого коммутатора микроопераций и первого коммутатора кода операции, выход которого соединен с третьим информационным входом пер-; вого регистра адреса, вто1я 1е выходы первого и второго блоков ассоциативной памяти соединены соответственно с первьм и вторым управляющими входами коммутатора логических условий, третий выход первого блока ассоциативной памяти соединен с первьв4 входом третьего элемента ИЛИ, с первыми управляющими входами второго коммутатора кода операции и второго коммутатора микроопераций, третьим входом элемента ЗИ-ШВД и первьв4 входом пятого элемента ИЛИ, выход которого соединен с вторьми входами третьего и седьмого элементов. И, третий выход

второго блока ассоциативной памяти соединен с четвертым входом элемента ЗИ-ИЛИ, вторыми входами третьего и пятого элементов ИЛИ и вторыми управляющими входами второго коммутатора микроопераций и второго коммутатора кода операции, выход которого соединен с третьим информационным входом второго регистра адреса, второй ВЫХОД первого блока ассоциативной памяти соединен с первым управляющим входом третьего коммутатора адреса, пятым входом элемента ЗИ-ИЛИ, третьим управляющим входом первого коммутатора микроопераций, третьим входом второго элемента ИЛИ и первым входом шестого элемента ИЛИ, выход которого соединен с вторыми входами восьмого и девятого элементов И, второй выход второг блока ассоциативной памяти соединен с третьим входом третьего элемента ИЛИ, вторым входом шестого элемента ИЛИ, шестым входом элемента ЗИ-ИЛИ, третьим управляющим- входом второго коммутатора микроопераций и вторым управляющим входом третьего коммутатора кода операции, выход которого соединен с третьим информационным входом третьего регистра адреса, первый - третий выходы первого и вт.орого преобразователей кода операции в начальный адрес соединены с группой управляющих входов блока коммутации сигналов обнуления, выходы конца операции групп выходов первого и второго коммутаторов микроопераций соединены с групцой информационных входов блока коммутации сигналов обнуления, первый и второй выходы группы выходов которого соединены с первым и вторым установочньми входами регистра кода операции соответственно.

2. Устройство по п. 1, о т л ичающееся тем, что блок коммутации сигналов обнуления содержит первый и второй коммутаторы, первый и второй элементы ИЛИ, первый и второй одновибраторы, причем первый и второй входы группы управляющих входов блока соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым управляющим входом первого коммутатора, третий и четвертый входы группы управляющих входов блока соединены соответственно с вторым управляющим входом первого и первым управляющим входом второго комму таторов, выходы которых через первый и второй одновибраторы соединены соответственно с первым и вторым выходами группы выходов блока, пятый и шестой входы группы управляющих входов блока соединены соответственно с первым и вторьм входами второго элемента ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, первый вход группы информационных входов блока соединен с первьми информационными входами первого и второго коммутаторов, второй вход группы информационных входов блока соединен с вторыми информационными входами первого и второго коммутаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

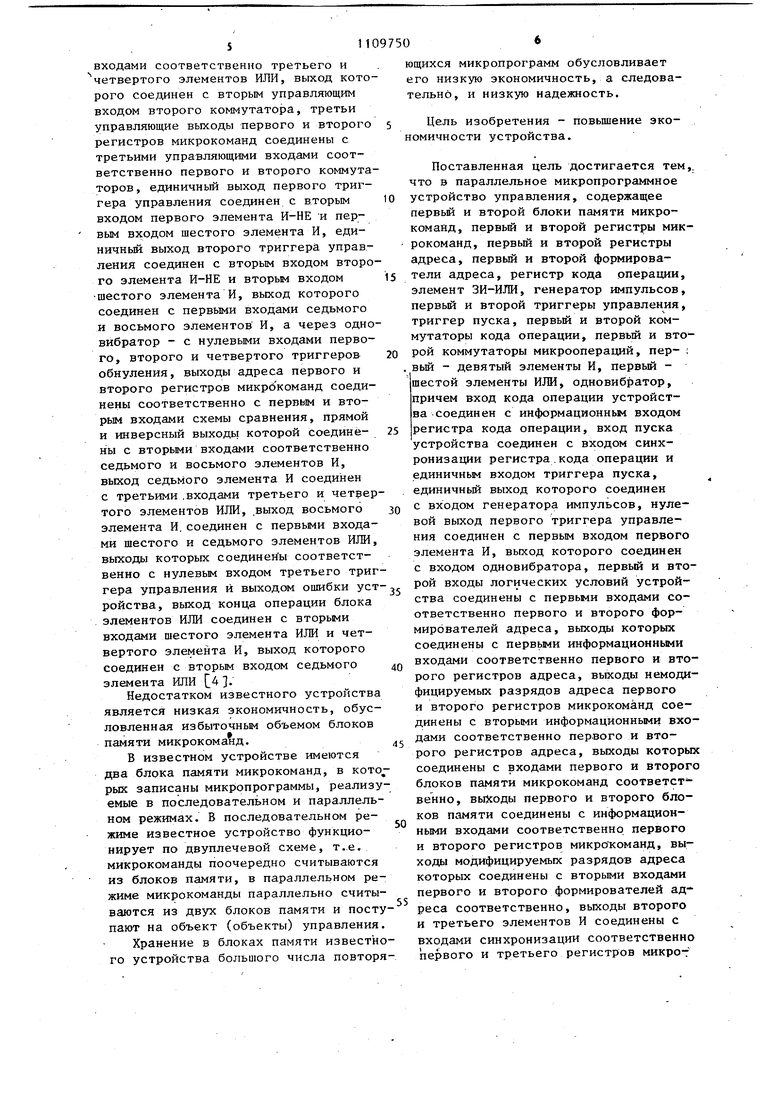

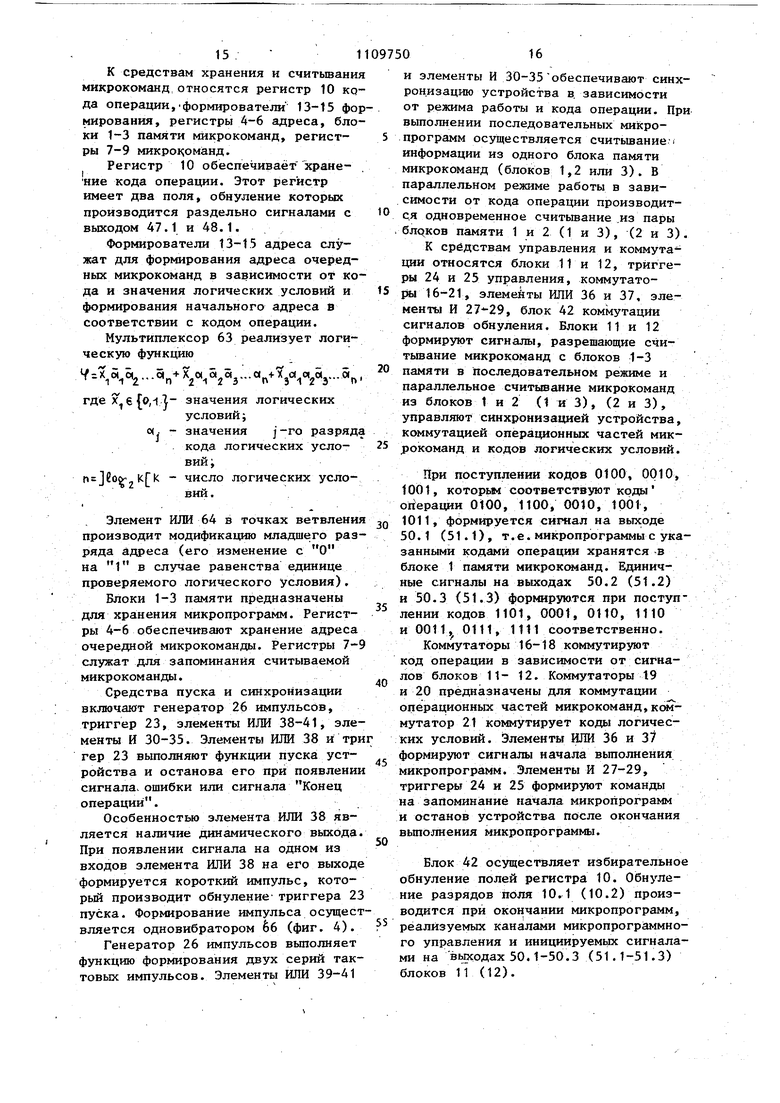

1. ПАРАЛЛЕЛЬНОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первьй и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, первый и второй регистры адреса, первый и второй формирователи адреса, регистр кода операции, элемент ЗИ-ИЛИ, генератор импульсов, первьй и второй триггеры управления, триггер пуска, первый и второй коммутаторы кода операции, первьй и второй коммутаторы микроопераций, первьй - девятый элементы И, первьй - шестой элементы ИЛИ, одновибратор, причем вход кода операции устройства соединен с информационным входом регистра кода операции, вход пуска устройства соединен с входом синхронизации регистра кода операции и единичным входом триггера пуска, единичный выход которого соединен с входом генератора импульсов, нулевой выход первого триггера управления соединен с первым входом первого элемента И, выход которого соединен с входом одновибратора, первый и второй ходы логических условий устройства соединены с первыми входами соответственно первого и второго формирователей адреса, выходы которых соединены с первыми информационными входами соответственно первого и второго регистров адреса, выходы немодифицируемых разрядов адреса первого и второго регистров микрокоманд соединены с вторыми информационньии входами соответственно первого и второго регистров адреса, выходы которых соединены с входами первого и второго бйоков памяти микроксманд соответственно, выходы первого и второго блоков памяти соедине.иы с информационными входами соответ ственно первого и второго регистров микрокоманд, выходы модифицируемых разрядов адреса которых соединены с вторыми входами первого и второго формирователей адреса соответственно, выходы второго и третьего элеменСО тов И соединены с входами синхронизации соответственно первого и треСП тьего регистров микрокоманд, выходы кода логических условий которых соединены с третьими входами первого и второго формирователей адреса соответственно, выход формирователя сигнала ошибки соединен с выходом ошибки устройства и первым входемя первого элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, отличающееся тем, что, с целью повышения экономичности, в него введены третий блок памяти микрокоманд, третий регистр адреса, блок коммутации сигналов обнуления.

t

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке устройств управления параллельными процессами вычислительных и управляющих систем.

Известны микропрограммные устройства управления, содержащие первый и дторой блоки памяти микрокоманд, регистры микрокоманд и адреса, формирователи адреса, триггеры, элементы И l1 и 2.

Недостатками указанных устройств являются низкая производительность и узкая область применения, обусловленные их невозможностью управления параллельными процессами.

Известно микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первьй и второй регистры адреса, первый и второй коммутаторы, блок синхронизации, первый и второй триггеры управления, элементы.И, ИЛИ t3. Недостаток такого устройства низкая производительность, обусловг ленная отсутствием технических средств для управления параллельными процессами и перетактовкой схемы при последовательном выполнении двух четных (нечетных) микрокоманд. Наиболее близким к предлагаемому по технической сущности и достигаемо му результату является параллельное микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры.адреса, первьй и второй регистры микрокоманд, схему сравнения, первый - четвертьй коммутаторы, формирователь тактовьк импульсов, первьй и второй формирователи адреса первьй - пятьй триггеры управления, первый - восьмой злементы И, первыйседьмой элементы ШШ, первьй и второй элементы И-НЕ, одновибратор, бло элементов ИЛИ, причем вход логических условий устройства соединен с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первы ми входами соответственно первого и второго регистров адреса, вход кода операции устройства соединен с вторыми информационными входами первого и второго регистров адреса, вьк ды которых соединены с информационными входами соответственно первого и второго блоков памяти микрокоманд, выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно первого и второго регистров микрокоманд, первые управлякицие выходы первого и второго регист ров микрокоманд соединены с единичны ми входами соответственно первого и второго триггеров управления, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первьм и вторьм входами блока элементов ИЛИ, выход кото рого является выходом микроопераций устройства, выход адреса первого регистра микрокоманд соединен с первыми информацИонньми входами первого и второго коммутаторов, выход адреса второго регистра микрокоманд соединен с вторыми информационными входами первого н второго коммутаторов, выходы которых соединены с вторыми информационнь1ми взводами соответственно первого и второго формирователей адреса, вход кода операции устройства через первый элемент.ИЛИ соединен с единичным входом третьего триггера управления, единичный выход которого соединен с входом формирователя тактовых импульсов, первьй выход формирователя, тактовых импульсов соединен с нулевыми входами триггеров полей микроопераций первого и второго регистров микрокоманд и с первыми информационными входами третьего и четвертого коммутаторов, выходы которых соединены с первыми входами соответственно первого и второго элементов И, второй и третий выходы формирователя тактовых импульсов соединены соответственно с вторыми и третьими информационными входами третьего и четвертого коммутаторов, единичньй выход четвертого триггера управления соединен с первыми управляющими входами третьего, четвертого коммутаторов, первьми входами третьего, четвертого, пятого элементов И и первого и второго элементов И-НЕ, выходы которых соединены с вторыми входами соответственно первого и второго элементов И, второй управляющий вькод первого регистра микрокоманд соединен с первыми входами второго и третьего элементов ИЛИ, выход которого соединен с первым управляющим входом первого коммутатора, второй управляющий выход второго регистра микрокоманд соединен с первым входом четвертого и вторьм вхо дом второго элементов ИЛИ, выход которого соединен с Т-входом пятого триггера управления единичньй выход пятого триггера управления соединен с вторыми управляющими входами третьего и четвертого коммутаторов, а нулевой выход соединен с третьими управляющими входами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров микрокоманд через пятьй элемент ИЖ соединены с единичным входом четвертого триггера управления, нулевой выход которого соединен с вторым управляющим входом первого коммутатора и первым управляющим входом второго коммутатора, нулевые вьрсоды первого и второго триггеров управления соединены с вторыми входами соответственно третьего и пятого элементов И, выходы которых соединены с вторыми входами соответственно третьего и четвертого элементов ИЛИ, выход кото рого соединен с вторым управляющим входом второго коммутатора, третьи управляющие выходы первого и второго регистров микрокоманд соединены с третьими управляющими входами соответственно первого и второго коммута торов, единичный выход первого триггера управления соединен с вторым входом первого элемента И-НЕ и первым входом шестого элемента И, единичньй выход второго триггера управления соединен с вторым входом второ го элемента И-НЕ и вторым входом шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И, а через одно вибратор - с нулевыми входами первого, второго и четвертого триггеров обнуления, выходы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверсный выходы которой соединены с вторьми входами соответственно седьмого и восьмого элементов И, выход седьмого элемента И соединен с третьими .входами третьего и четрер того элементов ИЛИ, .выход восьмого элемента И.соединен с первыми входами шестого и седьмого элементов ИЛИ, выходы которых соединены соответственно с нулевым входом третьего триг гера управления и выходом ошибки уст ройства, выход конца операции блока элементов ИЛИ соединен с вторыми входами шестого элемента ИЛИ и четвертого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ 4 . Недостатком известного устройства является низкая экономичность, обусловленная избыточным объемом блоков памяти микрокоманд. В известном устройстве имеются два блока памяти микрокоманд, в кото рых записаны микропрограммы, реализу емые в последовательном и параллель ном режимах. В последовательном режиме известное устройство функционирует по двуплечевой схеме, т..е. микрокоманды поочередно считываются из блоков памяти, в параллельном ре жиме микрокоманды параллельно считы ваются из двух блоков памяти и пост пают на объект (объекты) управления Хранение в блоках памяти известн го устройства большого числа повтор щихся микропрограмм обусловливает его низкую экономичность, а следовательно, и низкую надежность. Цель изобретения - повьшение экоомичности устройства. Поставленная цель достигается тем,. что в параллельное микропрограммное устройство управления, содержащее первьй и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, первьй и второй регистры адреса, первый и второй формирователи адреса, регистр кода операции, элемент ЗИ-ИЛИ, генератор импульсов, первый и второй триггеры управления, триггер пуска, первьй и второй коммутаторы кода операции, первьй и вто рой коммутаторы микроопераций, пер- ; вьй - девятый элементы И, первьй шестой элементы ИЛИ, одновибратор, причем вход кода операции устройства -соединен с информационным входом регистра кода операции, вход пуска устройства соединен с входом синхронизации регистра.кода операции и единичным входом триггера пуска, единичньй выход которого соединен с входом генератора импульсов, нулевой выход первого триггера управления соединен с первым входом первого элемента И, выход которого соединен с входом одновибратора, первьй и втоР° входы логических условий устроЙства соединены с первьми входами соответственно первого и второго формирователей адреса, выходы которых соединены с первьми информационными входами соответственно первого и второго регистров адреса, выходы немодифицируемых разрядов адреса первого и второго регистров микрокоманд соединены с вторыми информационными входами соответственно первого и второго регистров адреса, выходы которых соединены с входами первого и второго блоков памяти микрокоманд соответственно, выходы первого и второго блоков памяти соединены с информационными входами соответственно первого и второго регистров микрокоманд, выходы модифицируемых разрядов адреса которых соединены с вторыми входами первого и второго формирователей адреса соответственно, выходы второго и третьего элементов И соединены с входами синхронизации соответственно первого и третьего регистров микро-: 71 команд, выходы кода логических условий которых соединены с третьими вхо дами первого и. второго формирователе адреса, соответственно, выход формиро вателя сигнала ошибки соединен с выходом ошибки устройства и первым вхо первого элемента ИЛИ, выход кото рого .соединен с нулевм4 входом триггера пускаt дополнительно введены третий блок ми1фокоманд, треtwA регистр адреса, блок коммутации сигналов обнуления, третий регистр микрокоманд, третий формирователь адреса, первый и второй блоки ассоциативной памяти, коммутатор логичес ких условий и третий коммутатор кода операций, причем первь и второй входа логических условий устройства соединены соответственно с первым и BTopi информационными входами ком мутатора логических условий, выход которого соединен с первым входом третьего форкшрователя адреса, выход третьего фор шрователя адреса соединен с перв1Д4 информационным входом третьего регистра адреса, выход кото рого соединен с вводом третьего блока памяти микрокоманд, выход третьего блока памяти микрокоманд соединен с информационным входом третьего регистра микрокоманд, выходы немодифицируемых разрядов адреса, модифицируемого разряда адреса и кода логических условий которого соединены Соответственно с вторым информационным входом регистра адреса, вторым и третьим входами третьего формирователя адреса, первый выход регистра кода операции соединен с входом первого блока ассоциативной памяти и первыми информационными входами первого, второго и третьего коммутаторвв кода операции, выходы которых соединены с третьими информацион ными входами первого, второго и третьего регистров адреса соответственно, выход одновибратора соединен с вторым входом первого элемента ИЩ второй выход регистра кода операции соединен с входом второго блока ассоциативной памяти, вторьии информационными входами первого, второго и третьего коммутаторов кода операции, выходы второго и третьего элементов ИЛИ соединены с первыми входами соответственно четвертого и пятого элементов И, выходы которых соединены с единичньми входами первого 0 и второго триггеров управления соот ветственно, первый выход генератора импульсов соединен с вторь ш входами четвертого и пятого элементов И и первыми входами шестого, седьмого и восьмого элементов И, выходы которых соединены с входами синхронизации первого, второго и третьего регистров адреса соответственно, второй выход генератора тактовых импульсов соединен с первьми входами второго, третьего и девятого элементов И, выход которого соединен с входами синхронизации третьего регистра микроко-1 манд, выход микроопераций первого регистра микрокоманд соединен саперным и вторым информационными входами первого коммутатора микроопераций, группа выходов которого является первым выходом микроопераций устройства,выход микроопераций второго регистра микрокоманд соединен с первьм и вторым информационными входами второго коммутатора микроопераций, группа выходов которого является вторьм выходом микроопераций устройства, выход микроопераций третьего регистра микрокоманд соединен с третьими информационными входами второго коммутатора и первого коммутатора микроопераций, выход конца операции группы выходов которого соединен с нулевым входом первого триггера управления, вькод конца операции группы выходов второго коммутатора микроопераций соединен с нулевым входом второго триггера управления, нулевой выход которого соединен с вторым входом первого элемента И, первый выход первого блока ассоциативной памяти соединен с первыми управляющими входами пер- . вого коммутатора кода операции и первого комму7;атора микроопераций, первым входом элемента ЗИ-ИЛИ и первыми входами второго и четвертого элементов ИЛИ, выход которого соединен с вторыми входами второго и шестого элементов И, первьй выход второго i . . - . блока ассоциативной памяти соединен с вторьми входами второго и четвертого элементов ИЛИ и элемента ЗИ-ИПИ и вторьми управляющими входами первого коммутатора микроопераций и первого коммутатора кода операции, выход которого соединен с третьим информационным входом первого регистра адреса, вторые выходы первого и второго блоков ассоциативной па|мяти соединены сортветственно с первым и вторым управляющими входами коммутатора логических условий, третий выход первого блока ассоциативной памяти соединен с первым входом третьего элемента ИЛ, с первыми управляющими входами второго коммутатора кода операции и второго ком.. мутатора микроопераций, третьим входом элемента ЗИ-ИЛИ и первым входом пятого элемента ИШ, выход которого соединен с вторьми входами третьего и седьмого элементов И, третий выход второго блока ассоциативной памяти соединен с четвертым входом элемента ЗИ-ИЛИ, вторыми входами третьего и пятого элементов ИЛИ и вторыми управляющими входами второго коммута тора микроопераций и второго коммута тора-кода операции, выход которого соединен с третьим информационным входом второго регистра адреса, второй вьгход первого блока ассоциативной памяти соединен с первым управляющим входом третьего коммутатора адреса, пятым входом элемента ЗИ-ИЛИ третьим управляющим входом первого коммутатора микроопераций, третьим входом второго элемента ИЛИ и первым входом щестого элемента ИЛИ, выход которого соединен с вторыми входами восьмого и девятого элементов И, второй выход.второго блока ассоциативной памяти соединен с третьим входом третьего элемента ИЛИ, вторы входом шестого элемента ИЛИ, шестьм входом элемента ЗИ-ИЛИ третьим управляющим входом второго коммутатора микроопераций и вторым управляю:.щим входом третьего коммутатора кода, операции, выход которого соедине с третьим информационным входом трё тьего регистра адреса, первый - тре тий выходы первого и второго преобразователей кода операции в начальный адрес соединены с группой управ ЛЯНЯ1Р1Х входов блока коммутации сигн лов обнуления, выходы конца операци групп выходов первого и второго ком мутаторов микроопераций соединены с группой информационных входов комму TaTopia сигналов обнуления, первьй и второй выходы группы выходов которо го соединены с первым и вторым установочными входами регистра кода опе рации соответственно. . Кроме того, блок коммутации сигналов обнуления содержит первьй и второй коммутаторы, первьй и второй элементы ИЛИ, первьй и второй одновибраТоры, причем первьй и второй входы группы управляницих входов блока соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход Которого соединен с первым, управляющим входом первого коммутатора, третий и четвертьй входы группы управляющих входов блока соединены соответственно с вторым управляющим входом первого и первьм управляющим входом второго коммутаторов, выходы которых через первьй и второй одновИбраторы соединены соответственно с первым и вторым выходами группы выходов блока, пятьй и шестой входы . группы управляющих входов блока соединены соответственно с первым и вторым входами второго элемента ИЖ, выход которого соединён с вторым управляющим входом второго коммутатора, первьй вход группы информационных входов блока соединен с первыми информационными входами первого и второго коммутаторов, второй вход группы информационных входов блока соединен с вторыми информационными входами первого и второго кутаторов. Сущность изобретения состоит в повышении экономичности устройства путем сокращения суммарного объема памяти микрокоманд за счет введе- НИН специального блока памяти и записи в него.микропрограмм, реализуемых в обоих каналах управления. В предлагаемом устройстве в первом блоке памяти хранятся микропрограммы, предназначенные для управления , как правило, только первым каналом (объектом), во втором блоке памяти хранятся микропрограммы, предназначенные для управления только вторым каналом, в третьем блоке памяти хранятся микропрограммы, используемые для управления как первым, так и вторьм каналами. При этом исключается (или существенно уменьшается) дублирование микропрограмм, используемых в режимах последовательного и параллельного управления. Введение первого и второго блоков ассоциативной памяти, обусловленных ими связей позволяет по коду операции идентифицировать номер блока памяти микрокоманд, к которому должно быть произведено обращение (в котором хранится микропрограмма с заданным кодом операции) и обеспе чить перекоммутацию элементов су.емь для формирования требуемой конфигурации структуры. Введение технических средств, образующих допдлнительный канал микроп{ ограммного управленЬя, состоящий из третьего блока памяти шкpoкoмaнд третьих регистров адреса и микрокоманд, а также третьего формирователя адреса и обусловленных ими связей дает возможность организовать хране ние и считывание микропрограмм, используемых для управления первым и вторьм объектами. Введение коммутатора логических условий и обусловленных им связей позволяет обеспечить коммутацию сигналов логических условий, поступающих от первого и второго объектов управления, при выполнении микропрограмм, хранимых в третьем блоке памя ти микрокоманд. Введение новых связей для коммута торов, триггеров управления, элементов И и ИЛИ позволяет управлять форм рованием требуемой конфигурации стру туры. Введение блока коммутации сигнало обнуления и обусловленных им связей позволяет осуществлять избирательное обнуление полей регистра кода операции при реализации последовательных и параллельных микропрограмм. Таким образом, предлагаемое устройство отличается от известных по решаемой задаче - повьппением экономичности на основе дифференцированного хранения микропрограмм, используемых в режимах последовательного и параллельного управления, по пути решения указанной задачи - использованием специального канала мик ропрограммного управления, реализующего алгоритмы управления как первым, так и вторым объектами, по используемым техническим средствам введением первого и второго блоков ассоциативной памяти, третьих регист ров адреса и микрокоманд, формирователя адреса и блока памяти микрокоманд, а также коммутатора логических условий и соответствующих им новых связей. На фиг. 1 приведена функциональ-. ная схема предлагаемого устройства-, на фиг. 2 - функциональная схема фор мирователя адреса-, на фиг. 3 - пример построения первого и второго блоков ассоциативной памяти; на фиг. 4функциональная схема первого элемента ИЛИ с динамическим выходом; ,на фиг. 5 - функциональная схема блока коммутации сигналов обнуления. Параллельное микропрограммное устройство управления (фиг.1) содержит первый 1, третий 2 и второй 3 блоки памяти микрокоманд, первьй 4, третий 5 и второй 6 регистры адреса, первый регистр 7 микрокоманд, содержащий немодифицируемые 7.1 и модифицируемые 7.2 поля разрядов адреса, поле 7.3 логических условий и поле 7.4 микроопераций, третий регистр 8 микрокоманд, содержащий поля 8.1-8.4 (назначение этих полей аналогично назначению полей 7.1-7.4 соответственно), второй регистр 9 микрокоманд, содержащий поля 9.19.4 (их назначение аналогично назначению полей 7.1-7.4 соответственно), регистр 10 кода операции, сосТОЯЩ1Ш из полей первого 10.1 и второго to, 2 кодов операций, первый 11 и второй 12 блоки ассоциативной памяти, первый 13, Третий 14 и второй 15 формирователи адреса, первый 16,третий 17 и второй 13 коммутаторы кода операции, первьй 19 и вто рой 20 коммутаторы микроопераций, коммутатор 21 логических условий, iэлемент ЗИ-ИПИ 22, триггер 23 пуска, первый 24 и второй 25 триггеры управления, генератор 26 импульсов, четвертый 27, пятый 28, первый 29, шестой 30, восьмой 31, седьмой 32, второй 33, девятьй 34 и третий 35 элементы И, второй 36, третий 37, первый 38, четвертый 39, шестой 40 и пятьй 41 элементы ИЛИ , блок 42 коммутации сигналов обнуления. Кроме того, на фиг. 1 использованы следующие обозначения: вход 43 кода операции устройства, первьй 44 и второй 45 входы логических условий устройства соответственно, вход 46 пуска устройства, первьй выход 47 икроопераций устройства и выход 47.1 икрооперации Конец операции соотественно, второй выход 48 микроопеаций устройства и выход 48.1 микооперации Конец операции (второй араллельной микропрограммы) соответтвенно, выход 49 ошибки устройства, ервьй выход 50.1 первого блока 11, ервьй управляющий вход первого коммутатора 16 кода операции, первые входы элементов ИЛИ 36 и 39, первьй вход элемента ЗИ-ЙЛИ, первый управляющий вход первого коммутатора 19 микроопераций, второй выход 50.2 блока 11, первый управляющий вход третьего коммутатора 17 кода операции, первый управляющий вход коммутатора 21 логических условий, третий вход элемента ИЛИ 36, первый вход элемента ИЛИ 40, третий вход элемента 3 И-ИЛИ, третий управляющий входПервого коммутатора 19 микроопераций; третий выход 50.3 первого блока 11, первый управляющий вход второго коммутатора 18 кода операции первые входы элементов ИЛИ 37, 41, пятый вход элемента ЗИ-ИЛИ 22, второй управляющий вход втдрого коммутатрра 20 микроопераций-, первый выход 51.1 второго блока 12, второй управляющий вход первого коммутатора 16 кода операции,, вторые входы элементов ИЛИ 36, 39, второй вход элемента ЗИ-ИЖ 22, второй управляющйй вход первого коммутатора 19 микроопераций второй выход 51,2 в-торого блока 12 , второй управляющий ВХОД третьего коммутатора 17 кода on рации, второй управляющий вход коммутатора 21 логических условий, третий вход элемента ИЛИ 37, второй вход элемента ИЛИ 40, четвертьй вход элемента 22, первый управляющий вход второго коммутатора 20 микроопераций третий выход 51.3 второг блока 12, второй управляющий вход второго коммутатора 18 кода операции вторые входы элементов ИЛИ 37, 41, шестой вход элемента ЗИ-ИЛИ 22, третий управляющий вход второго коммутатора 20 микроопераций, выход 52 коммутатора 21 логических условий, первьй 53.1 и второй 53.2 выходы генератора 26 импульсов, выход 54 элемента И 30, вход синхронизации первого регистра 4 адреса, выход 55 элемента И 31, вход синхронизации третьего регистра адреса, выход 56 элемента И 32, вход синхронизации второго регистра адреса выход 57 элемента И 33, вход синхронизации первого регистра 7 микрокоманд, выход 58 элемента И 34, вход синхронизации третьего регистра 8 микрокоман выход 59 элемента И 35, вход информации второго регистра 9 микрокот манд, выход 60 элемента ИПИ 35, второй вход элемента И 30, второй вход

элемента И 33, выход 61 элемента ИЛИ 40, второй вход элемента И 31 второй вход элемента И 34; выход 62 элемента ИЛИ 41,/второй вход элемента И 32, второй вход элемента И 35.

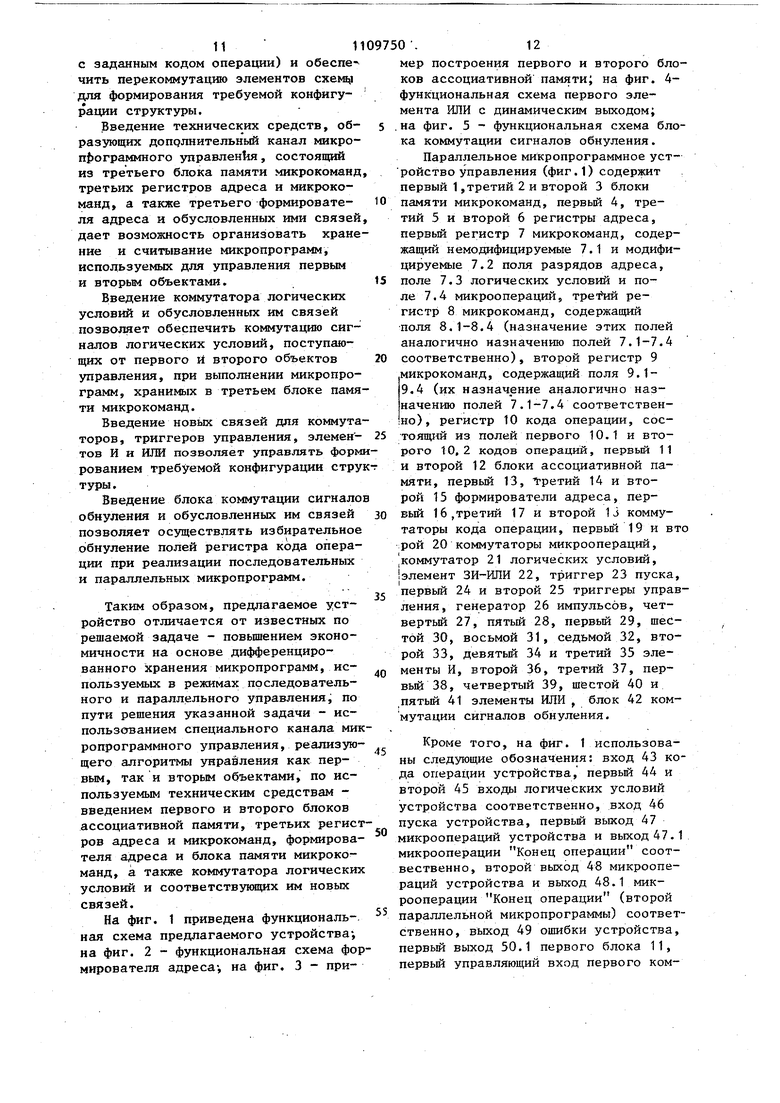

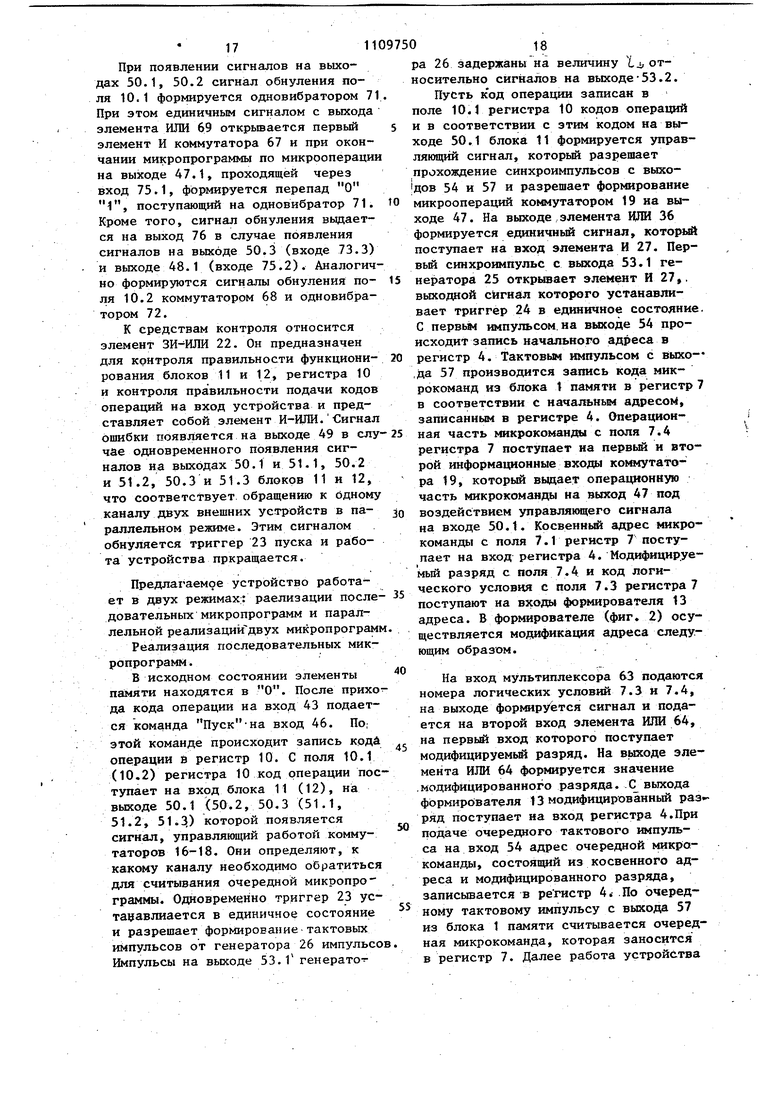

На фиг. 2 обозначены мультиплексор 63 и элемент ИЛИ 64.

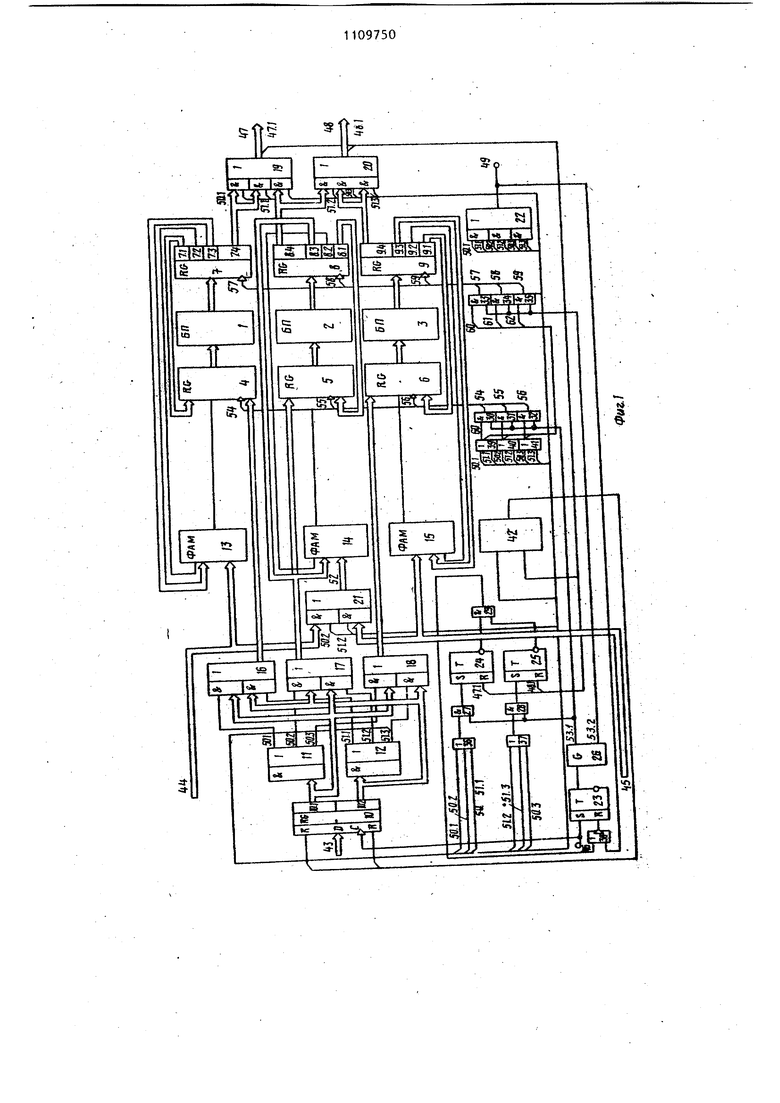

На фиг. 3 показана функциональная схема блоков 11 (12), реализуемых на базе программируемой матрицы для конкретного случаи кодировки кодов операции. Символами 65-68 обозначены первьй - четвертьй элементы НЕ соответственно, XI, Х2, ХЗ, Х4 входы кода операций. Например, когда на вход-блока 11 (12) поступают коды 0100 и 1100, сигнал появится на выходе 50.1 (51.1). Это означает, что микропрограммы с данным кодом операции хранятся в блоке 10 памяти микрокоманд.

i

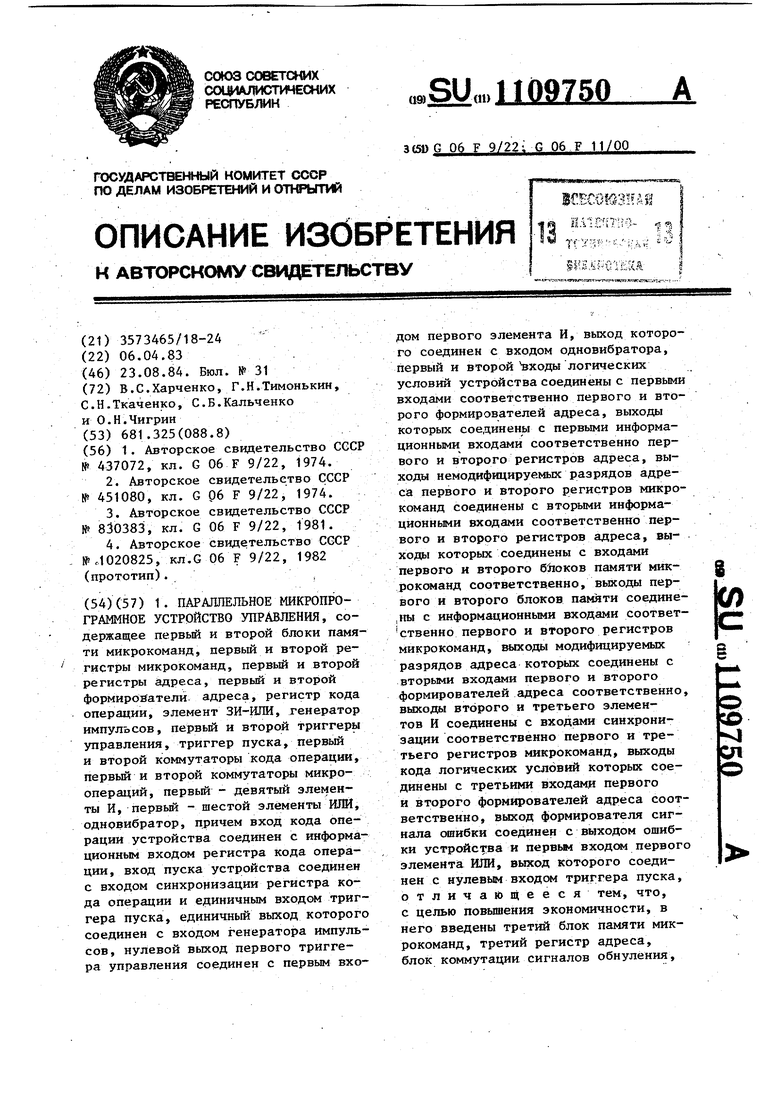

На фиг. 4 представлена функциональная схема элемента ИЛИ 38 с динамическим выходом, содержащая элемент ИЛИ 65 и одновибратор 66.

Блок 42 коммутации сигналов обнуления (фиг. 5) состоит из первого 67 и второго 68 коммутаторов, первого 69 и второго 70 элементов ИЛИ и первого 71 и второго 72 одновибраторов. Кроме того, на фиг. 5 использованы следующие обозначения: первьй 73.1 - третий 73.3 управляющие входы группы управляющих входов соответственно. Эти входы соединены с первым 50.1 - третьим 50.3 выходам блока 11 соответственно четвертьй 74.1 - шестой 74.3 управляющие входы группы управляюрщх входов соотвественно, которые соединены с первым 51.1 - третьим 51.3 выходами блоками 12 соответственноi первьй 75.1 и второй 75.2 входь группы информационных входов блока, которые соединены с выходами 47.1 и 47.2 соответственно j первьй 76 и второй 77 выходы группы выходов соответственно. Эти выходы соединены с первым и вторым установочными входами (входами обнуления) регистра 10 кода операции

Рассмотрим назначение элементов устройства, в котором условно могут быть выделены: средства хранения и считывания микрокоманд, средства пуска и синхронизации; средства управления и коммутации, а также средства контроля. К средствам хранения и считьшани микрокоманд, относятся регистр 10 ко да операции,.формирователи 13-15 фо мирования, регистры 4-6 адреса, бло ки 1-3 памяти микрокоманд, регистры 7-9 микро1 оманд. Регистр 10 обеспечиваетхранение кода операции. Этот регистр имеет два поля, обнуление которых производится раздельно сигналами с выходом 47.1 и 48.1. Формирователи 13-15 адреса служат для формирования адреса очередных микрокоманд в зависимости от ко да и значения логических условий и формирования начального адреса в соответствии с кодом операции. Мультиплексор 63 реализует логическую функцию - 1«. .., 1 - - S °2--°nVi2 3- n VlV3-% где 5( 6 {Я|Д значения логических условий; о(, - значения j-ro разряд - кода логических уело- вий п КГК - число логических уелоЭлемент ИЛИ 64 в точках ветвлени производит модификацию младшего раз ряда адреса (его изменение с О на 1 в случае равенства единице проверяемого логического условия), Блоки 1-3 памяти предназначены для хранения микропрограмм. Регистры 4-6 обеспечивают хранение адреса очередной микрокоманды. Регистры 7служат для запоминания считываемой микрокоманды, Средства пуска и синхронизации включают генератор 26 импульсов, триггер 23, злементы ИЛИ 38-41, эле менты И 30-35. Элементы ИЖ 38 и тр гер 23 выполняют фзгнкции пуска устройства и останова его при появлени сигнала ошибки или сигнала Конец операции. Особенностью злемента ИЛИ 38 является наличие динамического выхода При появлении сигнала на одном из входов элемента ИЛИ 38 на его выход формируется короткий импульс, который производит обнуление триггера 2 пуска. Формирование импульса осущес вляется одновибратором ёб (фиг. 4). Генератор 26 импульсов выполняет функцию формирования двух серий тактовых импульсов. Элементы ИЛИ 39-41 и элементы И 30-35обеспечивают синхронизацию устройства в. зависимости от режима работы и кода операции. При выполнении последовательных микропрограмм осуществляется считьшание . информации из одного блока памяти микрокоманд (блоков 1,2 или 3). В параллельном режиме работы в зависимости от кода операции производится одновременное считьтание .из пары блоков памяти 1 и 2 (1 и 3), (2 и 3). К средствам управления и коммутации относятся блоки 11 и 12, триггеры 24 и 25 управления, коммутаторы 16-21, элемейты ИЛИ 36 и 37, элементы И 27-29, блок 42 коммутации сигналов обнуления. Блоки 11 и 12 формируют сигналы, разрешающие считьшание микрокоманд с блоков 1-3 памяти в последовательном режиме и параллельное считывание микрокоманд из блоков 1 и 2 (1 и 3), (2 и 3), управляют синхронизацией устройства, коммутацией операционных частей микрокоманд и кодов логических условий. При поступлении кодов 0100, 0010, 1001, которые соответствуют коды операции 0100, 1100, 0010, 1001, 1011, формируется сигнал на выходе 50.1 (51.1), т.е. микропрограммы с указанными кодами операции хранятся в блоке 1 памяти микрокоманд. Единичные сигналы на выходах 50.2 (51.2) и 50.3 (51.3) формируются при поступлении кодов 1101, 0001, 0110, 1110 и 0011, 0111, 1111 соответственно. Коммутаторы 16-18 коммутируют код операции в зависимости от сигналов блоков 11- 12. Коммутаторы 19 и 20 предназначены для коммутации операционньк частей микрокоманд,кс мутатор 21 коммутирует коды логических условий. Элементы ШШ 36 и 37 формируют сигналы начала вьшолнения микропрограмм. Элементы И 27-29, триггеры 24 и 25 формируют команды на запоминание начала микропрограмм и останов устройства после окончания вьшолнения микропрограммы. Блок 42 осуществляет избирательное обнуление полей регистра 10. Обнуление разрядов поля 10,1 (10.2) производится при окончании микропрограмм, реализуемых каналами микропрограммного управления и инициируемых сигналами на вьрсодах 50.1-50.3 (51.1-51.3) блоков 11 (12). При появлении сигналов на выходах 50.1, 50.2 сигнал обнуления поля 10.1 формируется одновибратором 7 При этом единичным сигналом с выхода элемента ИЛИ 69 открьтается первый элемент И коммутатора 67 и при окончании микропрограммы по микроопераци на выходе 47.1, проходящей через вход 75.1, формируется перепад О 1, поступающий на одновибратор 71. Кроме того, сигнал обнуления выдается на выход 76 в случае появления сигналов на выходе 50.3 (входе 73.3) и выходе 48.1 (входе 75.2). Аналогич но формируются сигналы обнуления поля 10.2 коммутатором 68 и одновибратором 72. К средствам контроля относится элемент ЗИ-ИЛИ 22. Он предназначен для контроля правильности функционирования блоков 11 и 12, регистра 10 и контроля правильности подачи кодов операций на вход устройства и представляет собой элемент И-ИДИ. Сигнал ошибки появляется на выходе 49 в слу чае одновременного появления сигналов на выходах 50.1 и 51.1, 50.2 и 51.2, 50.3 и 51.3 блоков 11 и 12, что соответствует обращению к Одному каналу двух внешних устройств в параллельном режиме. Этим сигналом обнуляется триггер 23 пуска и работа устройства пркращается. Предлагаемое устройство работает в двух режимах: раелизации последовательных микропрограмм и параллельной реализации двух микропрограм Реализация последовательных микропрограмм. В исходном состоянии элементы памяти находятся в О. После прихо да кода операции на вход 43 подается команда вход 46. По, этой команде происходит запись крд& операции в регистр 10. С поля 10.1 (10,2) регистра 10 код операции пос тупает на вход блока 11 (12), на выходе 50.1 (50.2, 50.3 (51.1, 51.2, 51.3) которой появляется сигнал, управляющий работой коммутаторов 16-18. Они определяют, к какому каналу необходимо обратиться для считывания очередной микропрограммы. Одновременно триггер 23 устацавлиается в единичное состояние и разрешает формированиетактовых импульсов от генератора 26 импульсо Импульсы на выходе 53. f генератора 26 задержаны на величину 1 относительно сигналов на выходе-53.2. Пусть код операции записан в поле 10.1 регистра 10 кодов операций и в соответствии с этим кодом на выходе 50.1 блока 11 формируется управляющий сигнал, которьй разрешает прохождение синхроимпульсов с выхо|дов 54 и 57 и разрешает формирование микроопераций коммутатором 19 на выходе 47. На выходе элемента ИЛИ 36 формируется единичный сигнал, который поступает на вход элемента И 27. Первьй синхроимпульс с выхода 53.1 генератора 25 открывает элемент И 27,. В1лсодаой сигнал которого устанавливает триггер 24 в единичное состояние. С первьм импульсом, на выходе 54 происходит запись начального адреса в регистр 4. Тактовым импульсом с выхо- ,да 57 производится запись кода микрокоманд из блока t памяти в регистр 7 в соответствии с начальным адресом, записанным в регистре 4. Операционная часть микрокоманды с поля 7.4 регистра 7 поступает на первый и второй информационные входы коммутатора 19, который вьщает операционную часть микрокоманды на выход 47 под воздействием управляющего сигнала на входе 50.1. Косвенный адрес микрокоманды с поля 7.1 регистр 7 поступает на вход регистра 4. Модифицируемый разряд с поля 7.4 и код логического условия с поля 7.3 регистра 7 поступают на входы формирователя 13 адреса. В формирователе (фиг. 2) осуществляется модификация адреса следующим образом. На вход мультиплексора 63 подаются номера логических условий 7.3 и 7.4, на выходе фор№1руётся сигнал и подается на второй вход элемента ИЛИ , на первый вход которого поступает модифицируемый разряд. На выходе элемента ИЛИ 64 формируется значение модифицированного разряда,.С выхода формирователя 13 модифицированный разряд поступает на вход регистра 4.При подаче очередного тактового импульса на вход 54 адрес очередной микрокоманды, состоявщй из косвенного адреса и модифицированного разряда, записывается в регистр 4. .По очередному тактовому импульсу с выхода 57 из блока 1 памяти считывается очередная микрокоманда, которая заносится в регистр 7. Далее работа устройства 19 продолжается аналогично описанному. При считьшании последней микрокоманды на выходе 47.1 появляется сигнал Конец операции, которьй переводит к нулевое состояние триггер 24. Кроме того, по этому сигналу производит ся обнуление поля 10.1 регистра 10. Эту функцию реализует блок 42 коммутации сигналов обнуления (фиг. 5). Так как сигнал Конец операции появ ляется по тактовому импульсу с выхода 53.2, а единичный сигнал на входе триггера 25 появляется по импульсу с выхода 53, 1, то этим исключается возможность появления единичных сигналов на двух входах триггера 24. После обнуления посредством блока 42 поля 10.1 регистра 10 и триггера 24 на выходе элемента Е 29 появляется единичный потенциал. После этого импульсом с выхода элемента ИЛИ 38 обнуляется триггер 23, который запрещает формирование импульсов генератором 26. Устройство устанавливается в исходное состояние Если после записи кода операции в поле 10.1 регистра 10 появляется управляющие сигналы на выходах 50.2 или 50.3, работа устройства происходит аналогично описанному. Отличие состоит лишь в том, что считьшание микрокоманд производится из блоков 2 или 3 памяти соответственно. При работе с блоком 2 памяти логичес кие условия с входа 44 через коммутатор 21 под воздействием управляющего сигнала с выхода 50.2 подают ся на вход 52 формирователя 14. При записи кода операции в поде 10.2 регистра 10 работа устройства происходит согласно рассмотренному алгоритму. В этом случае управление производится с помощью блока 12. Параллельная реализация двух микропрограмм. В исходном состоянии после подачи команды Пуск на входе 43 в отличие от режима реализации одной микропро50граммы происходит запись двух кодов операций в поля, -10.1 и 10.2 регистра 10. При этом в соответствии с кодами операций на выходах блоков 11 и 12 появляются управляющие сигналы, которые разрешают независимое считывание микрокоманд из пары блоков памяти в соответствии с управляющими сигналами. Выдача операционных частей микрокоманд производится одновременно с двух выходов 47 и 48 в соответствии с управляющими сигналами блоков 11 и 12. Работа каждого канала происходит аналогично алгоритму работы при реализации одной последовательной микропрограммы. По первому тактовому импульсу с выхода 53.1 триггеры 24 и 25 устанавливаются в единичное состояние в соответствии с сигналами на , выходах блоков 11 и 12. Например, пусть параллельно считьюаются микропрограмм из блоков 2 и 3 памяти микрокоманд (присутствуют сигналы на выходе 50.2 блока 11 и 51.3 блока 12). Если первым заканчивается считывание микропрограммы из блока 3 памяти, тогда сигналом с выхода 47.1 триггер 24 и сигналом с выхода 76 блока 42 первое поле 10.1 регистра 10 устанавливаются в нулевое состояние. По окончании считывания микрокоманд из блока 3 памяти сигналом с выхода 48.1 триггер 25 и второе поле 10.2 регистра 10 сигна лом с выхода 77 блока 42 устанавливаются в нулевое состояние. Под воздействием положительного перепада однов.ибратор 66 формирует импульс, который устанавливает в нулевое состояние триггер 23. Нулевой сигнал на.выходе триггера 23 запрещает выдачу синхроимпульсов генератором 26. Устройство устанавливается в исходное состояние. При одновременном появлении сигналов на двух одноименных выходах блоков 11 и 12 элемент ЗИ-ИЛИ 22 выдает сигнал ошибки и блокирует работу предлагаемого устройства.

lZi8.Z(9.2l)

Ч.Ч (it.SlS.Z))

Фиг. 2

Фиг.З

Фаг.Ч

77

S

7f

Фиг.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-06—Подача