1 , 13

Изобретение отиосит я к вычислительной технике и может быть использовано нри определении законов распределения случайных величин,

изобретения - повышение точ- ности определения закона распределения при малом числе измерений.

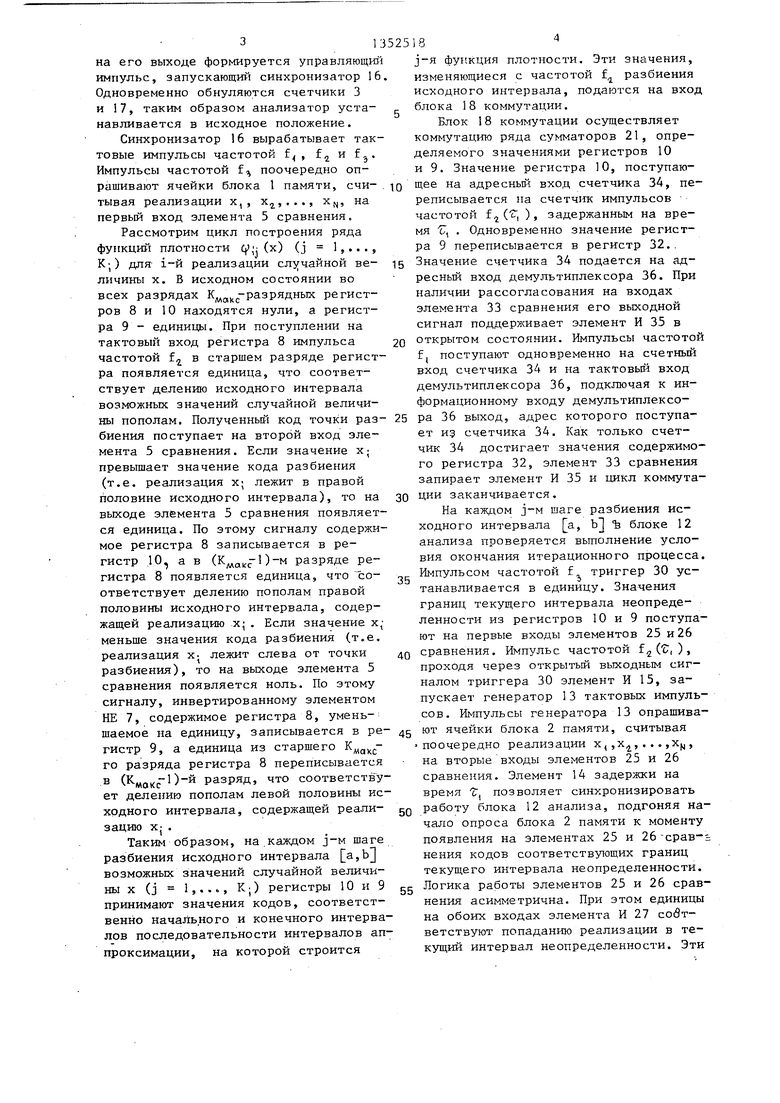

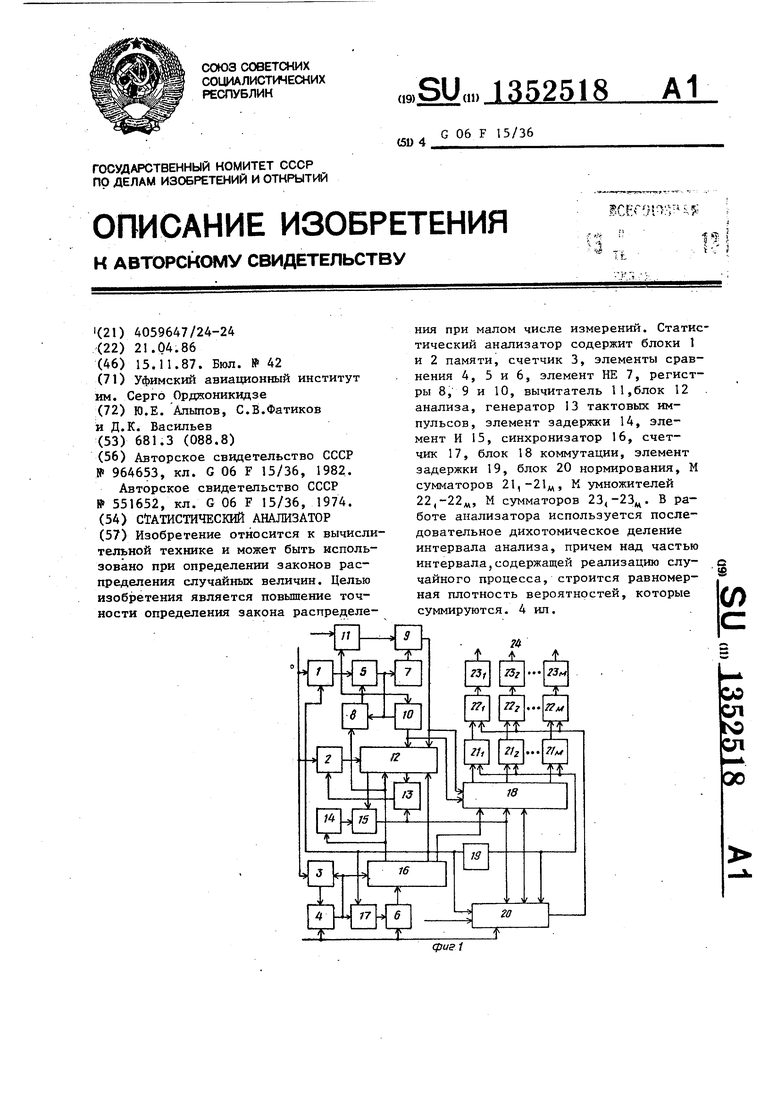

На фиг,I изображена структурная схема предлагаемого анализатора; на фиг,2 - схема блока анализа; на . фиг,3 - схема блока коммутации; на фиг,4 /г схема блока нормирования.

Статистическийанализатор содержит первый 1 и-второй 2 блоки памяти,пер- вьгй счетчик 3, третий 4, первый 5 и второй 6 элементы сравнения, элемент НЕ 7, второй 8, третий 9 и первый 0 регистры, вычитатель 11, блок 12 анализа, генератор 13 тактовых импульсов, первый элемент 14 за- держки, элемент И 15, синхронизатор 16, второй счетчик 17, блок 18 коммутации, второй элемент 19 задержки, блок 20 нормирования, М сумматоров

2i;-21, М умножителей 22,-22, М сумматоров , группу выходов 24

Блоки анализа (фиг.2) и коммутации (фиг.3) содержат первый 25 и второй 26 элементы сравнения, первый и второй элементы И 27 и 28, первый счетчик 29 триггер 30, элемент ИЛИ 31, регистр 32, элемент 33 сравнения, второй счетчик 34, элемент И 35 и демульти- плексор 36, Блок нормирования (фиг,4) содержит регистры 37, 38 и 39, умно- жители 41 и 42, делители 43 и 44, элемент ИЛИ 40 и счетчик 45,

Работа статистического анализатора основана на следующих зависимостях. Функция плотности ра(пределения имеет вид:

(f (х) S о при а X b ; (jj (х) О при а X, X b,

(1)

где а и b - границы интервала возможных значений случайной величины X, ,

Для каждой реализации Х из выборки объема N строят ряд функций шгат- ности Vj. (х) (J I, Kj), где К- - количество разбиений исходного интервала , bj при обработке i-й реализации.

Алгоритм построения следующий. На первом шаге исходный интервал разбивается пополам, часть, не содержащая реализации х; , отбрасывается, а над Оставшимся интервалом неопределенности строится функция плотности у| (х), представляющая собой плотность равномерного распределения высотой . Полученный интервал снова разбивается пополам, пустая часть отбрасывается, а над оставшимся интервалом строится функция плотности (У; (х) высотой и т.д.

Процесс построения функций (х) (j 1,,.., К;) для i-й реализации зак нчивается, если на очередном шаге полученный для х; интервал неопределенности не накрывает ни одну из других реализаций выборки х, х,,,,,

, ,) -- N- случае, если две или более реализации практически совпадают, критерием окончания обработки каждой из этих реализаций является совпадение на очередном шаге величины интервала неопределенности с заранее выбранным интервалом аппрок- . симации. Для удобства работы анализатора Исходный интервал а, Ъ должен включать целое число М интервалов аппрок1:имации, равное 2

максимально возможное

исходного интервала прной реализации.

Функции плотности Ц

(x) f (х)

имеют одинаковый вес, Условие, нормировки при этом вьгполняе гся соответствующим выбором высоты К,-| функции плотности ф;, (х) (i ,,.,., N) :

Kj- N-d

(3)

где d - ширина исходного интервала,

равная (Ь-а),

Высота-И j (j 2,,.., К;) функций плотности (х) опрвделяется соотношением

45

«i, Ни-2

(4)

Результирующая плотность распределения (х) определяется суммированием всех функций плотности ifl (х) :

(/(х) v,4x) (,;(х).(5) - i-i j t

Анализатор работает следующим образом.

Реализации исследуемой случайной величины X поступают на вход блоков- 1 и 2 памяти и счетчика 3. Значение счетчика 3 сравнивается в элементе 4 сравнения с величиной N заданного объема выборки. При совпадении сигналов на входах элемента 4 сравнения

3,

на его выходе формируется управлягощю импульс, запускающий синхронизатор 16 Одновременно обнуляются счетчики 3 и 17, таким образом анализатор устанавливается в исходное положение.

Синхронизатор 16 вырабатывает тактовые импульсы частотой f , f и f. Импульсы частотой f- поочередно опрашивают ячейки блока 1 памяти, счи- тывая реализации х, , х,..., х, на первый вход элемента 5 сравнения.

Рассмотрим цикл построения ряда

функций плотности С|);: (х) (J I,...,

К;) для- i-й реализации сл- чайной ве- личины X. В исходном состоянии во всех разрядах K gi :-раз рядных регистров 8 и 10 находятся нули, а регистра 9 - единицы. При поступлении на тактовый вход регистра 8 импульса частотой fj в старшем разряде регистра появляется единица, что соответствует делению исходного интервала возможных значений случайной величины пополам. Полученный код точки раз- биения поступает на второй вход элемента 5 сравнения. Если значение к; превышает значение кода разбиения (т.е. реализация х; лежит в правой половине исходного интервала), то на выходе элемента 5 сравнения появляется единица. По этому сигналу содержимое регистра 8 записывается в регистр 10, а в ()-M разряде регистра 8 появляется единица, что 1:о- ответствует делению пополам правой половины исходного интервала, содержащей реализацию х; . Если значение х, меньше значения кода разбиения (т.е. реализация х- лежит слева от точки разбиения), то на выходе элемента 5 сравнения появляется ноль. По этому сигналу, инвертированному элементом НЕ 7, содержимое регистра 8, уменьшаемое на единицу, записывается в ре- гистр 9, а единица из старшего К,..- го разряда регистра 8 переписывается в (К-макс разряд, что соответствует делению пополам левой половины исходного интервала, содержаш,ей реали- зацию Xj.

Таким образом, на.каждом j-м шаге разбиения исходного интервала а,Ь возможных значений случайной величины х (J 1,..., К|) регистры 10 и 9 принимают значения кодов, соответственно начального и конечного интервалов последовательности интервалов аппроксимации, на которой строится

j-я функция плотности. Эти значения, изменяющиеся с частотой f разбиения исходного интервала, подаются на вход блока 18 коммутации.

Блок 18 коммутации осуществляет кoм ryтaцию ряда сумматоров 21, определяемого значениями регистров 10 и 9. Значение регистра 10, поступающее на адресный вход счетчика 34, переписывается па счетчик импульсов частотой (С, ), задержанным на время о, , Одновременно значение регистра 9 переписывается в регистр 32.. Значение счетчика 34 подается на адресный вход демультиплексора 36. При наличии рассогласования на входах элемента 33 сравнения его выходной сигнал поддерживает элемент И 35 в открытом состоянии. Импульсы частотой f, поступают одновременно на счетный вход счетчика 34 и на тактовьй вход демультиплексора 36, подключая к информационному входу демультиплексора 36 выход, адрес которого поступает из счетчика 34. Как только счетчик 34 достигает значения содержимого регистра 32, элемент 33 сравнения запирает элемент И 35 и цикл коммутации заканчивается.

На каждом j-м шаге разбиения исходного интервала а, Ь Ъ блоке 12 анализа проверяется выполнение условия окончания итерационного процесса Импульсом частотой f триггер 30 устанавливается в единицу. Значения границ текущего интервала неопределенности из регистров 10 и 9 поступают на первые входы элементов 25 и 26 сравнения. Импульс частотой f2 ( с, ), проходя через открытый выходным сигналом триггера 30 элемент И 15, запускает генератор 13 тактовых импульсов. Импульсы генератора 13 опрашивают ячейки блока 2 памяти, считывая поочередно реализации х, ,х, . .. ,X|j,, на вторые входы элементов 25 и 26 сравнения. Элемент 14 задержки на время t позволяет синхронизировать работу блока 12 анализа, подгоняя начало опроса блока 2 памяти к моменту появления на элементах 25 и 26 -сравнения кодов соответствующих границ текущего интервала неопределенности. Логика работы элементов 25 и 26 сравнения асимметрична. При этом единицы на обоих входах элемента И 27 сойт- ветствуют попаданию реализации в текущий интервал неопределенности. Эти

13

реализации подсчт-ттываются счетчи- . ком 29, обнуленным предварительно импульсом частотой fJ.

Появление единицы на выходе второ- го разряда счетчика 29 соответствует

О

наличию в анализируемом интервале более чем одной реализации. Единичный сигнал поступает на вход останова генератора 13, пре кращая опрос блока 2 памяти. Одновременно обнуляется счетчик 29 для подготовки блока 12 к анализу дчередного интервала неопределенности.

Отсутствие единицы на выходе вто- рого разряда счетчика 29 по окончании цикла опроса блока 2 памяти означает, что в анализируемом интервале неопределенности лежит только одна реализация х; . В этом случае .очеред- ной импульс частотой f, проходя через открытьй элемент И 28, устанавливает триггер 30 в ноль. Элемент И 15 закрывается, не пропуская импульсы частотой f 2 (€ ,), управляющие работой блока 18 коммутации.

Таким образом, количество импульсов частотой ) прошедших через элемент И 15, совпадает с числом разбиений исходного интервала при об- работке i-й реализации. Процесс коммутации прекращается до прихода следующего импульса частотой f. , которьш считает из блока I памяти очередную (1+1)-ю реализацию случайной величи- ны X. .

В каждом J-M цикле коммутации ряда сумматоров 21, что соответствует j-му пагу разбиения исходного интервала а, Ь, на информационный вход де- мультиплексора 35 блока 18 коммутации поступает значение условной высоты функции плотности ((x). Условная высота К ц, (J I,..., Kj ) представляет co6oii целое число высот К; начальной функции плотности и принимает последовательно значения 1,2, 4, 8 и т.д. Значения К. (j I,..,, К) поступают из регистра 38 блока 20 нормирования (фиг.4). .

Перед началом работы анализатора в регистр 37 заносится единица, в регистр 39 - двойка, а на второй вход умножителя 42 подают значение ширины исходного интервала d. Импуль с частотой f обнуляет регистр 38 и переписывает в него единицу из регистра 37. Таким образом, на первом шаге К 1. Импульс частотой f ( ) счи8°

тывает содержимое регистра 38 на ин- формационньш вход демультиплексора 36. Кроме того, значение К удваивается умноткителем 41 и переписывается в регистр 38. Следующий импульс частотой f 2( ) считывает из регистра 38 значение Kfj 2 и т.д. По окончании обработки i-й реализации очередной импульс частотой f обнуляет регистр 38 и в него снова заносится начальная условная высота К 1 для обработки следующей реализации и т.д.

. Счетчик 45 подсчитывает значение К; . По окончании обработки i-й реализации выборки импульс частотой ) обнуляет счетчик 45 и тем самым подготавливает его к подсчету нового Kj .

На выходе делителя 44 появляется значение начальной высоты Н,, согласно (3). Накопленная в сумматорах 21 условная функция плотности V; (х) нормируется умножением на величину Н, . Таким образом, на выходах умножитеей 22 формируется значение (f); (х) результирующей функции плотности для i-й реализации.

После окончания умножения сумматоры 21 обнуляются импульсом частотой f , задержанным на время €: , Задержка € необходима для осуществления операции умножения блоками 22, На выходах сумматоров 23 формируется значение искомой плотности распределения согласно (5).

ормула изобретения

Статистический анализатор, содеращий генератор тактовых импульсов, умножитель, вычитатель, два сумматора, элемент .И и элемент НЕ, отичающийся тем, что, с цеью повышения точности определения закона распределения при малом числе измерений, в него введены два блока памяти, два счетчика, три элемента сравнения, три регистра, два элемен-. та задержкИ;, синхронизатор, (2М-2) (М - число интервалов аппроксимации) сумматоров, (М-1) умножителей, блок анализа, содержащий два элемента сравнения, счетчик, триггер, элеент РШИ и два элемента И, блок норирования, содерл{а1ций три регистра, два умножителя, два делителя, элемент ИПИ и счетчик, блок коммутации, содержащий регистр, счетчик, элемент

7 . 1 сравнения, элемент И и демультиплек- сор, причем в блоке анализа выход первого элемента сравнения соединен с первым входом первого элемента И,

выход второго элемента сравнения соединен с вторым входом первого элемента И, выход которого соединен со счетным входом счетчика, выход первого разряда счетчика соединен с первы входом второго элемента И, выход которого соединен с входом установки в О триггера, выход второго разряда счетчика соединен с первым входом элемента ИЛИ, . выход которого соедине с входом установки в О счетчика, в блоке нормирования вьтход первого регистра соединен с первым входом элемента ИЛИ, выход которого соединен с инфopмau oнным входом второго ре гнет ра, выход которого соединен с первым входом первого умножителя, вькод которого соединен с вторым входом элемента ИЛИ, выход третьего регистра соединен с вторым входом первого ум- ножителя и входом делимого первого делителя, вход делителя которого соединен с выходом второго умножителя, а выход - с входом делимого второго делителя, вход делителя которого сое динен с выходом счетчика, счетный вход которого соединен с тактовым входом второго регистра, вход установки в О второго регистра соедине с тактовым входом первого регистра и тактовым входом второго делителя, в блоке коммутации выход регистра соединен с первым входом элемента сравнения, выход которого соединен с первым входом элемента И, выход которо- го соединен со счетным входом счетчика и тактовым входом денультиплексора, адресный вход которого соединен с выходом счетчика и вторым входом элемента сравнения, информационный вход первого блока памяти соединен с информационным входом второго блока памяти и счетным входом первого счетчика и является информационным входом анализатора, выход первого блока памяти соединен с первым входом первого элемента сравнения, второй вход которого соединен с входом меньшае- мого вычитателя, информационным входом первого регистра и выходом вто

рого регистра, выход первого, элемента сравнения соединен с входом разрешения записи первого регистра, с входом разрешения считывания второго ре8

g о 5 о Q Q

5

5

гистра и через элемент НЕ - с входом разрешения записи третьего регистра, вход вычитаемого вычитателя является входом единичного потенциала анализатора, выход вычитателя соединен с информационным входом третьего регистра, выход первого регистра соединен с информационным входом счетчика блока коммутации и первым входом первого элемента сравнения блока анализа, выход третьего регистра соединен с информационным входом регистра блока коммутации и первым входом второго элемента сравнения блока анализа, выход второго блока памяти соединен с вторыми входами первого и второго элементов сравнения блока анализа, первый выход синхронизатора соединен с вторым входом элемента И блока коммутации, второй выход синхронизатора соединен с вторым входом второго элемента И блока анализа, с входом первого элемента задержки, с тактовым входом второго регистра, третий выход синхронизатора соединен с входом разрешения считывания первого блока памяти, с входом установки в 1 триггера блока анализа, с вторым входом элемента ИЛИ блока анализа, с тактовым входом первого регистра блока нормирования, с входом установки в О второго регистра и с тактовым - входом второго делителя блока норми рования, с входом второго эдемента задержки, со счетным входом счетчика импульсов, выход которого соединен с первым входом второго элемента сравнения, второй вход которого соединен с первым входом третьего элемента сравнения, с первым входом второго умножителя блока нормирования и является входом задания числа реализаций анализатора, второй вход третьего элемента сравнения соединен с выходом первого счетчика, выход третьего элемента сравнения соединен с входами установки в О первого и второго счетчиков, с входом запуска синхронизатора, вькод второго элемента сравнения соединен с входом останова синхронизатора, выход второго элемента задержки соединен с входом установки в О счетчика блока нормирования и входом з становки в О i-ro сум атора (i 1,..., М), инфор- мационньй вход которого соединен с соответствуюшдм входом демультиплек- сора блока коммутации, выход первого

элемента задержки соединен с первым входом элемента И, второй вход которого соединен с выходом триггера блока анализа, выход элемента И соединен с входом запуска генератора тактовых импульсов, с входом разрешения записи регистра блока коммутации и счетчика блока коммутации, со счетным входом счетчика блока нормирования и тактовым входом второго регистра блока нормирования, вход останова генератора тактовых импульсов соединен с выходом второго разряда счетчика блока анализа, выход генера тора тактовых импульсов соединен с

От регис/гтрсг 7ff

Us

Z

25

26

из ; Ргсгс/гг сг 3

входом разрешения считывания второго блока памяти, второй вход второго умножителя блока нормирования является входом задания ширины интервала анализа анализатора, выход второго делителя блока нормирования соединен с первым входом i-ro умножителя, второй вход i-ro умножителя соединен с выходом соответствующего сумматора, а выход i-ro умножителя соединен с входом (i+M)-ro сумматора, выход (i+M)-ro сумматора является выходом i-ro значения плотности распределе, ния анализатора.

27

2

,.Г

23

/ HttrrH /3

/3

30

а

4

.Z

ТЬу

1/3 ff/TO ct qjueS

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1990 |

|

SU1698892A1 |

| Статистический анализатор | 1986 |

|

SU1397939A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

| Статистический анализатор | 1985 |

|

SU1280395A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Статистический анализатор | 1986 |

|

SU1411779A1 |

| Статистический анализатор | 1989 |

|

SU1695328A1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

| Статистический анализатор | 1987 |

|

SU1499376A1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайных величин. Целью изобретения является повьшение точности определения закона распределения при малом числе измерений. Статистический анализатор содержит блоки 1 и 2 памяти, счетчик 3, элементы сравнения 4, 5 и 6, элемент НЕ 7, регистры 8, 9 и 10, вычитатель 11,блок 12 анализа, генератор 13 тактовых импульсов, элемент задержки 14, элемент И 15, синхронизатор 16, счетчик 17, блок 18 коммутации, элемент задержки 19, блок 20 нормирования, М сумматоров 21,-21д, К умножителей 22,-22д, М сумматоров 234-23. В работе анализатора используется последовательное дихотомическое деление интервала анализа, причем над частью интервала,содержащей реализацию случайного процесса, строится равномерная плотность вероятностей, которые суммируются. 4 ил. i (/)

Составитель В.Орлов Редактор М.Андрушенко Техред Л.Олийнык

Заказ 5568/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Пилипенко

| Статистический анализатор | 1980 |

|

SU964653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Статистический анализатор | 1974 |

|

SU551652A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-04-21—Подача