Фиг.{

Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайных величин.

Целью изобретения является повышение точности оценивания закона распределения при малом числе измерений.

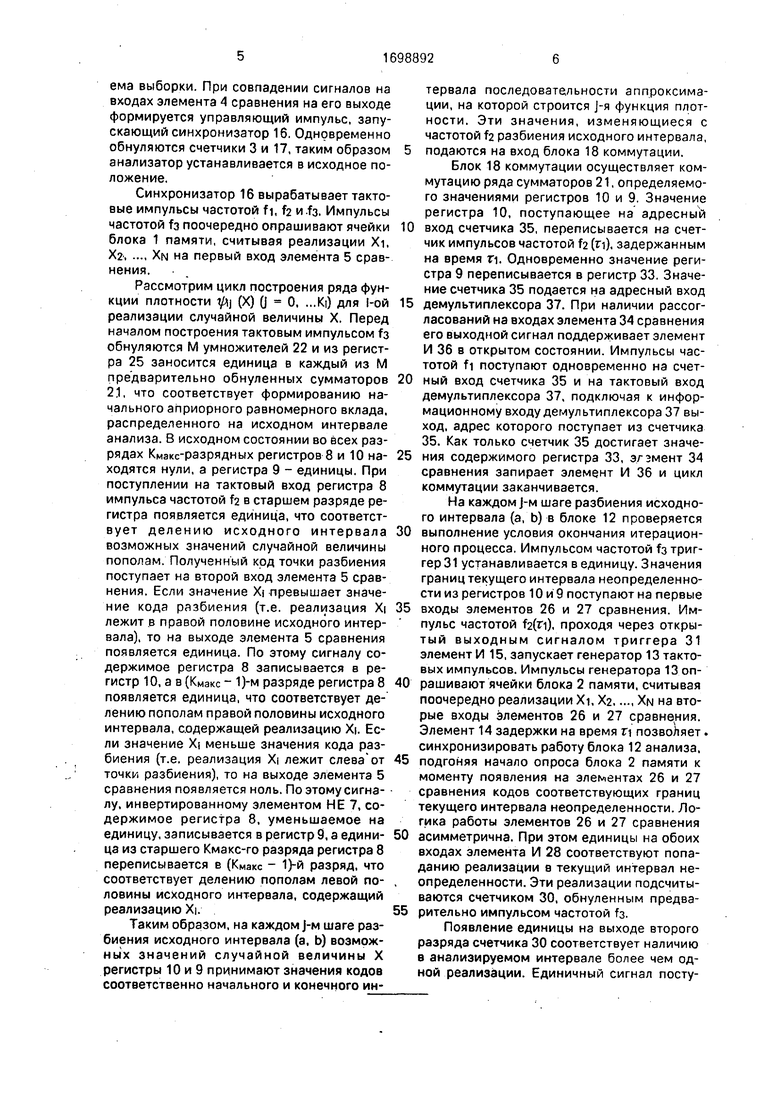

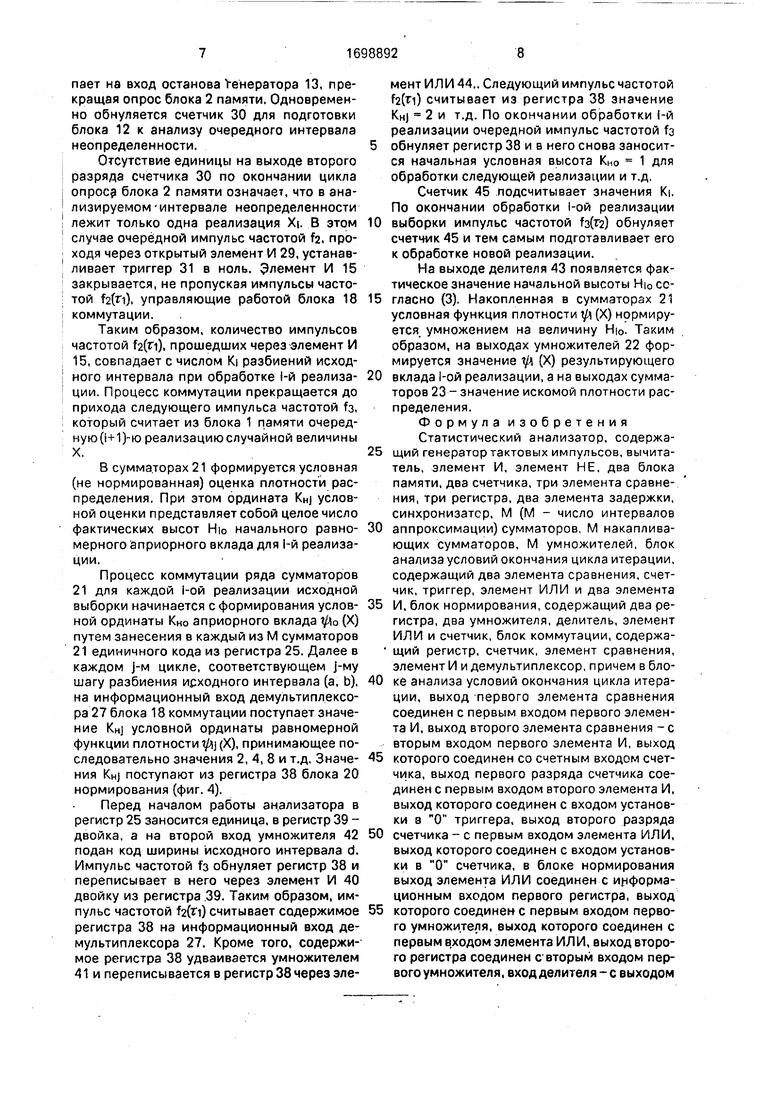

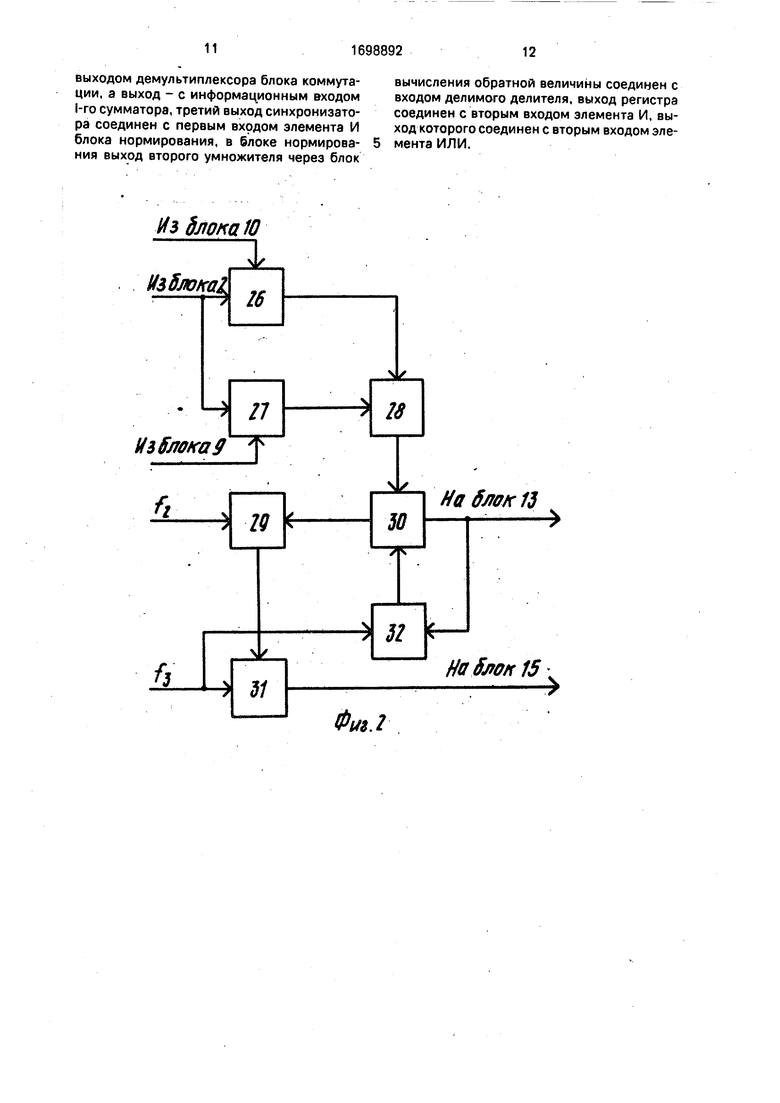

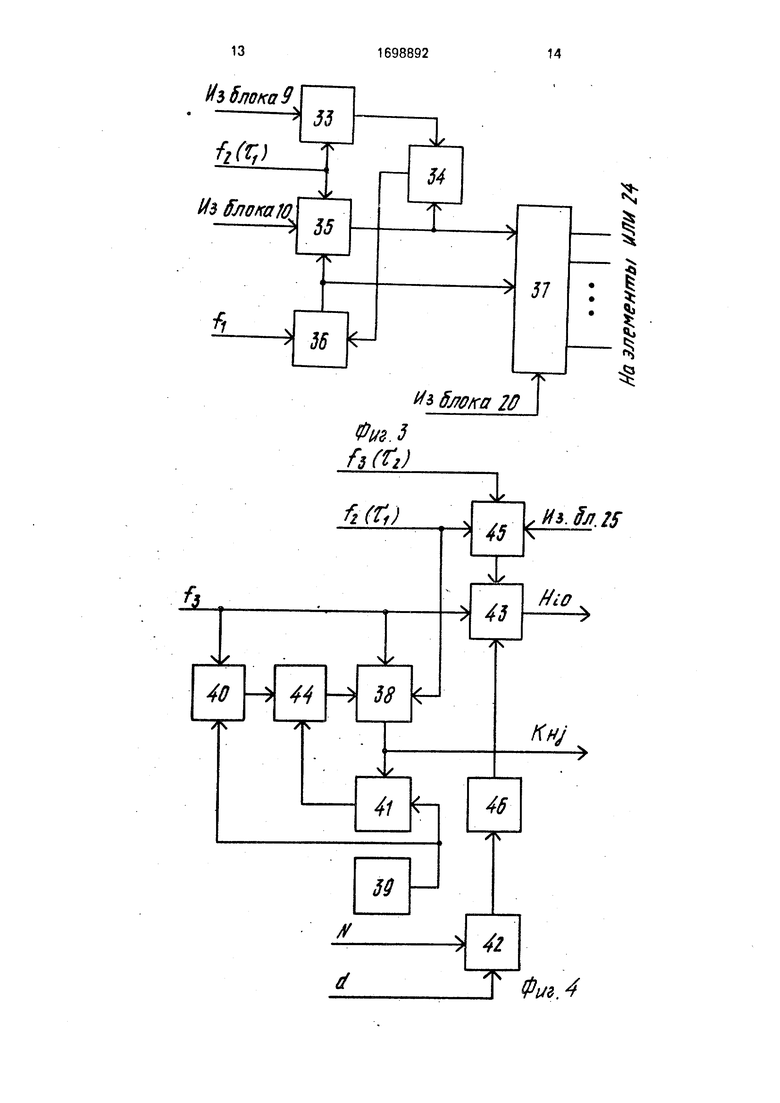

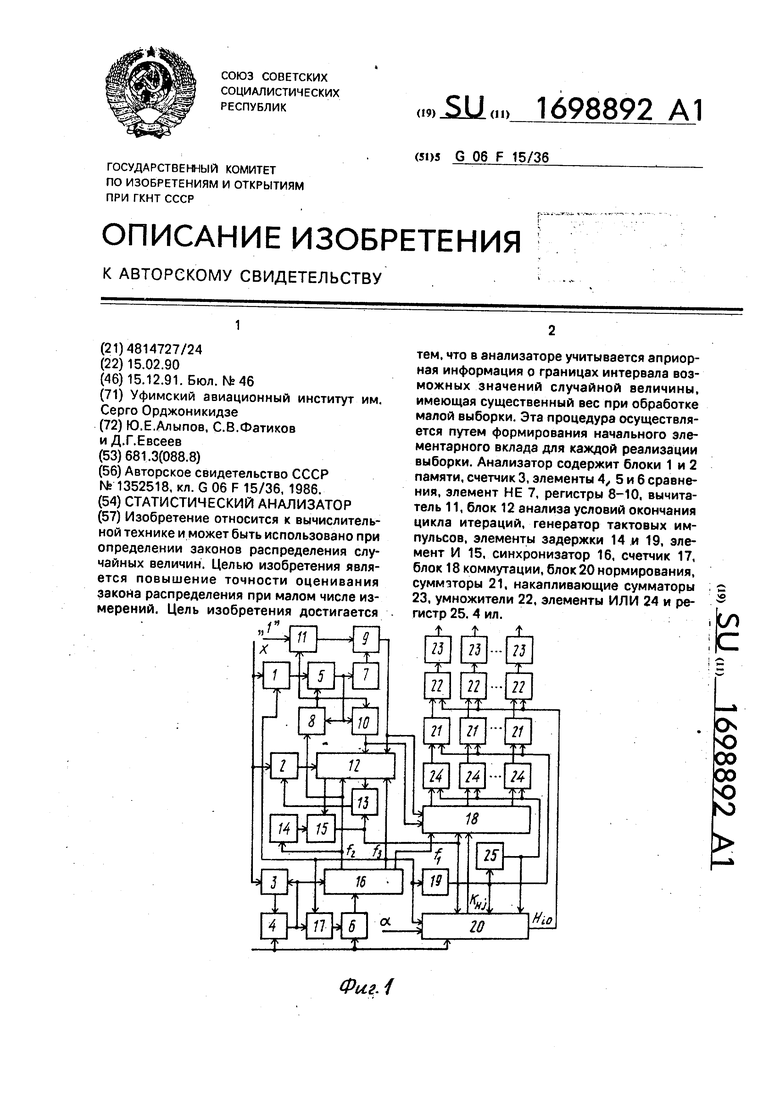

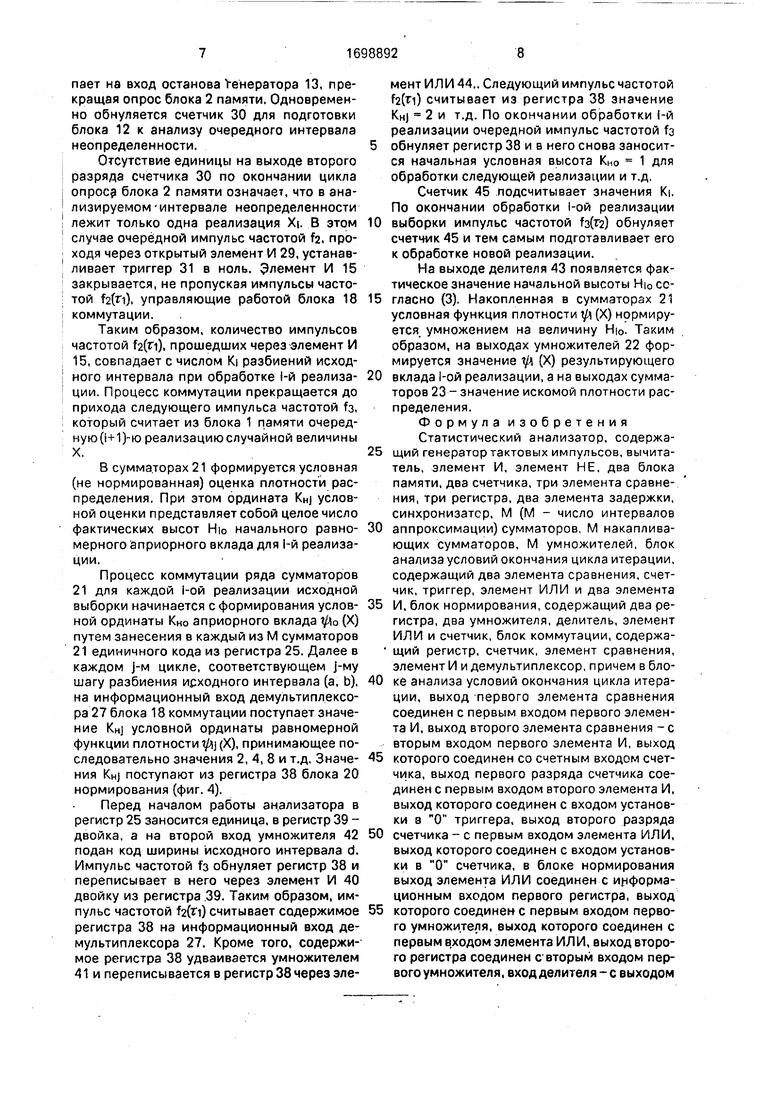

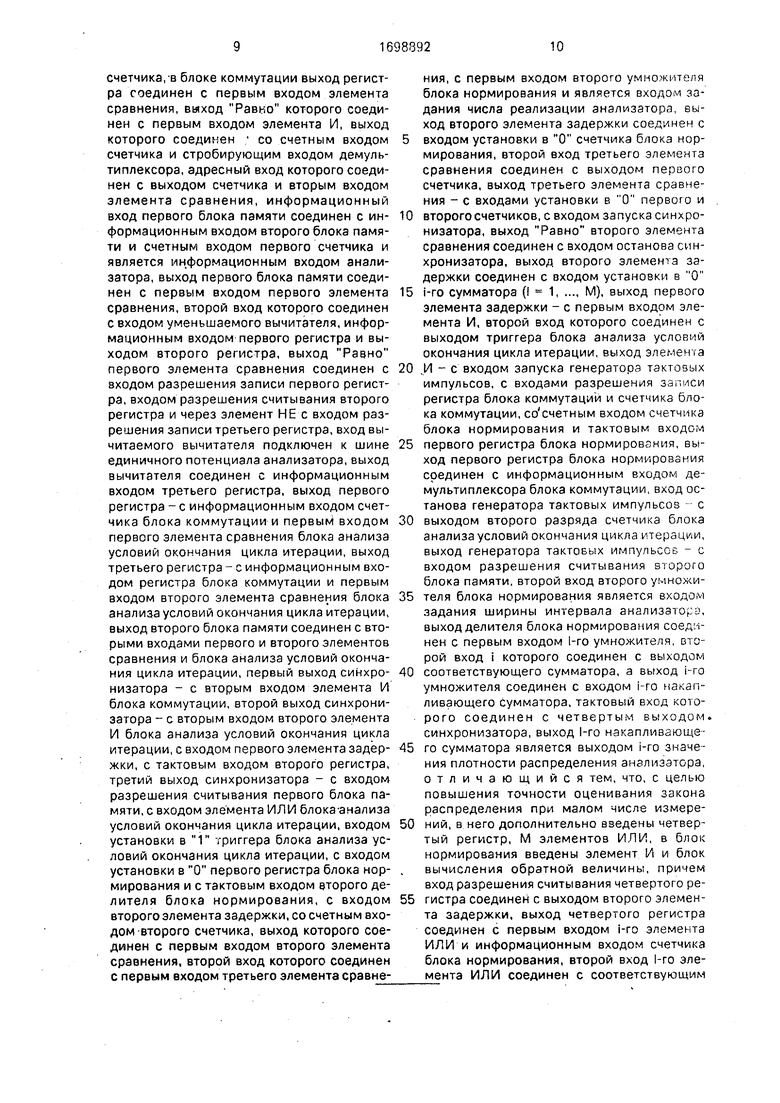

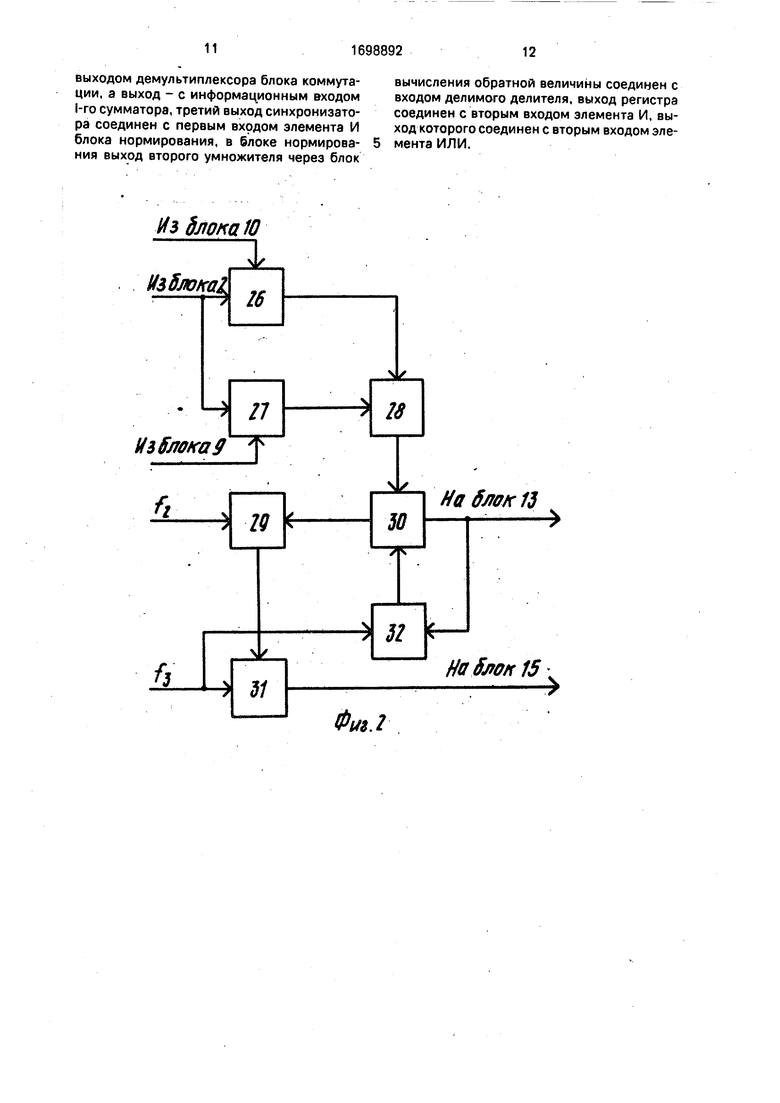

На фиг. 1 приведена функциональная схема статистического анализатора; на фиг.2 - схема блока анализа условий окончания цикла итераций; на фиг. 3 - схема блока коммутации; на фиг. 4 - схема блока нормирования.

Статистический анализатор содержит блоки 1 и 2 памяти, счетчик 3, элементы 4,5 и 6 сравнения, элемент НЕ 7, регистры 8, 9 и 10, вычитатель 11, блок 12 анализа условий окончания цикла итераций, генератор 13 тактовых импульсов, элемент 14 задержки, элемент И 15, синхронизатор 16, счетчик 17, блок 18 коммутации, элемент 19 задержки, блок 20 нормирования, М сумматоров 21, М умножителей 22, М накапливающих сумматоров 23, М элементов ИЛИ 24 и регистр 25.

Блок 12 анализа (фиг. 2) содержит два элемента 26 и 27 сравнения, два элемента И 28 и 29, счетчик 30, триггер 31 и элемент ИЛИ 32.

Блок 18 коммутации (фиг. 3) содержит регистр 33, элемент 34 сравнения, счетчик 35, элемент И 36 и демультиплексор 37.

Блок 20 нормирования (фиг. 4) содержит два регистра 38 и 39, элемент И 40. два умножителя 41 и 42, делитель 43, элемент ИЛИ 44, счетчик 45 и блок 46 вычисления обратной величины.

Работа статистического анализатора основана на следующих зависимостях. Функция плотности распределения имеет вид:

V(X) 0 при а Х Ь;

VHX) Onpna X, ,(1)

где а и b - границы интервала возможных значений случайной величины X.

Для каждой реализации X (I 1N) из

выборки объема N строят ряд функций плотности fyi (X) 0 0, KI), где Ki - количество разбиений исходного интервала а, Ь при обработке 1-й реализации. При малом числе наблюдений повышается информационный вес априорных данных об оцениваемой случайной величине. В связи с этим на первом шаге алгоритма построения оценки в анализаторе формируется элементарный вклад fyo (X) плотности вероятности, отражающий априорные знания о границах измерения случайной величины X и представляющий собой элементарную плотность равномерного распределения высотой Н|0 на интервале а, Ь. На втором шаге исходный интервал разбивается пополам, часть, не содержащая реализацию Xi, отбрасывается,

а над оставшимся интервалом неопределенности строится функция плотности $1 (X), представляющая собой плотность равномерного распределения высотой Ни. Полученный интервал снова разбивается

пополам, пустая часть отбрасывается, а над оставшимся интервалом строится функция

ПЛОТНОСТИ t/12 (X) ВЫСОТОЙ Н|2 И Т.Д.

Процесс построения функции $j (X) ( - 0,..., Ki) для 1-й реализации заканчивается,

если на очередном шаге полученный для Х| интервал неопределенности не накрывает ни одну из других реализаций выборки XL

Х2X|-1, Xt+iXN. В том случае, если две

или более реализации практически совпадают, критерием окончания обработки каждой из этих реализаций является совпадение на очередном шаге величины интервала неопределенности с заранее выбранным интервалом аппроксимации. Для удобства работы

анализатора исходный интервал а, Ь дол- жен включать целое число М интервалов

аппроксимации, равное 2Кмакс, где Кмакс - максимально возможное число разбиений интервала при обработке одной реализа- ции.

Функции плотности

К1

V(X) E ММ(2)

о

имеют одинаковый вес. Условие нормировки при этом выполняется соответствующим выбором высоты Hio функции плотности Vb (X):

Hl° ( Ki + 1 ) N d (3)

где d - ширина исходного интервала анализа, равная (Ь-а).

Высота HIJ функции плотности $j (X) определяется соотношением: HIJ Ню 2J.(4)

Результирующая плотность распределения (X) определяется суммированием всех функций плотности $ (X):

50

VM- I А()

i 1

NKi

- 2 2 0

Анализатор работает следующим обраtfj(X).

(5)

зом.

Реализации исследуемой случайной величины X поступают на вход блоков 1 и 2 памяти и счетчика 3. Значение счетчика 3 сравнивается с величиной N заданного объема выборки, При совпадении сигналов на входах элемента 4 сравнения на его выходе формируется управляющий импульс, запускающий синхронизатор 16. Одновременно обнуляются счетчики 3 и 17, таким образом анализатор устанавливается в исходное положение.

Синхронизатор 16 вырабатывает тактовые импульсы частотой fi, Ь n.fs, Импульсы частотой fa поочередно опрашивают ячейки блока 1 памяти, считывая реализации Xi, Х2XN на первый вход элемента 5 сравнения.

Рассмотрим цикл построения ряда функции плотности Vlj (X) 0 0. -KI) для 1-ой реализации случайной величины X. Перед началом построения тактовым импульсом тз обнуляются М умножителей 22 и из регистра 25 заносится единица в каждый из М предварительно обнуленных сумматоров 2.1, что соответствует формированию начального априорного равномерного вклада, распределенного на исходном интервале анализа. В исходном состоянии во всех разрядах Кмакс-разрядных регистров 8 и 10 находятся нули, а регистра 9 - единицы. При поступлении на тактовый вход регистра 8 импульса частотой f2 в старшем разряде регистра появляется единица, что соответствует делению исходного интервала возможных значений случайной величины пополам. Полученный код точки разбиения поступает на второй вход элемента 5 сравнения. Если значение Х| превышает значение кода разбиения (т.е. реализация Х| лежит .в правой половине исходного интервала), то на выходе элемента 5 сравнения появляется единица. По этому сигналу содержимое регистра 8 записывается в регистр 10, а в (Кмакс - 1)-м разряде регистра 8 появляется единица, что соответствует делению пополам правой половины исходного интервала, содержащей реализацию Х|. Если значение Х| меньше значения кода разбиения (т.е. реализация Xi лежит слева от точки разбиения), то на выходе элемента 5 сравнения появляется ноль. По этому сигналу, инвертированному элементом НЕ 7, содержимое pernctpa 8, уменьшаемое на единицу, записывается в регистр 9, а единица из старшего Кмакс-го разряда регистра 8 переписывается в (Кмакс - 1)-й разряд, что соответствует делению пополам левой половины исходного интервала, содержащий реализацию Х|.

Таким образом, на каждом j-м шаге разбиения исходного интервала (а, Ь) возможных значений случайной величины X регистры 10 и 9 принимают значения кодов соответственно начального и конечного интервала последовательности аппроксимации, на которой строится J-я функция плотности. Эти значения, изменяющиеся с частотой fa разбиения исходного интервала, 5 подаются на вход блока 18 коммутации.

Блок 18 коммутации осуществляет коммутацию ряда сумматоров 21, определяемого значениями регистров 10 и 9. Значение регистра 10, поступающее на адресный

0 вход счетчика 35, переписывается на счетчик импульсов частотой h (ri), задержанным на время п. Одновременно значение регистра 9 переписывается в регистр 33. Значение счетчика 35 подается на адресный вход

5 демультиплексора 37. При наличии рассогласований на входах элемента 34 сравнения его выходной сигнал поддерживает элемент И 36 в открытом состоянии. Импульсы частотой fi поступают одновременно на счет0 ный вход счетчика 35 и на тактовый вход демультиплексора 37, подключая к информационному входу демультиплексора 37 выход, адрес которого поступает из счетчика 35. Как только счетчик 35 достигает значе5 ния содержимого регистра 33, эгэмент 34 сравнения запирает элемент И 36 и цикл коммутации заканчивается.

На каждом j-м шаге разбиения исходного интервала (а, Ь) в блоке 12 проверяется

0 выполнение условия окончания итерационного процесса. Импульсом частотой fs триггер 31 устанавливается в единицу. Значения границ текущего интервала неопределенности из регистров 10 и 9 поступают на первые

5 входы элементов 26 и 27 сравнения. Импульс частотой f2(Ti), проходя через открытый выходным сигналом триггера 31 элемент И 15, запускает генератор 13 тактовых импульсов. Импульсы генератора 13 оп0 рашивают ячейки блока 2 памяти, считывая поочередно реализации Xi, X2XN на вторые входы элементов 26 и 27 сравнения. Элемент 14 задержки на время п позволяет. синхронизировать работу блока 12 анализа,

5 подгоняя начало опроса блока 2 памяти к моменту появления на элементах 26 и 27 сравнения кодов соответствующих границ текущего интервала неопределенности. Логика работы элементов 26 и 27 сравнения

0 асимметрична. При этом единицы на обоих входах элемента И 28 соответствуют попаданию реализации в текущий интервал неопределенности. Эти реализации подсчитываются счетчиком 30, обнуленным предва5 рительно импульсом частотой fa.

Появление единицы на выходе второго разряда счетчика 30 соответствует наличию в анализируемом интервале более чем одной реализации. Единичный сигнал поступает на вход останова Генератора 13, прекращая опрос блока 2 памяти. Одновременно обнуляется счетчик 30 для подготовки блока 12 к анализу очередного интервала неопределенности.

Отсутствие единицы на выходе второго разряда счетчика 30 по окончании цикла опрос блока 2 памяти означает, что в анализируемом -интервале неопределенности лежит только одна реализация Х|. В этом случае очерёдной импульс частотой fa, проходя через открытый элемент И 29, устанавливает триггер 31 в ноль, Элемент И 15 закрывается, не пропуская импульсы частотой f2(ri), управляющие работой блока 18 коммутации.

Таким образом, количество импульсов частотой f2(ji), прошедших через-элемент И 15, совпадает с числом К| разбиений исходного интервала при обработке 1-й реализации. Процесс коммутации прекращается до прихода следующего импульса частотой fa, который считает из блока 1 памяти очеред- ную(1+1)-ю реализацию случайной величины X.

В сумматорах 21 формируется условная (не нормированная) оценка плотности распределения. При этом ордината KHJ условной оценки представляет собой целое число фактических высот Hio начального равномерного априорного вклада для 1-й реализации.

Процесс коммутации ряда сумматоров 21 для каждой l-ой реализации исходной выборки начинается с формирования условной ординаты Кно априорного вклада t/ь (Х) путем занесения в каждый из М сумматоров 21 единичного кода из регистра 25. Далее в каждом j-м цикле, соответствующем j-му шагу разбиения исходного интервала (а, Ь), на информационный вход демультиплексо- ра 27 блока 18 коммутации поступает значение KHj условной ординаты равномерной функции плотности i/ij (X), принимающее последовательно значения 2, 4, 8 и т.д. Значения KHj поступают из регистра 38 блока 20 нормирования (фиг. 4).

Перед началом работы анализатора в регистр 25 заносится единица, в регистр 39 - двойка, а на второй вход умножителя 42 подан код ширины исходного интервала d. Импульс частотой fs обнуляет регистр 38 и переписывает в него через элемент И 40 двойку из регистра 39. Таким образом, импульс частотой f2(ri) считывает содержимое регистра 38 на информационный вход де- мультиплексора 27. Кроме того, содержимое регистра 38 удваивается умножителем 41 и переписывается в регистр 38 через элемент ИЛИ 44.. Следующий импульс частотой f2(fi) считывает из регистра 38 значение KHJ 2 и т.д. По окончании обработки 1-й реализации очередной импульс частотой fa

обнуляет регистр 38 и в него снова заносится начальная условная высота Кно - 1 для обработки следующей реализации и т.д.

Счетчик 45 подсчитывает значения К|. По окончании обработки l-ой реализации

выборки импульс частотой 1з(Т2) обнуляет счетчик 45 и тем самым подготавливает его к обработке новой реализации.

На выходе делителя 43 появляется фактическое значение начальной высоты HIO ccгласно (3). Накопленная в сумматорах 21 условная функция плотности $ (X) нррмиру- ется умножением на величину Н|0. Таким образом, на выходах умножителей 22 формируется значение ф (X) результирующего

вклада i-ой реализации, а на выходах сумматоров 23 - значение искомой плотности распределения.

Формула изобретения Статистический анализатор, содержащий генератор тактовых импульсов, вычита- тель, элемент И, элемент НЕ, два блока памяти, два счетчика, три элемента сравнения, три регистра, два элемента задержки, синхронизатор, М (М - число интервалов

аппроксимации) сумматоров, М накапливающих сумматоров, М умножителей, блок анализа условий окончания цикла итерации, содержащий два элемента сравнения, счетчик, триггер, элемент ИЛИ и два элемента

И, блок нормирования, содержащий два регистра, два умножителя, делитель, элемент ИЛИ и счетчик, блок коммутации, содержащий регистр, счетчик, элемент сравнения, элемент И и демультиплексор, причем в блоке анализа условий окончания цикла итерации, выход -первого элемента сравнения соединен с первым входом первого элемента И, выход второго элемента сравнения - с

вторым входом первого элемента И, выход которого соединен со счетным входом счетчика, выход первого разряда счетчика соединен с первым входом второго элемента И, выход которого соединен с входом установки в О триггера, выход второго разряда

счетчика - с первым входом элемента ИЛИ, выход которого соединен с входом установки в О счетчика, в блоке нормирования выход элемента ИЛИ соединен с информационным входом первого регистра, выход

которого соединен с первым входом первого умножителя, выход которого соединен с первым в.ходом элемента ИЛИ, выход второго регистра соединен с вторым входом первого умножителя, вход делителя-с выходом

счетчика, в блоке коммутации выход регистра соединен с первым входом элемента сравнения, выход Равно которого соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика и стробирующим входом демуль- типлексора, адресный вход которого соединен с выходом счетчика и вторым входом элемента сравнения, информационный вход первого блока памяти соединен с ин- формационным входом второго блока памяти и счетным входом первого счетчика и является информационным входом анализатора, выход первого блока памяти соединен с первым входом первого элемента сравнения, второй вход которого соединен с входом уменьшаемого вычитателя, информационным входом первого регистра и выходом второго регистра, выход Равно первого элемента сравнения соединен с входом разрешения записи первого регистра, входом разрешения считывания второго регистра и через элемент НЕ с входом разрешения записи третьего регистра, вход вычитаемого вычитателя подключен к шине единичного потенциала анализатора, выход вычитателя соединен с информационным входом третьего регистра, выход первого регистра - с информационным входом счетчика блока коммутации и первый входом первого элемента сравнения блока анализа условий окончания цикла итерации, выход третьего регистра - с информационным входом регистра блока коммутации и первым входом второго элемента сравнения блока анализа условий окончания цикла итерации, выход второго блока памяти соединен с вторыми входами первого и второго элементов сравнения и блока анализа условий окончания цикла итерации, первый выход синхро- низатора - с вторым входом элемента И блока коммутации, второй выход синхронизатора - с вторым входом второго элемента И блока анализа условий окончания цикла итерации, с входом первого элемента задер- жки, с тактовым входом второго регистра, третий выход синхронизатора - с входом разрешения считывания первого блока памяти, с входом элемента ИЛИ блока-анализа условий окончания цикла итерации, входом установки в 1 триггера блока анализа условий окончания цикла итерации, с входом установки в О первого регистра блока нор- мирования и с тактовым входом второго делителя блока нормирования, с входом второго элемента задержки, со счетным входом второго счетчика, выход которого соединен с первым входом второго элемента сравнения, второй вход которого соединен с первым входом третьего элемента сравнения, с первым входом второго умножителя блока нормирования и является входом задания числа реализации анализатора, выход второго элемента задержки соединен с входом установки в О счетчика блока нормирования, второй вход третьего элемента сравнения соединен с выходом первого счетчика, выход третьего элемента сравнения - с входами установки в О первого и второго счетчиков, с входом запуска синхронизатора, выход Равно второго элемента сравнения соединен с входом останова синхронизатора, выход второго элемента задержки соединен с входом установки в О 1-го сумматора (1 1, .... М), выход первого элемента задержки - с первым входом элемента И, второй вход которого соединен с выходом триггера блока анализа условий окончания цикла итерации, выход элемента .И - с входом запуска генератора тактовых импульсов, с входами разрешения записи регистра блока коммутации и счетчика блока коммутации, со счетным входом счетчика блока нормирования и тактовым входом первого регистра блока нормирования, выход первого регистра блока нормирования соединен с информационным входом де- мультиплексора блока коммутации, вход останова генератора тактовых импульсов - с выходом второго разряда счетчика блока анализа условий окончания цикла итерации, выход генератора тактовых импульсов - с входом разрешения считывания второго блока памяти, второй вход второго умножителя блока нормирования является входом задания ширины интервала анализаторы, выход делителя блока нормирования соединен с первым входом i-ro умножителя, второй вход i которого соединен с выходом соответствующего сумматора, а выход i-ro умножителя соединен с входом i-ro накапливающего сумматора, тактовый вход которого соединен с четвертым выходом. синхронизатора, выход 1-го накапливающего сумматора является выходом 1-го значения плотности распределения анализатора, отличающийся тем, что, с целью повышения точности оценивания закона распределения при малом числе измерений, в него дополнительно введены четвертый регистр, М элементов ИЛИ, в блок нормирования введены элемент И и блок вычисления обратной величины, причем вход разрешения считывания четвертого регистра соединен с выходом второго элемента задержки, выход четвертого регистра соединен с первым входом i-ro элемента ИЛИ и информационным входом счетчика блока нормирования, второй вход 1-го элемента ИЛИ соединен с соответствующим

выходом демультиплексора блока коммутации, а выход - с информационным входом 1-го сумматора, третий выход синхронизатора соединен с первым входом элемента И блока нормирования, в блоке нормирования выход второго умножителя через блок

вычисления обратной величины соединен с входом делимого делителя, выход регистра соединен с вторым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1986 |

|

SU1397939A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

| Статистический анализатор | 1986 |

|

SU1352518A1 |

| Статистический анализатор | 1985 |

|

SU1280395A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1322172A1 |

| Статистический анализатор | 1987 |

|

SU1499376A1 |

| Статистический анализатор | 1986 |

|

SU1411779A1 |

| Статистический анализатор | 1986 |

|

SU1401482A1 |

| Статистический анализатор | 1987 |

|

SU1441418A1 |

Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайных величин. Целью изобретения является повышение точности оценивания закона распределения при малом числе измерений. Цель изобретения достигается тем, что в анализаторе учитывается априорная информация о границах интервала возможных значений случайной величины, имеющая существенный вес при обработке малой выборки. Эта процедура осуществляется путем формирования начального элементарного вклада для каждой реализации выборки. Анализатор содержит блоки 1 и 2 памяти, счетчик 3, элементы 4, 5 и б сравнения, элемент НЕ 7, регистры 8-10, вычита- тель 11, блок 12 анализа условий окончания цикла итераций, генератор тактовых импульсов, элементы задержки 14 и 19, элемент И 15. синхронизатор 16, счетчик 17, блок 18 коммутации, блок 20 нормирования, суммэторы 21, накапливающие сумматоры 23, умножители 22, элементы ИЛИ 24 и регистр 25. 4 ил.

Из длокаЮ

71

М$5лока9

-

53

fift)

fo блокам

55

Л

-

36

Фиг.З fs (fi)

54

/ ч

37

s

i блока 20

-I

Г

: |

I

Hi. л. 2S

Фиг.4

| Статистический анализатор | 1986 |

|

SU1352518A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-15—Публикация

1990-02-15—Подача