Изобретение относится к приборостроению, в частности к магнитной записи с высокой плотностью, а именно к устройствам синхронного воспроизведения цифровой информации.

Цель изобретения - повышение достоверности воспроизведения информации.

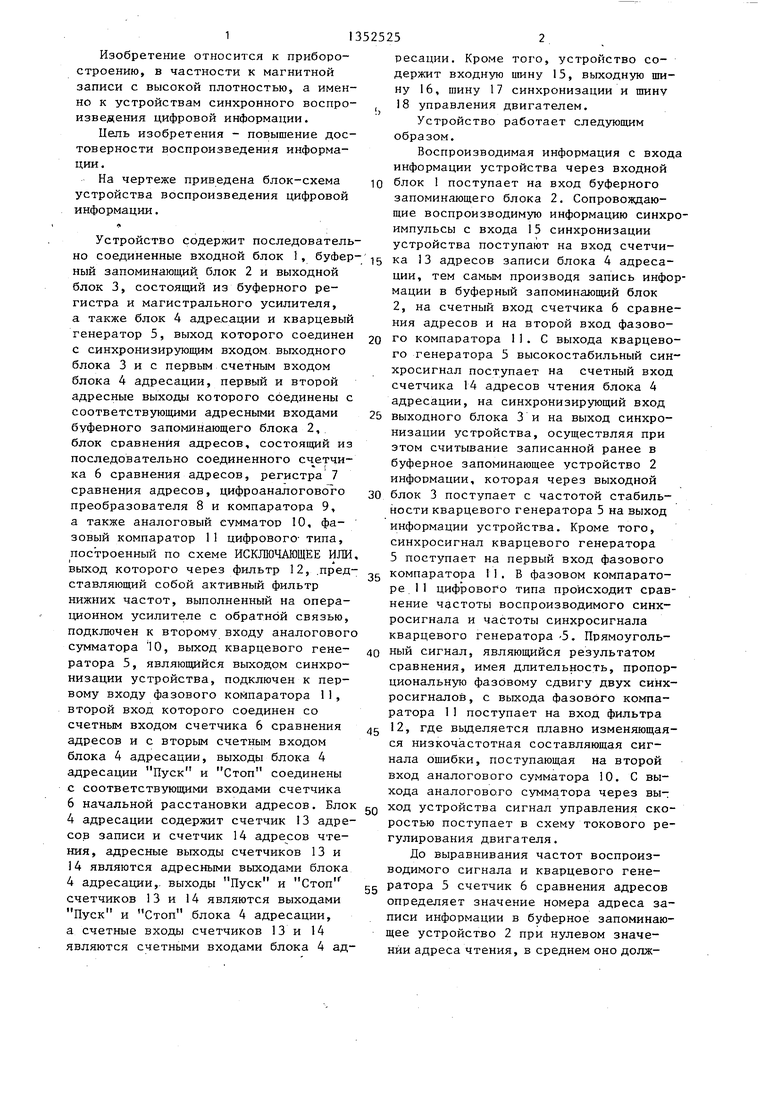

На чертеже приведена блок-схема устройства воспроизведения цифровой информации.

Устройство содержит последовательно соединенные входной блок 1, буфер ный запоминающий блок 2 и выходной блок 3, состоящий из буферного регистра и магистрального усилителя, а также блок 4 адресации и кварцевый генератор 5, выход которого соединен с синхронизирующим входом выходного блока 3 и с первым счетным входом блока 4 адресации, первый и второй адресные выходы которого соединены с соответствующими адресными входами буферного запоминающего блока 2, блок сравнения адресов, состоящий из последовательно соединенного сч етчи- ка 6 сравнения адресов, регистра 7 сравнения адресов, цифроаналогового преобразователя 8 и компаратора 9, а также аналоговый сумматор 10, фазовый компаратор 11 цифрового- типа, построенный по схеме ИСКЛЮЧАЮЩЕЕ ИЛИ выход которого через фильтр 12, .представляющий собой активный фильтр нижних частот, выполненный на операционном усилителе с обратной связью, подключен к второму входу аналоговог сумматора 10, выход кварцевого генератора 5, являющийся выходом синхронизации устройства, подключен к первому входу фазового компаратора 11, второй вход которого соединен со счетным входом счетчика 6 сравнения адресов и с вторым счетным входом блока 4 адресации, выходы блока 4 адресации Пуск и Стоп соединены с соответствующими входами счетчика 6 начальной расстановки адресов. Бло 4 адресации содержит счетчик 13 адресов записи и счетчик 14 адресов чтения, адресные выходы счетчиков 13 и 14 являются адресными выходами блока 4 адресации,, выходы Пуск и Стоп счетчиков 13 и 14 являются выходами Пуск и Стоп блока 4 адресации, а счетные входы счетчиков 13 и 14 являются счетными входами блока 4 ад

10

0

25

0

5

g

0

5

0

5

ресации. Кроме того, устройство содержит входную тину 15, выходную шину 16, шину 17 синхронизации и шину 18 управления двигателем.

Устройство работает следующим образом.

Воспроизводимая информация с входа информации устройства через входной блок 1 поступает на вход буферного запоминающего блока 2. Сопровождающие воспроизводимую информацию синхроимпульсы с входа 15 синхронизации устройства поступают на вход счетчика 13 адресов записи блока 4 адресации, тем самым производя запись информации в буферный запоминающий блок 2, на счетный вход счетчика 6 сравнения адресов и на второй вход фазового компаратора 11. С выхода кварцевого генератора 5 высокостабильный синхросигнал поступает на счетный вход счетчика 14 адресов чтения блока 4 адресации, на синхронизирующий вход выходного блока 3 и на выход синхронизации устройства, осуществляя при этом считывание записанной ранее в буферное запоминающее устройство 2 информации, которая через выходной блок 3 поступает с частотой стабильности кварцевого генератора 5 на выход информации устройства. Кроме того, синхросигнал кварцевого генератора 5 поступает на первый вход фазового компаратора II. В фазовом компараторе 1 1 цифрового типа происходит сравнение частоты воспроизводимого синхросигнала и частоты синхросигнала кварцевого генератора -5. Прямоугольный сигнал, являющийся результатом сравнения, имея длительность, пропорциональную фазбвому сдвигу двух синхросигналов, с выхода фазового компаратора 1I поступает на вход фильтра 12, где вьщеляется плавно изменяющаяся низкочастотная составляющая сигнала ошибки, поступающая на второй вход аналогового сумматора 10. С выхода аналогового сумматора через выход устройства сигнал управления скоростью поступает в схему токового регулирования двигателя.

До выравнивания частот воспроизводимого сигнала и кварцевого генератора 5 счетчик 6 сравнения адресов определяет значение номера адреса записи информации в буферное запоминающее устройство 2 при нулевом значении адреса чтения, в среднем оно долж

но равняться общего числа ячеек буферного запоминающего устройства 2, которое переносится каждый цикл счета адресов чтения в регистр 7 сравнения адресов. После преобразования в цифроаналоговом преобразователе 8 значение разности адресов записи и чтения в виде изменяющегося напряжения поступает на вход компарато ра 9. Это пороговое устройство служит индикатором выхода изменяющегося напряжения из установленных точных пределов, соответствующих минимально и максимально возможным значениям ад ресов записи в буферное запоминающее устройство 2. Б случае превьшения одного из опорных напряжений выход двойного .компаратора 9 переключается из нуля в положительное состояние, являясь дополнительным сигналом для увеличения скорости с целью начального разнесения адресов записи и чте- ния,

Дальнейшее управление скоростью определяется сигналом, снимаемым через фильтр 12 с фазового компаратора 11, в этом случае отсутствует накопление ощибки в разнице адресов записи и чтения информации, так как отклонение фазы воспроизводимого сигнала от фазы синхросигнала кварцевого генератора 5 в виде плавно меняющегося сигнала постоянно поступает через аналоговый сумматор 10 и шину 18 управления скоростью двигателя в схему токовог .регулирования двигателя, исключая возможность выхода частоты воспроиз- -водимого сигнала из полосы захвата устройства синхронизации, а также исключая возможность нарушения ста

Редактор М.Андрушенко Заказ 5568/50

Составитель С.Егоров

Техред Л.Олийнык Корректор Г.Решетник

Тираж 588 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,- Москва, Ж-35, Раущская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0

5

5

0

5

бильности работы сервомеханизма аппарата высокоплотной магнитной записи.

Формула изобретения Устройство воспроизведения цифровой информации, содержащее последовательно соединенные входной блок, подключенный входом к входной шине, буферный запоминающий блок и выходной блок , выход которого подключен к выходной щине, а также шину управления двигателем и кварцевый генератор, выход которого подключен к синхронизирующему входу выходного блока и первому входу блока адресации, второй вход которого подключен к щине синхронизации, а первый и второй, а также третий и четвертый выходы подключены соответственно к адреснь м входам буферного запоминающего блока и к входам блока сравнения, отличающееся тем, что, с целью повьш1ения достоверности воспроизведения информации, в него введены последовательно соединенные фазовый компаратор, первый вход которого подключен к шине синхронизации, а второй - к выходу кварцевого генератора. Фильтр и аналоговый сумматор, первым входом подключенный к выходу фильтра, а выходом - к шине управления двигателем, а также блок сравнения, состоящий из последовательно соединенных счетчика сравнения адресов, счетным входом подключенного к щине синхронизации, регистра сравнения адресов, цифроаналогового преобразователя и компаратора, выход которого подключен к второму входу аналогового сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1153347A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| УСТРОЙСТВО СБОРА ДАННЫХ | 2002 |

|

RU2218596C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Устройство для записи-воспроизведения цифровой информации на видеомагнитофоне | 1984 |

|

SU1157568A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

Изобретение относится к устройствам синхронного воспроизведения цифровой информации. Синхросигнал кварцевого генератора 5 поступает на вход фазового компаратора 11, где происходит сравнение частоты воспроизводимого синхросигнала и частоты синхросигнала кварцевого генератора 5. Прямоугольный сигнал, являющийся результатом сравнения, поступает на вход фильтра 12, где вьщеляется плавно изменяющаяся низкочастотная составляющая сигнала ошибки, поступающая на вход сумматора 10. С выхода последнего через выход устр-ва сигнал управления скоростью поступает в схему-тактового регулирования двигателя. 1 ил. J6 i (Л

| Система магнитной записи и воспроизведения информации | 1977 |

|

SU699551A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1153347A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-11-15—Публикация

1986-02-14—Подача