Изобретение относится к технике допускового контроля частоты.

Цель изобретения - повышение быст- Содействия и расширение функциональных возможностей.

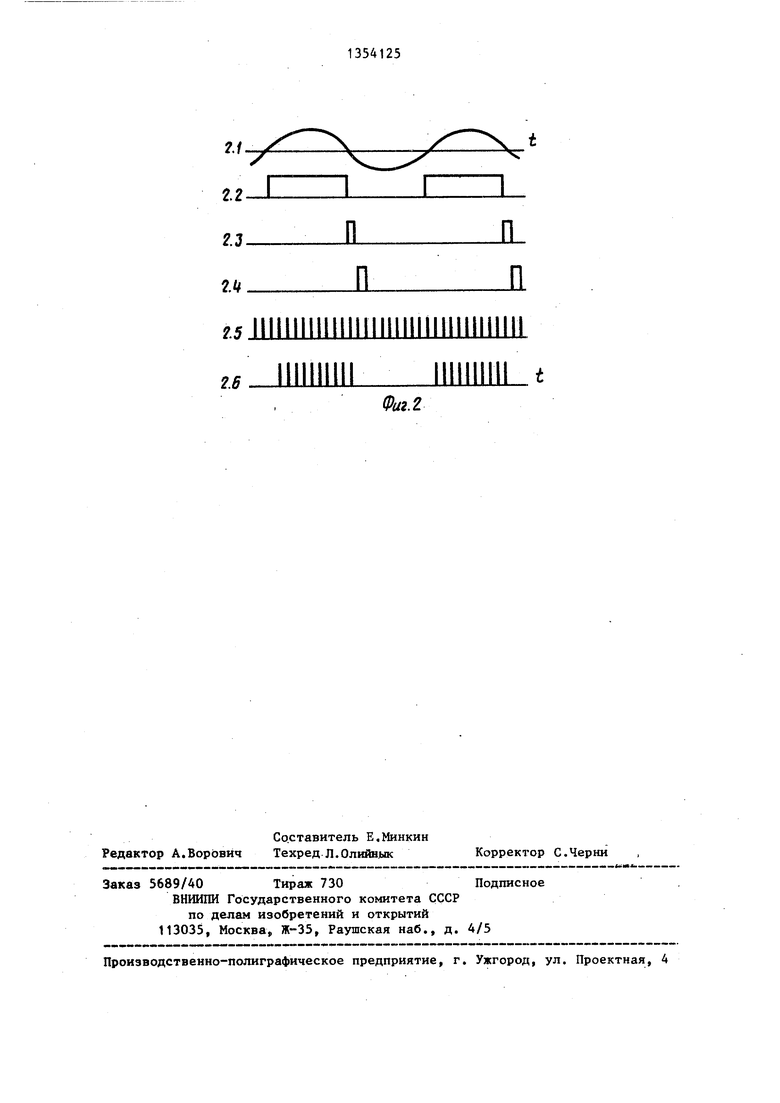

На фиг. 1 представлена функциональная схема устройства, на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит буферный регистр 1, программируемый делитель 2 частоты, генератор 3 эталонных импульсов, формирователь 4 меандра, блок 5 тактирования, счетчик 6 импульсов с предварительной установкой, трехвходовый элемент И 7, многовходо- вьй элемент И 8, элемент 9 и магистраль 10 микропроцессора.

Вход буферного регистра 1 соединен с магистралью 10 микропроцессора, а выход - с входом предварительной записи счетчика 6, управляющий вход программируемого делителя 2 соединен с магистралью 10 микропроцессора, информационный - с первым выходом эталонного генератора 3 им- fпульсов, а выход - с вторым входом элемента И 7, второй выход эталонного генератора 3 импульсов соединен с тактовым входом блока 5 тактирования, управляющий вход которого соединен с выходом формирователя 4 меандра и первым входом элемента И 7 выходы блока 5 тактирования соединены соответственно с первым входом элемента И 9 и входом разрешения пе- резациси счетчика 6, счетный вход которого соединен с выходом элемента И 7, выход П+1-ГО разряда соединен с инверсным третьим входом элемента И 7, а выходы разрядов с К-«-1-го по п-й (где п К) включительно соединены соответственно с входами много- входового элемента И 8, выход которого соединен с вторым входом элемента И 9, управляющий вход формирователя 4 меандра соединен с магистралью 10. микропроцессора.

Устройство работает следующим образом.

По магистрали 10 микропроцессора в буферный регистр 1 заносится Код смещения f , а в программируемый делитель 2 - код коэффициента деления, при этом на выходе программируемого делителя устанавливается частота импульсов, равная отношению частоты сигнала, поступающего с генера

5

0

5

тора 3 импульсов, к коэффициенту деления делителя 2.

Формирователь 4 меандра преобразует входной синусоидальный сигнал 2.1 (фиг. 2) и сигнал прямоугольной формы 2.2. Цикл распознавания начинается с нулевого сигнала на выходе формирователя 4 меандра. Этот сигнал запускает блок 5 тактирования. Второй тактовый сигнал 2,4, поступающий на вход перезаписи счетчика 6, записывает код буферного регистра 1 в счетчик 6.

Первый полупериод входного сигнала 2.1 соответствует положительному перепаду и положительному сигналу на выходе формирователя 4 меандра (2.2).

Входной положительный сигнал прямоугольной формы с выхода формирователя 4 меандра закрывает блок тактирования по управляющему входу и поступает на вход трехвходового элемента И 7, открывая его, и тем самым разрешает прохожл;ение импульсов заполнения 2.5 с выхода программируемого делителя 2 на счетный вход счетчика 6 (2.6).

Код смещения fpд, , предварительно занесенный в счетчик 6, в сумме с просчитанной пачкой импульсов, если частота сигнала соответствует ожидае- |Мой, составляет все единицы в старших разрядах счетчика 6 от К+1 до п и поэтому на выходе элемента И 8 формируется сигнал, подтверждающий,что распознавание произошло. Если же какой-либо из разрядов от К+1-го до п-й равен нулю по завершению цикла распознавания, значит частота распознаваемого сигнала не соответствует ожидаемой.

Для того, чтобы сигналы, кратные по частоте ожидаемому, не были восприняты как ожидаемый сигнал, п+1-й разряд счетчика 6 при переходе из нулевого в единичное состояние блокирует элемент И 7 ijo инверсному входу до конца измерительного полупериода В этом случае с 1-го по п-й разряды счетчика 6 находятся в нулевом состоянии. Ложного распознавания не происходит.

Второй полупериод входного сигнала 2.2, соответствующий отрицательному перепаду и нулевому сигналу на выходе формирователя 4 меандра, блокирует элемент И 7, счет прекращает0

0

5

0

5

ся и запускается блок 5 тактирования на выходах которого формируются выходные тактовые последовательности 2.3 и 2.4.

Первый тактовый импульс 2.3 стро- бирует элемент И 9. Если во время первого полупериода произошло распознавание, сигнал об этом поступает на выход устройства, если нет, то состояние выхода устройства распознавания не изменяется.

Второй тактовый импульс 2.4 записывает в счетчик 6 код с выхода буферного регистра-1. Схема готова к следующему циклу-распознавания.

Диапазон tuf, в пределах которого отклонение частоты входного сигна- 20 ключены соответственно к магистрали

ла от ожидаемой приведет к распознаванию, задается тем, что младшие разряды счетчика 6 от первого до К-го не заведены на элемент И 8. Если

некоторая частота распознавания.

fpто распознавание происходит, если входной сигнал лежит в диапазоне от (fp- uf) до 2/2 ,

(fp + fif), при uf

к-(

f 2 -2

Поскольку fp и uf фиксированы для конкретного устройства распознавания то настройка на необходимую частоту производится подбором частоты заполнения счетчика 6 путем перестройки программируемого делителя 2 и изменением кода смещения мого в счетчик 6.

ttv

записываеТаким образом, распознавание частоты осуществляется за время, не пре- вьшающее ее один период, при этом расширяются функциональные возмож- Ыости устройства за счет возможности включения его в автоматизированную систему измерения.

Формула изобретения Устройство распознавания частоты, содержащее счетчик импульсов, соединенный с дешифратором, генератор импульсов эталонной частоты, элементы И, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей, в него введены блок тактирования, формирователь меандра, программируемый делитель, буферный регистр, магистраль микропроцессора, дешифратор выполнен в виде многовходового

элемента И, а счетчик импульсов снабжен входом предварительной записи, причем вход буферного регистра, управляющие входы программируемого делителя и формирователя меандра подмикропроцессора, выход буферного регистра соединен с входом предварительной записи счетчика импульсов, информационный вход программируемого

делителя соединен с первым выходом генератора импульсов эталонной частоты, а выход - с вторым входом трех- входового элемента И, первый вход которого соединен с управляющим входом блока тактирования и выходом формирователя меандра, второй выход генератора импульсов эталонной частоты соединен с тактовым входом блока тактирования, выходы которого соединены соответственно с первым входом элемента И и входом разрешения перезаписи счетчика импульсов, счетный вход которого соединен с выходом трехвхо- дового элемента И, выход п+1-го разряда соединен с инверсным трет.ьим входом трехвходового элемента И а выходы разрядов с К+1-го по п-й (где п К)/включительно соединены соответственна с входами многовходового элемента И, выход которого сое

инен с вторым входом элемента И.

2.3.

гц.

75lllllllllllilllllllllllHIIIIIIIIII

,/ iiiiniiii тиши t

,Фаг.2

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Умножитель частоты | 1978 |

|

SU798831A1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Устройство для функционального контроля цифровых схем | 1987 |

|

SU1583884A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

Изобретение относится к технике допусковрго контроля частоты. Целью изобретения является повьшение быстродействия и расширение функциональных возможностей. Для достижения этой цели в устройство дополнительно йп.- введены блок 5 тактирования, формирователь 4 меандра, программируемый делитель 2 частоты, буферный регистр 1, магистраль микропроцессора 10. При этом дешифратор выполнен в виде многовходового элемента И 8, а счетчик 6 импульсов снабжен входом предварительной записи. Устройство также содержит генератор 3 эталонных импульсов, трехвходовый элемент И 7, элемент И 9. Устройство обеспечивает распознавание частоты за время, не превышающее один период, при этом расширяются функциональные возможности устройства за счет включения его в автоматизированную систему измерения. 2 ил. (Л

| Устройство допускового контролячАСТОТы | 1979 |

|

SU830250A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля частоты импульсов | 1974 |

|

SU468178A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-23—Публикация

1985-12-30—Подача