ел

00 00 00

00 4

315

Изобретение относится к вычислительной технике и может быть использовано для функционально-динамического контроля цифровых схем, а также для управления любыми быстродейству- кщими процессами.

Цель изобретения - повышение эффективности контроля за счет повышения эффективности использования узлов памяти заданного объема и сокращение времени контроля.

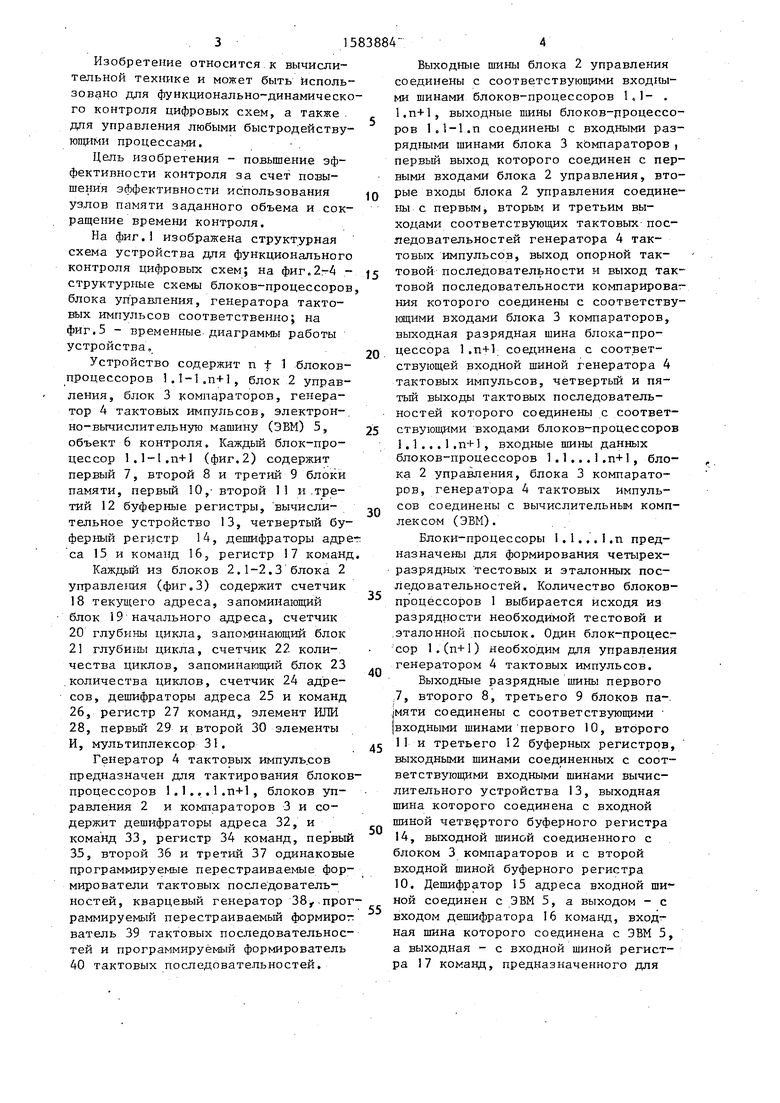

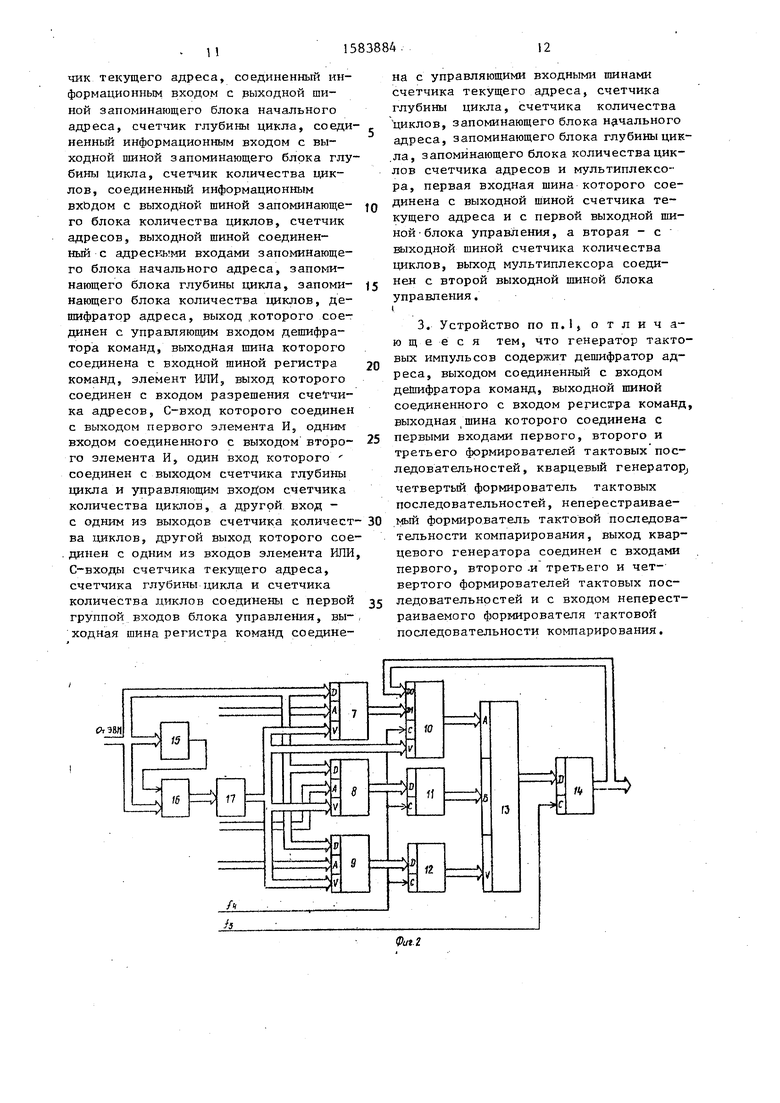

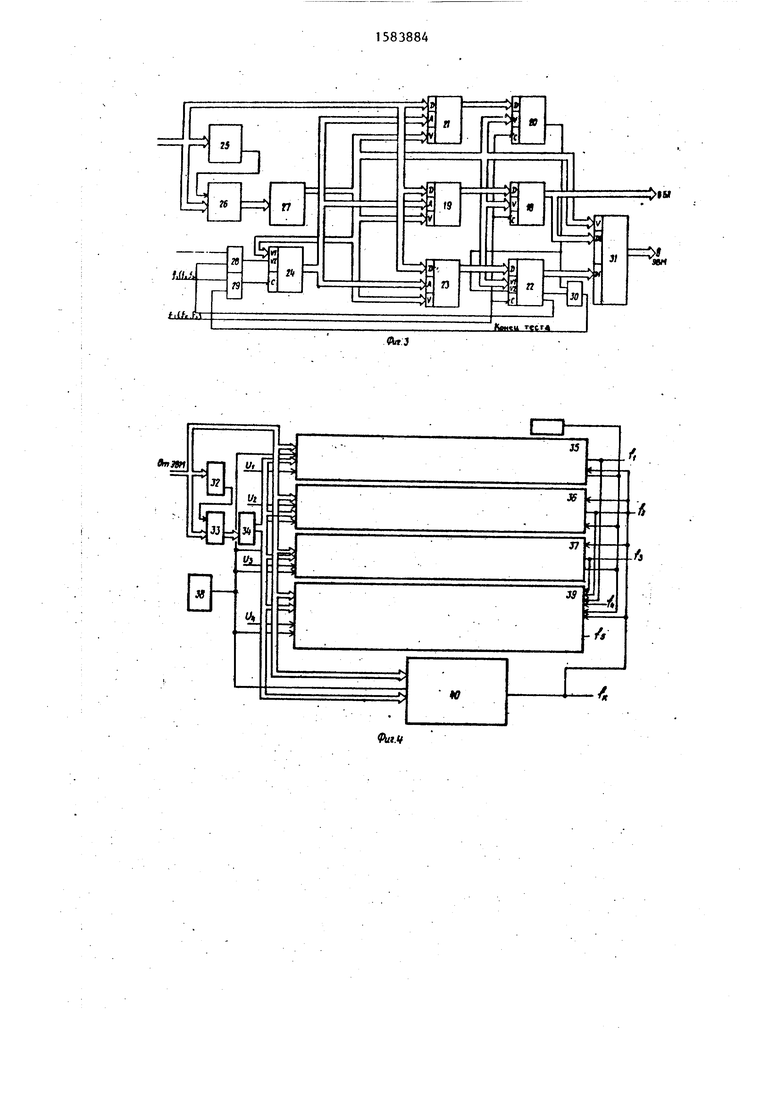

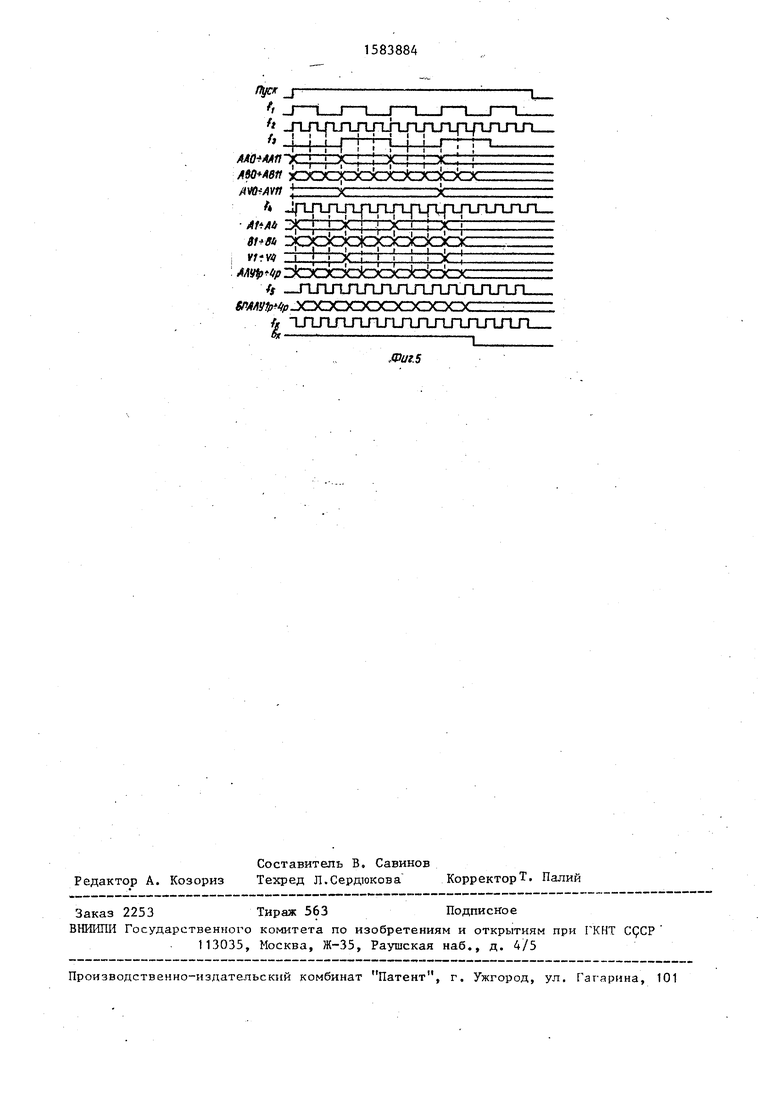

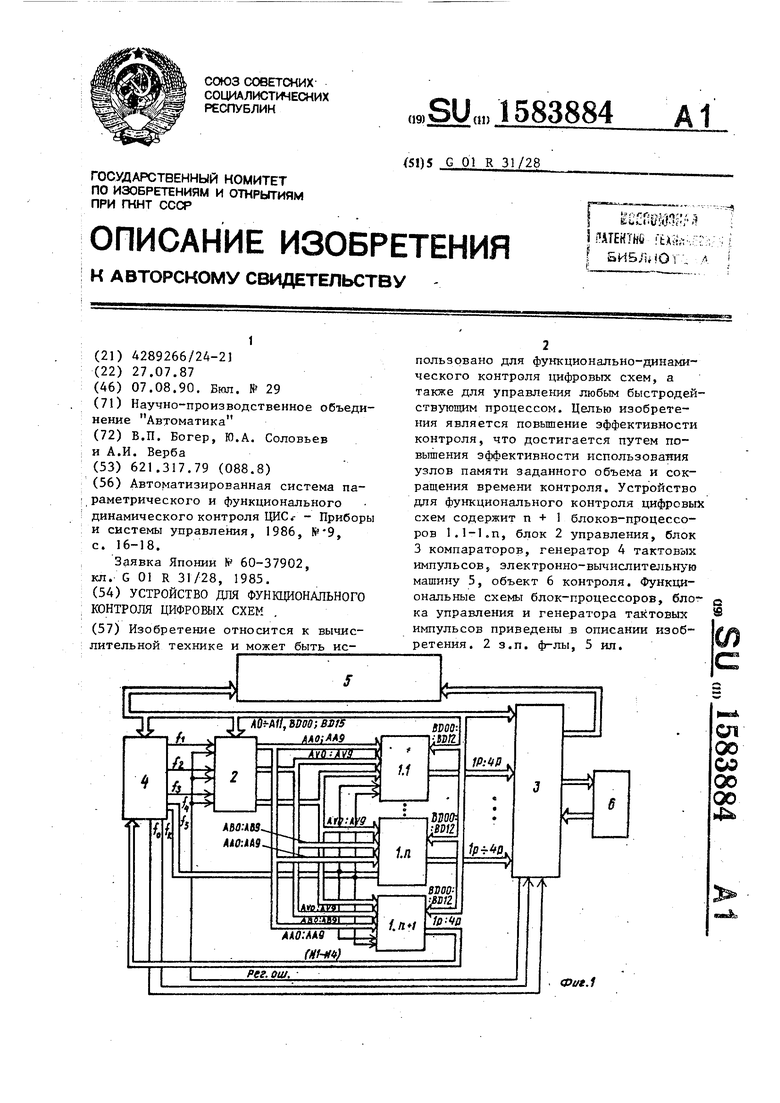

На фиг.1 изображена структурная схема устройства для функционального контроля цифровых схем; на фиг„2-4 - структурные схемы блоков-процессоров блока управления, генератора тактовых импульсов соответственно; на фиг.5 - временные диаграммы работы устройства.

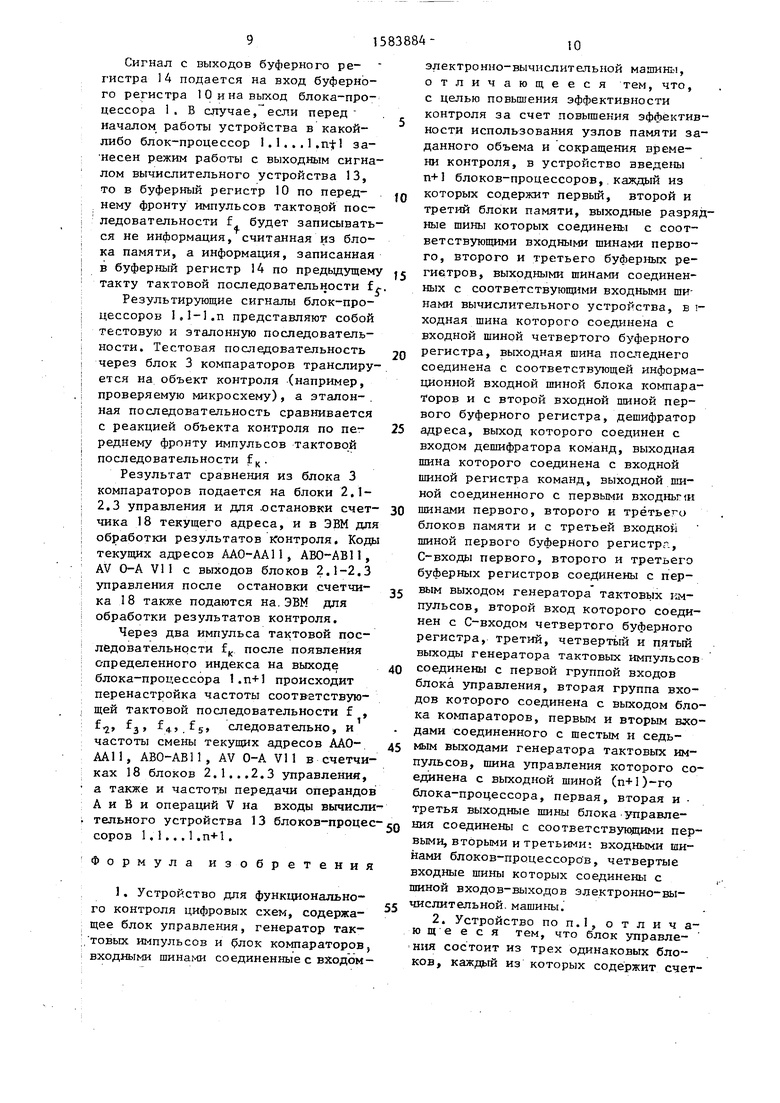

Устройство содержит n t 1 блоков- процессоров l.l-l.n+1, блок 2 управ

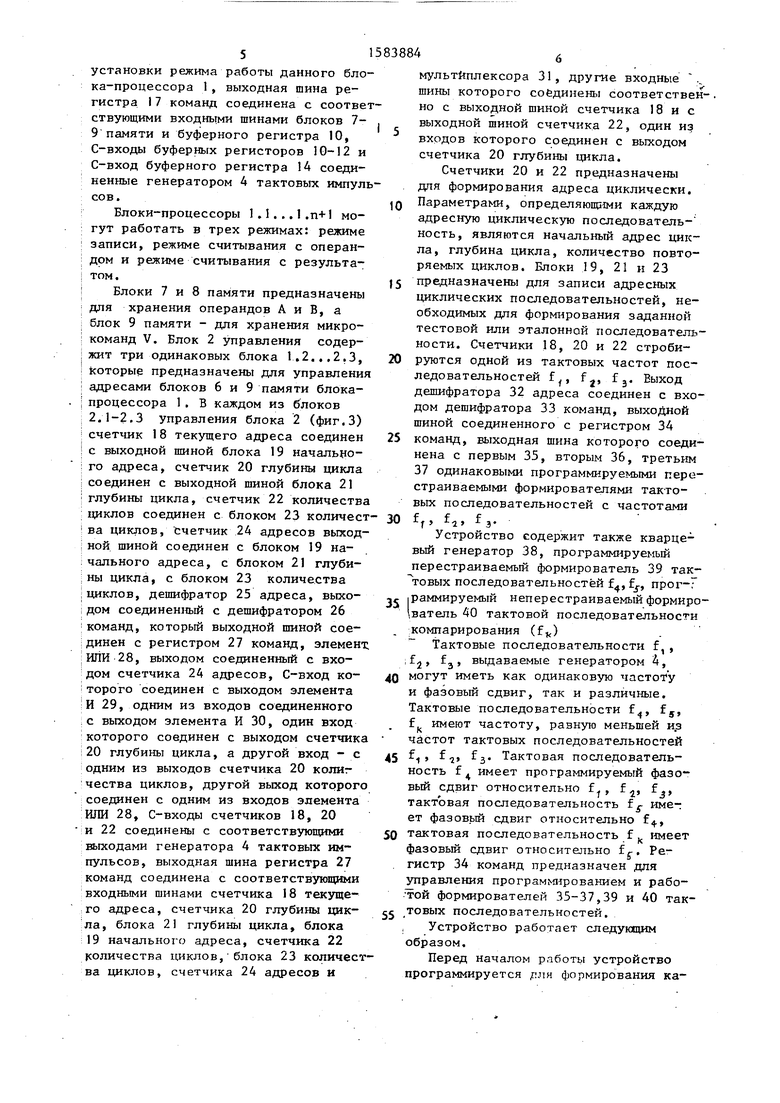

ления, блок 3 компараторов, генератор 4 тактовых импульсов, электронно-вычислительную машину (ЭВМ) 5, объект 6 контроля. Каждый блок-процессор l.l-l.n+1 (фиг.2) содержит первый 7, второй 8 и третий 9 блоки памяти, первый 10, второй 11 и третий 12 буферные регистры, вычислительное устройство 13, четвертый буферный регистр 14, дешифраторы адреса 15 и команд 16, регистр 17 команд

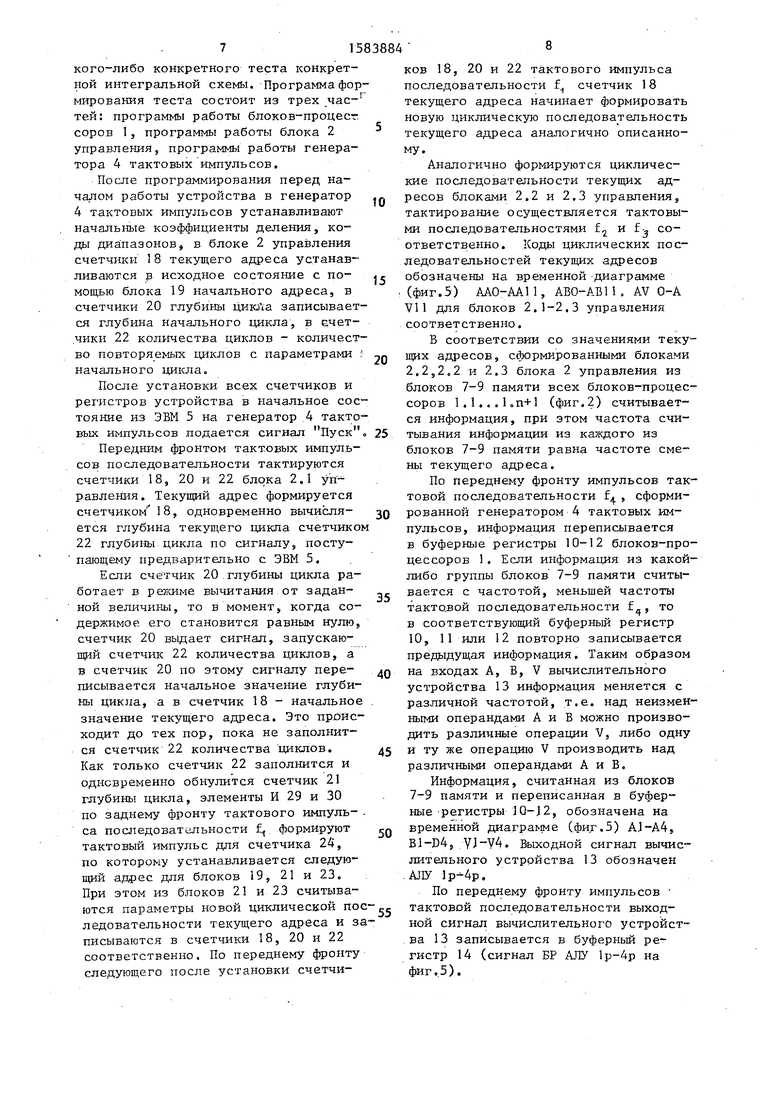

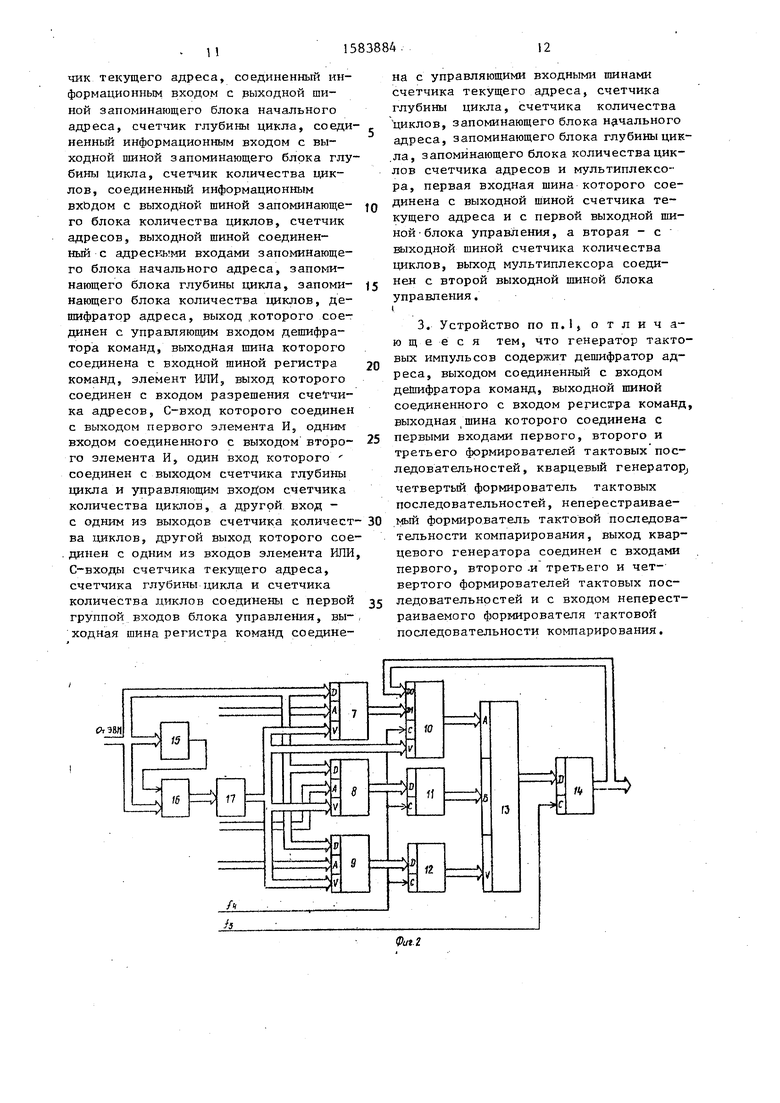

Каждый из блоков 2.1-2.3 блока 2 управления (фиг.З) содержит счетчик 18 текущего адреса, запоминающий блок 19 начального адреса, счетчик

20глубины цикла, запоминающий блок

21глубины цикла, счетчик 22 количества циклов, запоминающий блок 23 количества циклов, счетчик 24 адресов, дешифраторы адреса 25 и команд 26, регистр 27 команд, элемент ИЛИ 28, первый 29 и второй 30 элементы И, мультиплексор 31.

Генератор 4 тактовых импульсов предназначен для тактирования блоков процессоров 1.1...1.П+1, блоков управления 2 и компараторов 3 и содержит дешифраторы адреса 32, и команд 33, регистр 34 команд, первый 35, второй 36 и третий 37 одинаковые программируемые перестраиваемые формирователи тактовых последовательностей, кварцевый генератор 38f программируемый перестраиваемый формирог ватель 39 тактовых последовательностей и программируемый формирователь 40 тактовых последовательностей.

0

5

Выходные шины блока 2 управления соединены с соответствующими входными шинами блоков-процессоров 1.1- . l.n-M, выходные шины блоков-процессоров 1.1-l.n соединены с входными разрядными шинами блока 3 компараторов f первый выход которого соединен с первыми входами блока 2 управления, вторые входы блока 2 управления соединены с первым, вторым и третьим выходами соответствующих тактовых последовательностей генератора 4 тактовых импульсов, выход опорной тактовой последовательности и выход тактовой последовательности компарирова- ния которого соединены с соответствующими входами блока 3 компараторов, выходная разрядная шина блока-процессора 1,п+1 соединена с соответствующей входной шиной генератора 4 тактовых импульсов, четвертый и пятый выходы тактовых последовательностей которого соединены с соответствующими входами блоков-процессоров 1.1 ... 1,п+1, входные шины данных блоков-процессоров 1.1 ... 1.п+1, блока 2 управления, блока 3 компараторов, генератора 4 тактовых импульсов соединены с вычислительным комплексом (ЭВМ).

Блоки-процессоры 1.1.,.1,п предназначены для формирования четырехразрядных тестовых и эталонных последовательностей. Количество блоков- процессоров 1 выбирается исходя из разрядности необходимой тестовой и эталонной посылок. Один блок-процессор 1.(п+1) необходим для управления генератором 4 тактовых импульсов.

Выходные разрядные шины первого 7, второго 8, третьего 9 блоков па- ;мяти соединены с соответствующими (входными шинами первого 10, второго 5 11 и третьего 12 буферных регистров, выходными шинами соединенных с соответствующими входными шинами вычислительного устройства 13, выходная шина которого соединена с входной шиной четвертого буферного регистра 14, выходной шиной соединенного с блоком 3 компараторов и с второй входной шиной буферного регистра 10. Дешифратор 15 адреса входной шиной соединен с ЭВМ 5, а выходом - с входом дешифратора 16 команд, входная шина которого соединена с ЭВМ 5, а выходная - с входной шиной регистра 17 команд, предназначенного для

0

5

0

0

5

установки режима работы данного блока-процессора 1, выходная шина регистра 17 команд соединена с соответствующими входными шинами блоков 7- 9 памяти и буферного регистра 10, С-входы буферных регисторов 10-12 и С-вход буферного регистра 1А соединенные генератором 4 тактовых импульсов.

Блоки-процессоры 1.1...1.П+1 могут работать в трех режимах: режиме записи, режиме считывания с операндом и режиме считывания с результатом.

Блоки 7 и 8 памяти предназначены для хранения операндов А и В, а блок 9 памяти - для хранения микрокоманд V. Блок 2 управления содержит три одинаковых блока 1.2...2.3, которые предназначены для управления адресами блоков 6 и 9 памяти блока- процессора 1. В каждом из блоков 2.1-2.3 управления блока 2 (фиг.З) счетчик 18 текущего адреса соединен с выходной шиной блока 19 начального адреса, счетчик 20 глубины цикла соединен с выходной шиной блока 21 глубины цикла, счетчик 22 количества циклов соединен с блоком 23 количества циклов, счетчик 24 адресов выходной шиной соединен с блоком 19 начального адреса, с блоком 21 глубины цикла, с блоком 23 количества циклов, дешифратор 25 адреса, выходом соединенный с дешифратором 26 команд, который выходной шиной соединен с регистром 27 команд, элемент ИЛИ 28, выходом соединенный с входом счетчика 24 адресов, С-вход которого соединен с выходом элемента И 29, одним из входов соединенного с выходом элемента И 30, один вход которого соединен с выходом счетчика 20 глубины цикла, а другой вход - с одним из выходов счетчика 20 колиг чества циклов, другой выход которого соединен с одним из входов элемента ИЛИ 28, С-входы счетчиков 18, 20 и 22 соединены с соответствующими выходами генератора 4 тактовых импульсов, выходная шина регистра 27 команд соединена с соответствующими входными шинами счетчика 18 текущего адреса, счетчика 20 глубины цикла, блока 21 глубины цикла, блока 19 начального адреса, счетчика 22 количества циклов, блока 23 количества циклов, счетчика 24 адресов и

5

5

0

5

0

5

0

5

мультиплексора 31, другие входные шины которого соединены соответствен-, но с выходной шиной счетчика 18 и с выходной шиной счетчика 22, сдан из входов которого соединен с выходом счетчика 20 глубины цикла.

Счетчики 20 и 22 предназначены для формирования адреса циклически. Параметрами, определяющими каждую адресную циклическую последовательность, являются начальный адрес цикла, глубина цикла, количество повторяемых циклов. Блоки 19, 21 и 23 предназначены для записи адресных циклических последовательностей, необходимых для формирования заданной тестовой или эталонной последовательности. Счетчики 18, 20 и 22 строби- руются одной из тактовых частот последовательностей ff, f2, f3. Выход дешифратора 32 адреса соединен с входом дешифратора 33 команд, выходной шиной соединенного с регистром 34 команд, выходная шина которого соединена с первым 35, вторым 36, третьим 37 одинаковыми программируемыми перестраиваемыми формирователями тактовых последовательностей с частотами

f -i з«

Устройство содержит также кварцевый генератор 38, программируемый перестраиваемый формирователь 39 так- товых последовательностей прог-Г |раммируемый неперестраиваемый формирователь 40 тактовой последовательности компарирования (fk) Тактовые последовательности f t, f2, f э , выдаваемые генератором 4, могут иметь как одинаковую частоту и фазовый сдвиг, так и различные. Тактовые последовательности f, f5, f имеют частоту, равную меньшей и.з частот тактовых последовательностей Е3. Тактовая последователь- имеет программируемый фазовый сдвиг относительно f, f2, f, тактовая последовательность fg имет ет фазовый сдвиг относительно f, тактовая последовательность f K имеет фазовый сдвиг относительно . Регистр 34 команд предназначен для управления программированием и работой формирователей 35-37,39 и 40 тактовых последовательностей.

Устройство работает следующим образом.

Перед началом работы устройство программируется рлн формирования ность f

кого-либо конкретного теста конкретной интегральной схемы. Программа формирования теста состоит из трех час-г тей: программы работы блоков-процест соров 1, программы работы блока 2 управления, программы работы генератора 4 тактовых импульсов.

После программирования перед началом работы устройства в генератор 4 тактовых импульсов устанавливают начальные коэффициенты деления, коды диапазонов, в блоке 2 управления счетчики 18 текущего адреса устанавливаются в исходное состояние с помощью блока 19 начального адреса, в счетчики 20 глубины цикла записывается глубина начального цикла, в счетчики 22 количества циклов - количество повторяемых циклов с параметрами начального цикла.

После установки всех счетчиков и регистров устройства в начальное состояние из ЭВМ 5 на генератор 4 тактовых импульсов подается сигнал Пуск, Передним фронтом тактовых импульсов последовательности тактируются счетчики 18, 20 и 22 блока 2.1 управления. Текущий адрес формируется счетчиком 18, одновременно вычисляется глубина текущего цикла счетчиком 22 глубины цикла по сигналу, поступающему предварительно с ЭВМ 5.

Если счетчик 20 глубины цикла работает в режиме вычитания от заданной величины, то в момент, когда содержимое его становится равным нулю, счетчик 20 выдает сигнал, запускающий счетчик 22 количества циклов, а в счетчик 20 по этому сигналу переписывается начальное значение глубины цикла, а в счетчик 18 - начальное значение текущего адреса. Это происходит до тех пор, пока не заполнится счетчик 22 количества циклов. Как только счетчик 22 заполнится и одновременно обнулится счетчик 21 глубины цикла, элементы И 29 и 30 по заднему фронту тактового импуль- . са последовательности Ј, формируют тактовый импульс для счетчика 24, по которому устанавливается следующий адрес для блоков 19, 21 и 23. При этом из блоков 21 и 23 считыва10

15

20

25

30

35

40

45

50

ков 18, 20 и 22 тактового импульса последовательности f, счетчик 18 текущего адреса начинает формироват новую циклическую последовательност текущего адреса аналогично описанно му.

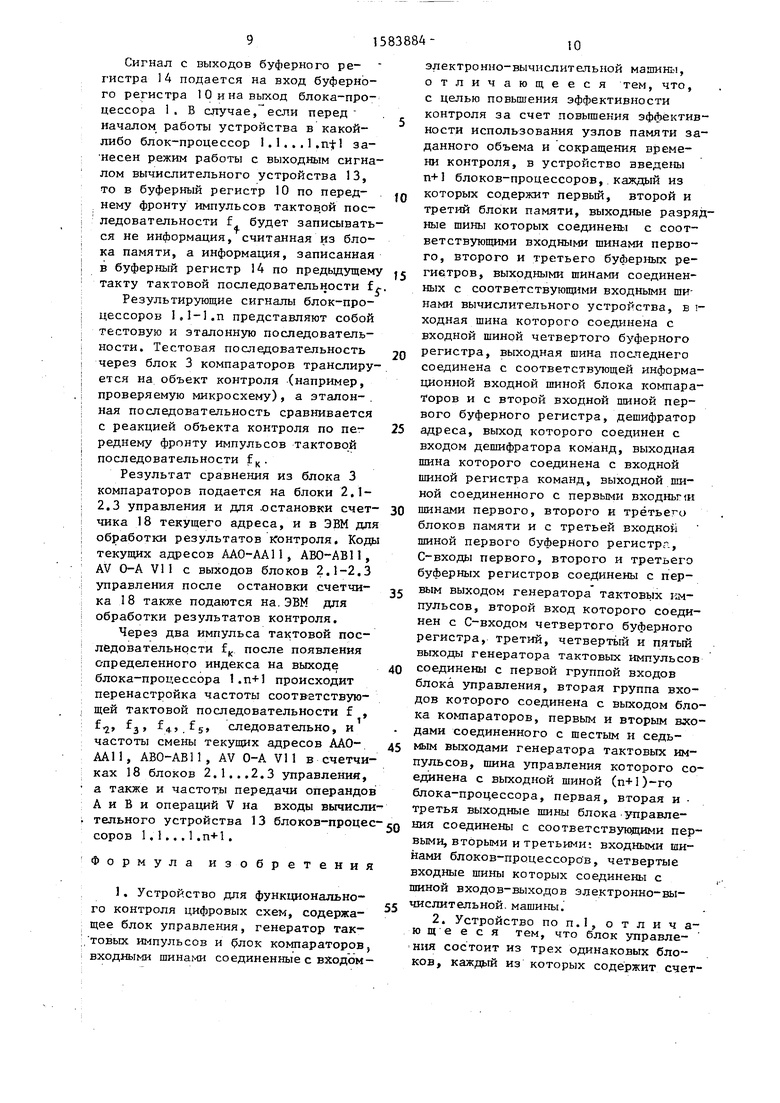

Аналогично формируются циклические последовательности текущих адресов блоками 2.2 и 2,3 управления, тактирование осуществляется тактовы ми последовательностями Јг и f, соответственно. Коды циклических пос ледовательностей текущих адресов обозначены на временной диаграмме (фиг.5) ААО-ААП, АВО-АВ11. AV О-А VII для блоков 2.1-2.3 управления соответственно.

В соответствии со значениями тек щих адресов, сформированными блокам 2.2,2.2 и 2.3 блока 2 управления из блоков 7-9 памяти всех блоков-проце соров 1.1...1.П+1 (фиг.2) считывает ся информация, при этом частота счи тывания информации из каждого из блоков 7-9 памяти равна частоте сме ны текущего адреса.

По переднему фронту импульсов та товой последовательности f, сформи рованной генератором 4 тактовых импульсов, информация переписывается в буферные регистры 10-12 блоков-пр цессоров 1. Если информация из како либо группы блоков 7-9 памяти считы вается с частотой, меньшей частоты тактовой последовательности f, то в соответствующий буферный регистр 10, 11 или 12 повторно записывается предыдущая информация. Таким образо на входах А, В, V вычислительного устройства 13 информация меняется с различной частотой, т.е. над неизме ными операндами А и В можно произво дить различные операции V, либо одн и ту же операцию V производить над различными операндами А и В.

Информация, считанная из блоков 7-9 памяти и переписанная в буферные регистры 1Q-J2, обозначена на временной диаграмме (фиг.5) А1-А4, В1-Р4, . Выходной сигнал вычис лительного устройства 13 обозначен АЛУ 1р-4р.

По переднему фронту импульсов

ются параметры новой циклической пос- тактовой последовательности выходледовательности текущего адреса и записываются в счетчики 18, 20 и 22 соответственно. По переднему фронту следующего после установки счетчинои сигнал вычислительного устройст ва 13 записывается в буферный регистр 14 (сигнал БР АЛУ 1р-4р на фиг,5).

р-гт ттсо, ом

, е. 10

15

20

25

30

35

40

45

50

8

ков 18, 20 и 22 тактового импульса последовательности f, счетчик 18 текущего адреса начинает формировать новую циклическую последовательность текущего адреса аналогично описанному.

Аналогично формируются циклические последовательности текущих адресов блоками 2.2 и 2,3 управления, тактирование осуществляется тактовыми последовательностями Јг и f, соответственно. Коды циклических последовательностей текущих адресов обозначены на временной диаграмме (фиг.5) ААО-ААП, АВО-АВ11. AV О-А VII для блоков 2.1-2.3 управления соответственно.

В соответствии со значениями текущих адресов, сформированными блоками 2.2,2.2 и 2.3 блока 2 управления из блоков 7-9 памяти всех блоков-процессоров 1.1...1.П+1 (фиг.2) считывается информация, при этом частота считывания информации из каждого из блоков 7-9 памяти равна частоте смены текущего адреса.

По переднему фронту импульсов тактовой последовательности f, сформированной генератором 4 тактовых импульсов, информация переписывается в буферные регистры 10-12 блоков-процессоров 1. Если информация из какой- либо группы блоков 7-9 памяти считывается с частотой, меньшей частоты тактовой последовательности f, то в соответствующий буферный регистр 10, 11 или 12 повторно записывается предыдущая информация. Таким образом на входах А, В, V вычислительного устройства 13 информация меняется с различной частотой, т.е. над неизменными операндами А и В можно производить различные операции V, либо одну и ту же операцию V производить над различными операндами А и В.

Информация, считанная из блоков 7-9 памяти и переписанная в буферные регистры 1Q-J2, обозначена на временной диаграмме (фиг.5) А1-А4, В1-Р4, . Выходной сигнал вычислительного устройства 13 обозначен АЛУ 1р-4р.

По переднему фронту импульсов

нои сигнал вычислительного устройства 13 записывается в буферный регистр 14 (сигнал БР АЛУ 1р-4р на фиг,5).

Сигнал с выходов буферного регистра 14 подается на вход буферного регистра Юинавыход блока-процессора 1. В случае,если перед началом работы устройства в какой- либо блок-процессор l.l...l.nfl занесен режим работы с выходным сигналом вычислительного устройства 13, то в буферный регистр 10 по перед- нему фронту импульсов тактов.ой последовательности f будет записываться не инАормация, считанная из блока памяти, а информация, записанная в буферный регистр 14 по предыдущему такту тактовой последовательности f/Результирующие сигналы блок-процессоров I.l-l.n представляют собой тестовую и эталонную последовательности. Тестовая последовательность через блок 3 компараторов транслируется на объект контроля (например, проверяемую микросхему), а эталонная последовательность сравнивается с реакцией объекта контроля по пе- реднему фронту импульсов тактовой последовательности fK.

Результат сравнения из блока 3 компараторов подается на блоки 2.1- 2.3 управления и для остановки счет- чика 18 текущего адреса, и в ЭВМ для обработки результатов контроля. Коды текущих адресов ААО-ААН , АВО-АВ11, AV 0-А VII с выходов блоков 2.1-2.3 управления после остановки счетчи- ка 18 также подаются на ЭВМ для обработки результатов контроля.

Через два импульса тактовой последовательности Јк после появления определенного индекса на выходе блока-процессора 1 .п+1 происходит перенастройка частоты соответствующей тактовой последовательности f , f, f 3 , f4, f5, следовательно, и частоты смены текущих адресов ААО- АА11, АВО-АВ11, AV 0-А VI1 в счетчиках 18 блоков 2.1...2.3 управления, а также и частоты передачи операндов А и В и операций V на входы вычислительного устройства 13 блоков-процес соров 1. 1... 1.п+1.

Формула изобретения

1. Устройство для функционально-

го контроля цифровых схем, содержа щее блок управления, генератор тактовых импульсов и блок компараторов, входными шинами соединенные с входом -

JQ.

2025

30 ,г

4045 -сп

55

электронно-вычислительной машины, отличающееся тем, что, с целью повышения эффективности контроля за счет повышения эффективности использования узлов памяти заданного объема и сокращения времени контроля, в устройство введены п+1 блоков-процессоров, каждый из которых содержит первый, второй и третий блоки памяти, выходные разрядные шины которых соединены с соответствующими входными шинами первого, второго и третьего буферных ре- гиетров, выходными шинами соединенных с соответствующими входными ши нами вычислительного устройства, в - ходная шина которого соединена с входной шиной четвертого буферного регистра, выходная шина последнего соединена с соответствующей информационной входной шиной блока компараторов и с второй входной шиной первого буферного регистра, дешифратор адреса, выход которого соединен с входом дешифратора команд, выходная шина которого соединена с входной шиной регистра команд, выходной шиной соединенного с первыми входными шинами первого, второго и третьего блоков памяти и с третьей входной шиной первого буферного регистрг, С-входы первого, второго и третьего буферных регистров соединены с первым выходом генератора тактовых км- пульсов, второй вход которого соединен с С-входом четвертого буферного регистра, третий, четвертый и пятый выходы генератора тактовых импульсов соединены с первой группой входов блока управления, вторая группа входов которого соединена с выходом блока компараторов, первым и вторым входами соединенного с шестым и седьмым выходами генератора тактовых импульсов, шина управления которого соединена с выходной шиной (п+1)-го блока-процессора, первая, вторая и третья выходные шины блока управления соединены с соответствующими первыми, вторыми и третьими; входными шинами блоков-процессоров, четвертые входные шины которых соединены с шиной входов-выходов электронно-вычислительной машины.

2. Устройство поп.1, отличающееся тем, что блок управления состоит из трех одинаковых блоков, каждый из которых содержит счетчик текущего адреса, соединенный информационным входом с выходной шиной запоминающего блока начального адреса, счетчик глубины цикла, соединенный информационным входом с выходной шиной запоминающего блока глубины цикла, счетчик количества циклов, соединенный информационным входом с выходной шиной запоминающе- го блока количества циклов, счетчик адресов, выходной шиной соединенный с адресными входами запоминающего блока начального адреса, запоминающего блока глубины цикла, эапоми- нающего блока количества циклов, дешифратор адреса, выход которого соединен с управляющим входом дешифратора команд, выходная шина которого соединена с входной шиной регистра команд, элемент ИЛИ, выход которого соединен с входом разрешения счетчика адресов, С-вход которого соединен с выходом первого элемента И5 одним входом соединенного с выходом второ- го элемента И, один вход которого соединен с выходом счетчика глубины цикла и управляющим входом счетчика количества циклов, а другой вход - с одним из выходов счетчика количест ва циклов, другой выход которого соединен с одним из входов элемента ИЛИ С-входы счетчика текущего адреса, счетчика глубины цикла и счетчика количества ликлов соединены с первой группой входов блока управления, выходная шина регистра команд соединена с управляющими входными шинами счетчика текущего адреса, счетчика глубины цикла, счетчика количества циклов, запоминающего блока начального адреса, запоминающего блока глубины цикла, запоминающего блока количества циклов счетчика адресов и мультиплексора, первая входная шина которого соединена с выходной шиной счетчика текущего адреса и с первой выходной шиной блока управления, а вторая - с выходной шиной счетчика количества циклов, выход мультиплексора соединен с второй выходной шиной блока

управления.

(

3. Устройство по п.1, отличающееся тем, что генератор тактовых импульсов содержит дешифратор адреса, выходом соединенный с входом дешифратора команд, выходной шиной соединенного с входом регистра команд выходная шина которого соединена с первыми входами первого, второго и третьего формирователей тактовых последовательностей, кварцевый генератор,

четвертый формирователь тактовых последовательностей, неперестраиваемый формирователь тактовой последовательности компарирования, выход кварцевого генератора соединен с входами первого, второго .и третьего и четвертого формирователей тактовых последовательностей и с входом неперестраиваемого формирователя тактовой последовательности компарирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

Изобретение относится к вычислительной технике и может быть использовано для функционально-динамического контроля цифровых схем, а также для управления любым быстродействующим процессом. Целью изобретения является повышение эффективности контроля, что достигается путем повышения эффективности использования узлов памяти заданного объема и сокращения времени контроля. Устройство для функционального контроля цифровых схем содержит N+1 блоков-процессоров 1.1-1.N, блок 2 управления, блок 3 компараторов, генератор 4 тактовых импульсов, электронно-вычислительную машину 5, объект 6 контроля. Функциональные схемы блок-процессоров, блока управления и генератора тактовых импульсов приведены в описании изобретения. 2 з.п.ф-лы, 5 ил.

ЛЭШ1

к-Ь

1Ы

Л

/J

T-flfTJl-njTJirirLrLflf

t LI(

JГ

ААО+АЛЯ к .. -... x ; j -згг

«MW DOc cxrot Kdcfcx:

AVfcAvn I -- у- ;:jx

41-f4 MM4MMMM1-J1-njl-n

АКАЛ DJ; j /JC4i 3;ciizii/j j

«y« podcx yxpfaiocx:

wrw -ix.. j. ii

мурщ Dfcx oclcxDckziaicx

// JlJTJTJTnjbTlJlJTJTnJTJTJ-L. юмтрйл y-y-y-vnorv-y-y-y-v

ЯJlJтлJъruгJглJтлJ J Jгл

JГ

| Автоматизированная система параметрического и функционального динамического контроля - Приборы и системы управления, 1986, № 9, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-08-07—Публикация

1987-07-27—Подача