группы информационных входов соединены соответственно с шинами единичного и нулевого потенциалов, группы 1195351 выходов первого и второго коммутаторов образуют информационный- выход блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для согласования интерфейсов | 1988 |

|

SU1688249A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для обмена информацией | 1985 |

|

SU1264196A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

.УСТРОЙСТВО ДЛЯ ОБМЕНА ИИФОРМАЦИЕЙ МЕЖДУ МИКРОЭВМ И ПЕРИФЕРИЙНЫМИ УСТРОЙСТВАМИ, содержащее оперативный запоминающий блок, постоянный запоминающий блок, объединенные адресной, управляющей и информационной шинами, группу интерфейсных блоков , информационные и управляющие входы которых соединены с выходными управляющей и информацинной шинами микроэвм, отличающееся тем, что, с целью .повышения производительности и достоверности работы, в него введены два дешифратора, ре-, гистр базового адреса, блок формирования контрольных комбинаций, элемент И, элемент ИЛИ, причем группа входов первого дешифратора соединена с выходной адресной шиной микроЭВМ, а первый, второй и третий выходы соединены соответственно с первыми входами элемента ИЛИ, второго дешифратора и элемента И, второй вход которого соединен с разрядом записи выходной управляющей шины мйкроЭВМ, а выход соединен с входом записи регистра базового адреса, группа информационных входов которого соединена с выходнойинформационной шиной микроэвм, первый и второй выходы регистра базового адреса соединены соответственно с вторым входом втЪрого дешифратора и входом разрешения блока формирования контрольных комбинаций, первая и вторая rpyrt- пы входов которого соединены соответственно с выходными адресной и управляющей щинами микроЭВМ, а выход признака диагностики и информа- . ционный выход соединены соответственно с вторым входом элемента ИЛИ и входной информационной шиной микро- i ЭВМ, выход элемента ИЛИ соединен с входом блокировки работы оператив(Л ного запоминающего блока, выход второго дешифратора соединен с входами выборки интерфейсных блоков группы. 2. Устройство по п.1, о т л и ча.ющееся тем, что блок формирования контрольных комбинаций содержит элемент НЕ, элементы И и коммутаторы, причем четные разряды пер: вой группы входов блока соединены с сл первой группой входов первого эле00 мента И, а нечетные разряды первой ел группы входов блока через элемент НЕ соединены с второй группой входов первого элемента И, выход которого соединен с первым входом второго элемента И, второй вход которого является входом разрешения блока, а выход является выходом признака диагностики блока и соединен с управляющими входами первого и второго коммутаторов, первые группы информационных входов которых образуют вторую группу входов блока, а вторые

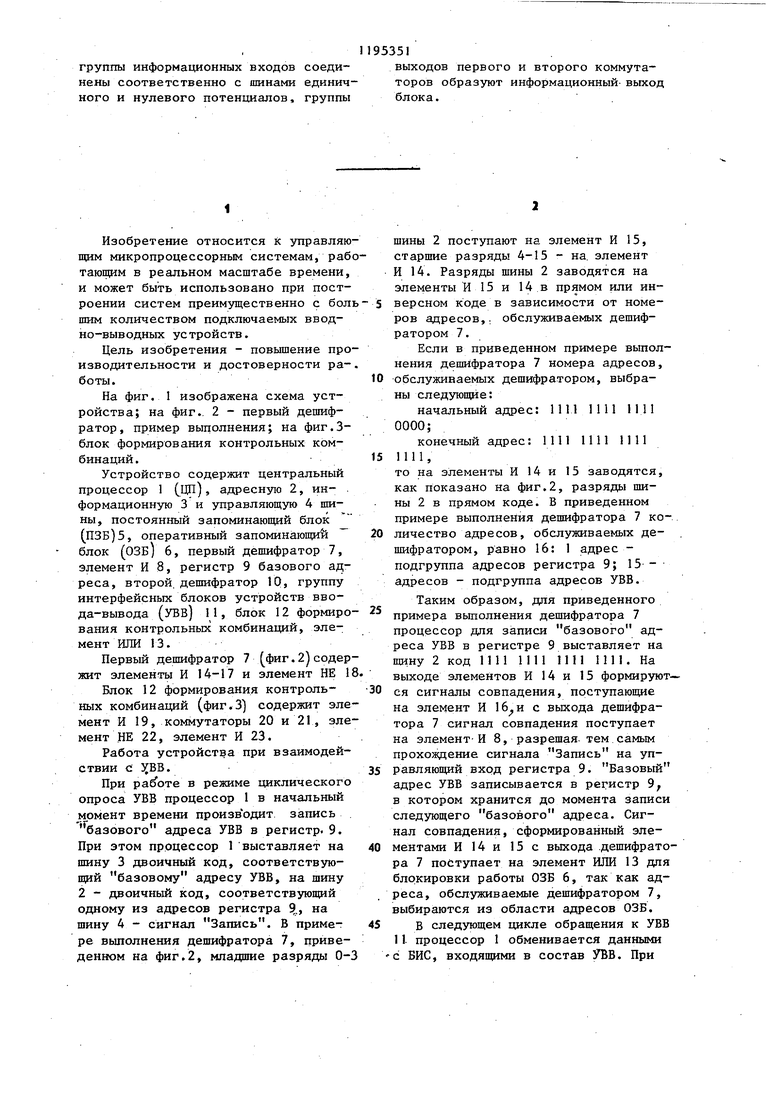

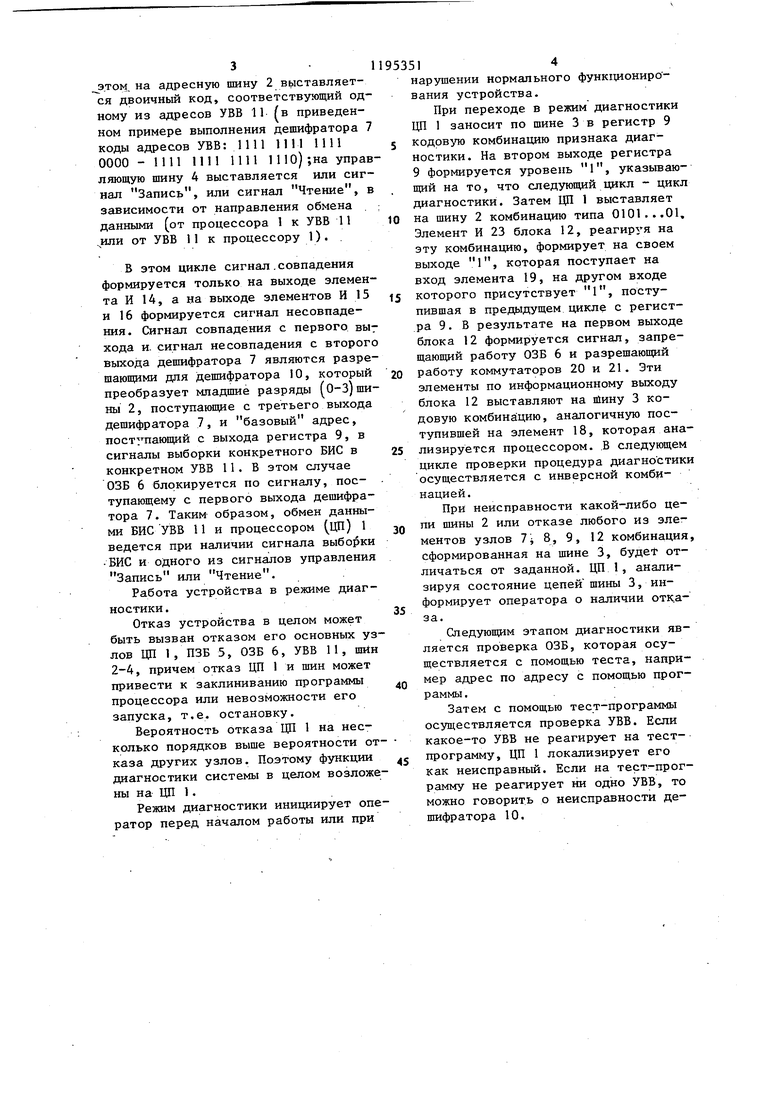

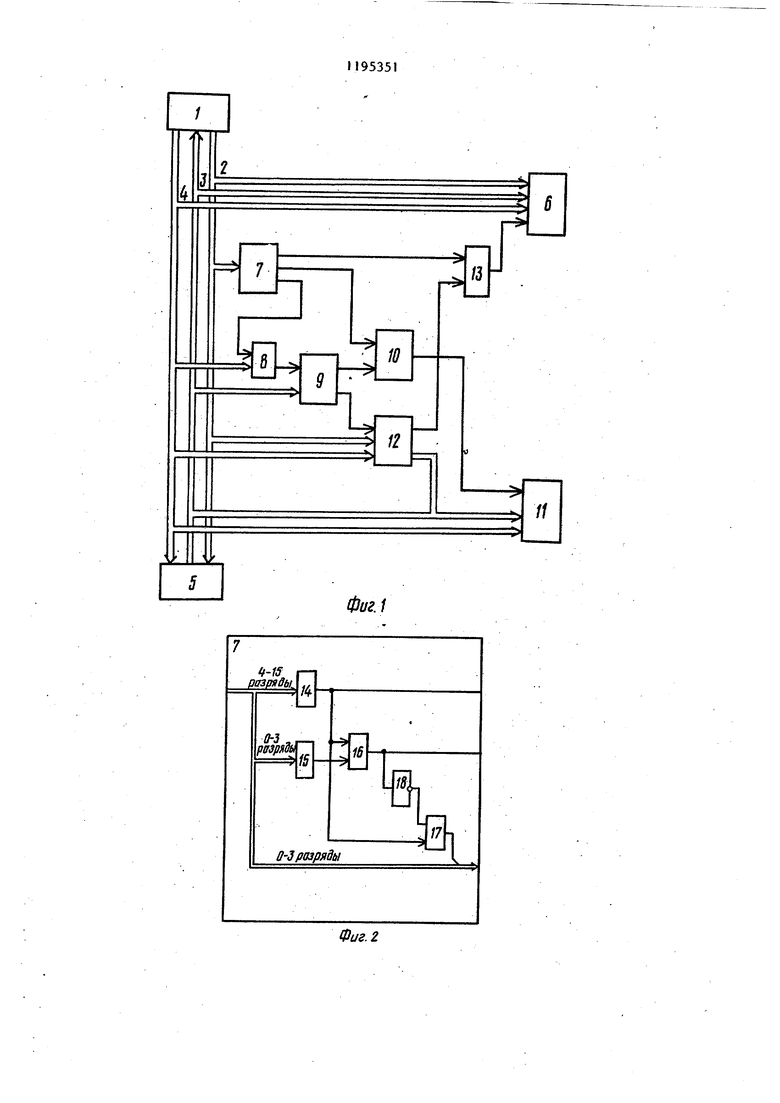

Изобретение относится к управляю щим микропроцессорным системам, раб таюпщм в реальном масштабе времени и может быть использовано при построении систем преимущественно с бол шим количеством подключаемых вводно-выводных устройств. Цель изобретения - повышение про изводительности и достоверности работы. На фиг. 1 изображена схема устройства; на фиг.. 2 - первый дешифратор, пример выполнения; на фиг.Зблок формирования контрольных комбинаций. Устройство содержит центральный процессор 1 (ЦП), адресную 2, информационную 3 и управляющую 4 шины, постоянный запоминающий блок (ПЗБ)5, оперативный запоминающий блок (ОЗБ) 6, первый дешифратор 7, элемент И 8, регистр 9 базового адреса, второй, дешифратор 10, группу интерфейсных блоков устройств ввода-вывода (УВВ) 11, блок 12 формиро вания контрольных комбинаций, элемент ИЛИ 13. Первый дешифратор 7 (фиг. 2) содер жит элементы И 14-17 и элемент НЕ 1 Блок I2 формирования контрольных комбинаций (фиг.3) содержит эле мент И 19, коммутаторы 20 и 21, эле мент НЕ 22, элемент И 23. Работа устройства при взаимодействии с 3JBB. При в режиме циклического опроса УВВ процессор 1 в начальный момент времени произвЪдит запись базового адреса УВВ в регистр, 9. При этом процессор 1 выставляет на шину 3 двоичный код, соответствующий базовому адресу УВВ, на шину 2 - двоичный код, соответствующий одному из адресов регистра 9,, на шину 4 - сигнал Запись. В примере выполнения дешифратора 7, приведенном на фиг.2, младшие разряды 0шины 2 поступают на элемент И 15, старшие разряды 4-15 - на. элемент И 14. Разряды шины 2 заводятся на элементы И 15 и 14 в прямом или инверсном коде в зависимости от номеров адресов,.. обслуживаемых дешифратором 7. Если в приведенном примере выполнения дешифратора 7 номера адресов, обслуживаемых дешифратором, выбраны следующие: начальный адрес: 1111 1111 1111 0000; конечный адрес: 1111 1111 1111 1111, то на элементы И 14 и 15 заводятся, как показано на фиг.2, разряды шины 2 в прямом коде. В приведенном примере выполнения дешифратора 7 количество адресов, обслуживаемых дешифратором, равно 16: 1 адрес подгруппа адресов регистра 9; 15 адресов - подгруппа адресов УВВ. Таким образом, дпя приведенного примера вьтолнения дешифратора 7 процессор для записи базового адреса УВВ в регистре 9 выставляет на шину 2 код 1111 1111 1111 1111. На выходе элемеИтов И 14 и 15 формируют- ся сигналы совпадения, поступающие на элемент И с вькода дешифратора 7 сигнал совпадения поступает на элемент-И 8, разрешая, тем самым прохождение сигнала Запись на управляющий вход регистра 9. Базовый адрес УВВ записывается в регистр 9 в котором хранится до момента записи следующего базового адреса. Сигнал совпадения, сформированный элементами И 14 и 15 с выхода .дешифратора 7 поступает на элемент ИЛИ 13 для блокировки работы ОЗБ 6, так как адреса, обслуживаемые дешифратором 7, выбираются из области адресов ОЗБ. Б следующем цикле обращения к УВВ 11- процессор 1 обменивается данными С БИС, входящими в состав УВВ. При

этом. на адресную шину 2 выставляется двоичный код, соответствующий одному из адресов УВВ 11 (в приведенном примере выполнения дешифратора 7 коды адресов УВВ: 1111 1111 1111 0000 - 1111 1111 1111 111 о);на управляющую шину 4 выставляется или сигнал Запись, или сигнал Чтение, в зависимости от направления обмена данными (от процессора 1 к УВВ 11 ,шпл от УВВ 11 к процессору 1). .

В этом цикле сигнал.совпадения формируется только на выходе элемента И 14, а на выходе элементов И 15 и 16 формируется сигнал несовпадения. Сигнал совпадения с первого вы7 хода и. сигнал несовпадения с второго выхода дешифратора 7 являются разрешаюш 1ми для дешифратора 10, который преобразует младшие разряды (О-З) шины 2, поступающие с третьего выхода дешифратора 7, и базовый адрес, поступающий с выхода регистра 9, в сигналы выборки конкретного БИС в конкретном УВВ 11. В этом случае ОЗБ 6 блокируется по сигналу, поступающему с первого выхода дешифратора 7. Таким образом, обмен данными БИС УВВ 11 и процессором (ЦП) 1 ведется при наличии сигнала выборки БИС и одного из сигналов управления Запись или Чтение.

Работа устройства в режиме диагностики.

Отказ устройства в целом может быть вызван отказом его основных узлов ЦП 1, ПЗБ 5, ОЗБ 6, УВВ 11, шин 2-4, причем отказ ЦП 1 и шин может привести к заклиниванию программы процессора или невозможности его запуска, т.е. остановку.

Вероятность отказа ЦП 1 на несколько порядков выше вероятности отказа других узлов. Поэтому функции диагностики системы в целом возложены на ЦП 1.

Режим диагностики инициирует оператор перед началом работы или при

953514

нарушении нормального функгдаонирования устройства.

При переходе в режим диагностики ЦП 1 заносит по шине 3 в регистр 9 5 кодрв то комбинацию признака диагностики. На втором выходе регистра 9 формируется уровень 1, указывающий на то, что следующий цикл - цикл диагностики. Затем ЦП 1 выставляет

0 на шину 2 комбинацию типа 0101...01, Элемент И 23 блока 12, реагируя на эту комбинацию, формирует на своем выходе 1, которая поступает на вход элемента 19, на другом входе

5 которого присутствует 1, поступившая в предыдущем цикле с регистра 9. В результате на первом выходе блока 12 формируется сигнал, запрещающий работу ОЗБ 6 и разрешающий

0 работу коммутаторов 20 и 21. Эти элементы по информационному выходу блока 12 выставляют на Шину 3 кодовую комбинацию, аналогичную поступившей на элемент 18, которая анализируется процессором. .В следующем цикле проверки процедура диагностики осуществляется с инверсной комбинацией.

При неисправности какой либо цепи шины 2 или отказе любого из элементов узлов 7j 8, 9, 12 комбинация, сформированная на щине 3, будет отличаться от заданной. ЦП 1, анализируя состояние цепейщины 3, информирует оператора о наличии откдза.

Следуюшзим этапом диагностики является проверка ОЗБ, котора.я осуществляется с помощью теста, например адрес по адресу с помощью программы.

Затем с помощью тест-программы осуществляется проверка УВВ. Если какое-то УВВ не реагирует на тестпрограмму, ЦП 1 локализирует его как неисправный. Если на тест-программу не реагирует ни одно УВВ, то можно говорить о неисправности дешифратора 10.

W

T

2i

| Микропроцессорная система с изолированным вводом-вьшодом | |||

| Каталог фирмы Intel, США, 1977 | |||

| Микропроцессорная система, использующая способ ввода-вьюода с наложением на память | |||

| Каталог фирмы Intel, США, 1977. |

Авторы

Даты

1985-11-30—Публикация

1983-11-05—Подача