обеспечения вычисления всего выходного массива:

,V-

у;

14. k-1

I

где у;,, - значения элементов преобра- зованного массива, х;,- знач«5ния элементов исходного массива, Чк J значения коэффициентов, k число коэффициентов, i, q .

1

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации в реальном масштабе времени.

Цель изобретения - повьшение быстродействия за счет обеспечения параллельного вычисления всего выходного массива у,-Л.

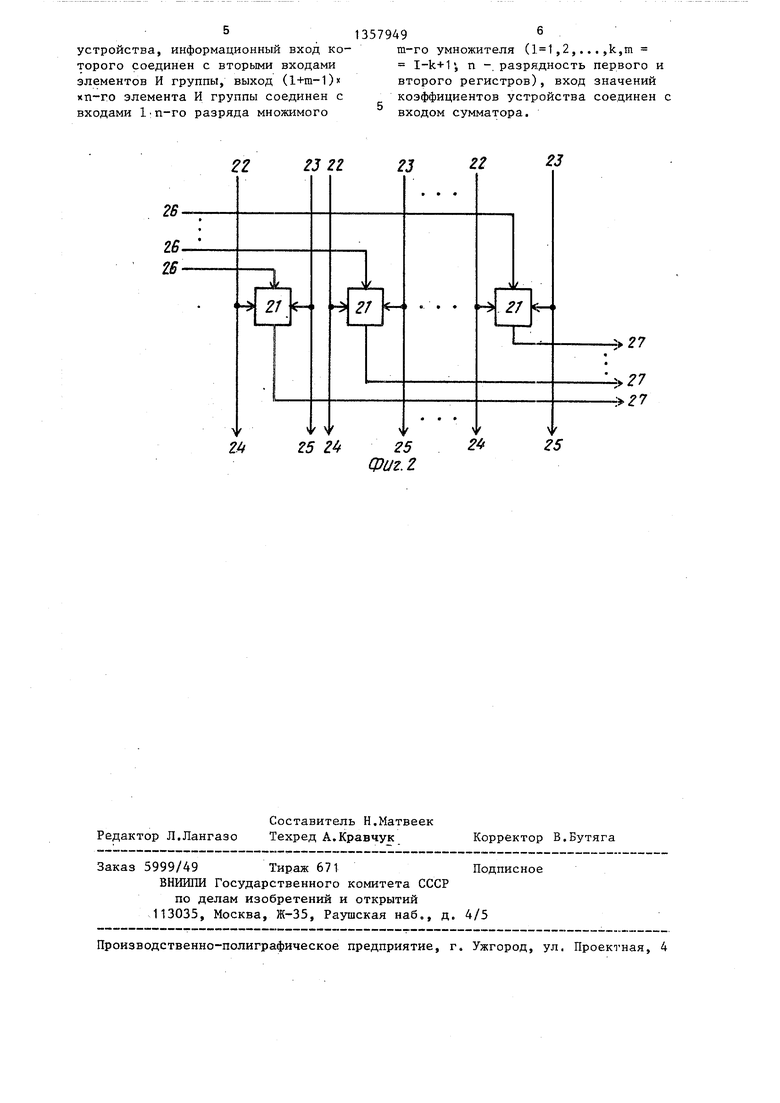

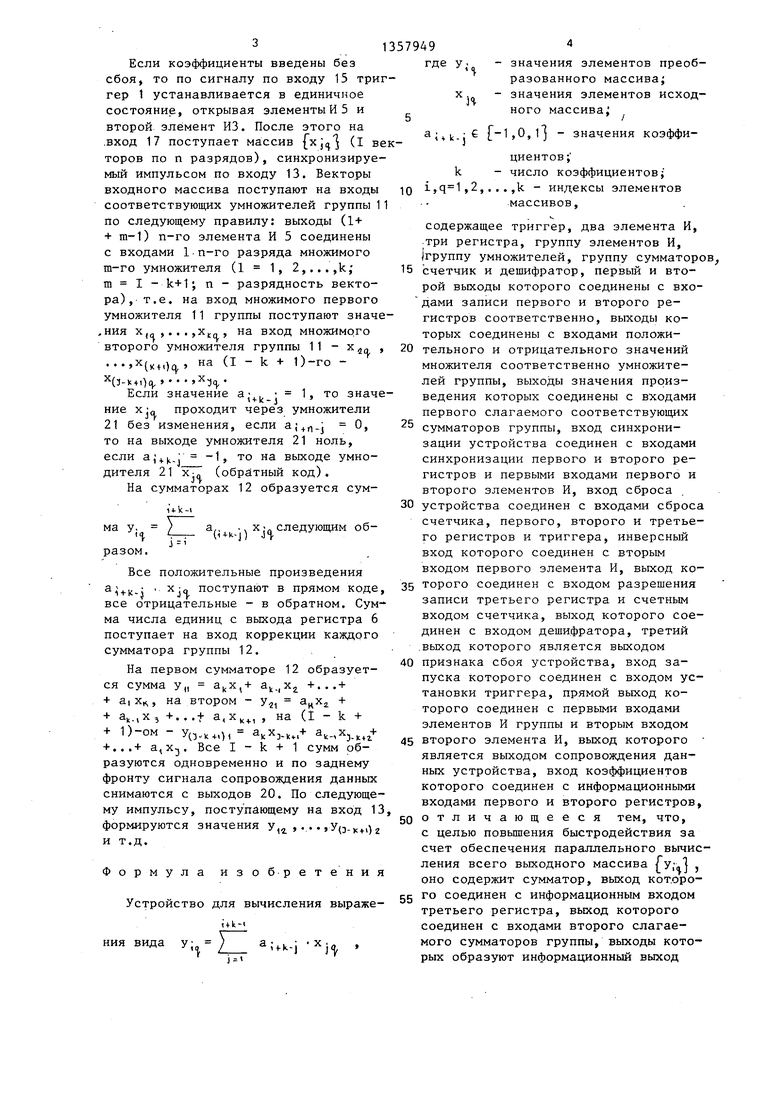

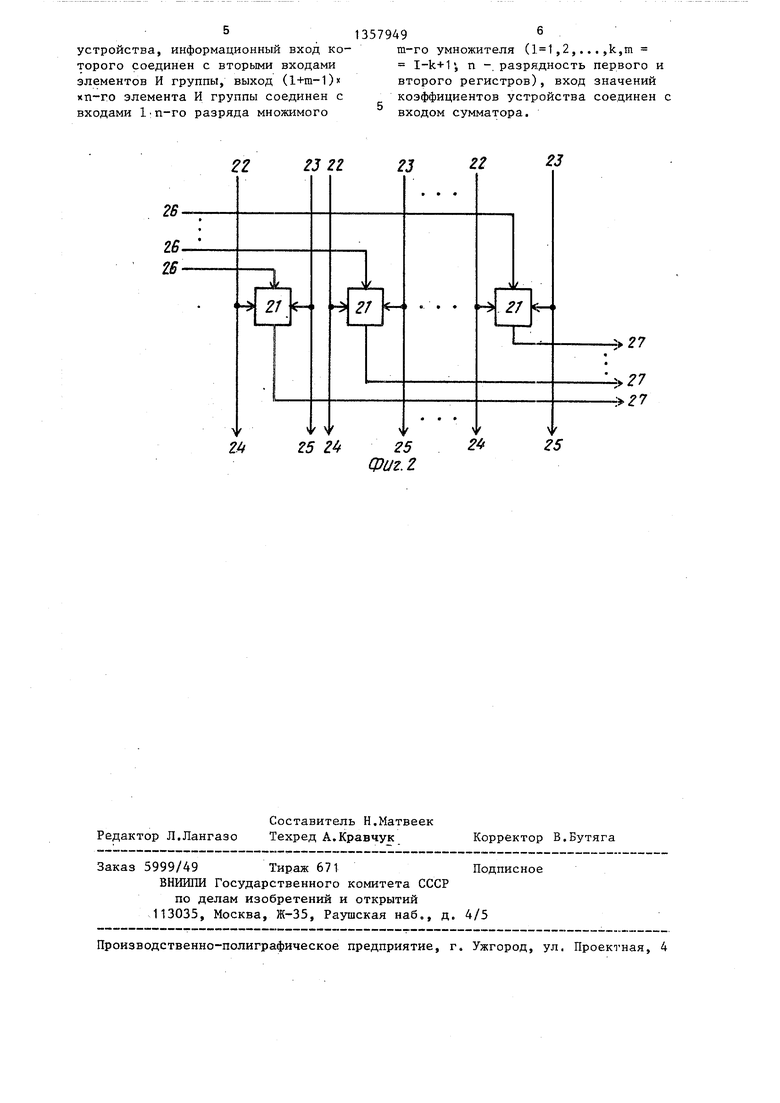

На фиг. 1 представлена функциональная -схема устройства; на фиг.2 - вариант выполнения умножителя группы

Устройство содержит триггер 1, элементы И 2 и 3, сумматор 4, группу элементов И 5, регистры 6-8, счетчик 9, дешифратор 10, группу умножителей 11 и группу сумматоров 12, входы 13-17 синхронизации, сброса, запуска, ввода коэффициентов и информацион- ный устройства соответственно, выходы 18-20 признака сбоя, сопровождения данных и информационный устройства соответственно. Умножители 21, входы 22 и 23 и выходы 24 и 25 положи- тельного и отрицательного значений множителя соответственно, входы 26 значения множимого и выходы значения произведения.

Устройство работает следующим об- разом.

Подачей сигнала на вход 14 производится установка устройства в исходное состояние. При этом сбрасываются триггер I, регистры 6-8 и счетчик 9.

Затем вводятся коэффициенты a-;..j. При этом на вход 13 поступает импульс по заднему фронту которого счетчик 9 устанавливается в состояние, равное

1,2,...k - индексы элементов массивов. С этой целью устройство, содержащее триггер 1, элементы И 2, 3, группу элементов И 5, регистры 6-8, счетчик 9, дешифратор 10, группу умножителей 11 и группу сумматоров 12, содержит сумматор 4. Введение сумматора 4 и изменение связей в устройстве позволяет вычислять выходной массив fy. ol за один такт работы устройства, 2 ил.

единице. В результате на первом входе дешифратора 10 появляется сигнал, поступающий на вход разрешения записи регистра 7.

В следующем такте по переднему фронту импульса, поступающего на вхо 13, осуществляется запись в регистр

7положительных значений коэффициентов, а по заднему фронту этого импульса счетчик 9 устанавливается в состояние, равное двум, В результате по сигналу с второго выхода дешифратора 10 разрешается запись в регистр

8отрицательных значений коэф(1)ициен- тов, которые поступают в следующем такте на вход 16, синхронизируемых по переднему фронту импульса на входе 13. По заднему фронту этого импульса счетчик 9 устанавливается в состояние, равное трем. Одновременно вектор отрицательных значений коэффициентов а;. поступает на сумматор 12, который осуществляет подсчет числа единиц, содержащихся в векторе отрицательных значений. Вычисленное значение с выхода сумматора 12 заносится в регистр 6 по импульсу на входе 13,

Эта сумма используется для коррекции результата вычисления.

Если на этапе ввода на вход 16 поступают еще какие-либо данные, сопровождающиеся импульсом, то ло заднему фронту импульса по входу 13 счетчик 9 устанавливается в состояние, равное четырем, в результате чего на третьем вых;оде дешифратора 1 появляется признак сбоя устройства.

Если коэффициенты введены без сбоя, то по сигналу по входу 15 триггер 1 устанавливается в единичное состояние, открывая элементы И 5 и второй элемент ИЗ. После этого на вход 17 поступает массив fxj, (I векторов по п разрядов), синхронизируемый импульсом по входу 13. Векторы входного массива поступают на входы ю соответствующих умножителей группы 11 по следующему правилу: выходы (1+ + т-1) п-го элемента И 5 соединены с входами 1.п-го разряда множимого -го умножителя (1 1, 2,...,k, I - k+l; n - разрядность вектора), т.е. на вход множимого первого множителя 11 группы поступают значе- ния X,„,...,, на вход множимо.го

((

второго умножителя группы 11-х ...,Х(,ц, на (I - k + 1)-го (r-K4l)c(, ),

Если значение а

щ

ние X

П

1, то значе- проходит через умножители

21 без изменения, если а

1

О,

25

то на выходе умножителя 21 ноль,

15

20

если а

то на выходе умнодителя 21 Х-. (обратный код).

На сумматорах 12 образуется сумn-k-i

ма

разом.

Все а

J

а,.. xj следующим обположительные произведения 1 ;q поступают в прямом коде, все отрицательные - в обратном. Сумма числа единиц с выхода регистра 6 поступает на вход коррекции каждого сумматора группы 12.

На первом сумматоре 12 образуется сумма у„ акХ,+ а.,х +...+ + aix, на втором - у, ацХ + + а.,х, +...+ а.х. , на (1 - k +

+ 1)-ом - ,..,), a,Xi.v.,+ а,..х, . +

D-kn + 1

об 1С-1

+ ...+ a,x-j. Все I - k + 1 сумм разуются одновременно и по заднему фронту сигнала сопровождения данных снимаются с выходов 20. По следующему импульсу, поступающему на вход 13 формируются значения У, , .Уо-к+Ог и т.д.

Формула изобретения

Устройство для вычисления выраже- itk-i

ния вида У;(, а;,,,.; -х

j

I f k-j

J4

ю

7949

где у,

- значения элементов преобразованного массива; X. - значения элементов исходного массива;

i + k-i значения коэффициентов ; k - число коэффициентов;

i,,2,,..,k - индексы элементов массивов,

ригвекуеыды ю ы 11 ы о огоаче- о

аче- и

,

25

омбде, ум6го

т+

г х е13, Ог

я

е-

55

содержащее триггер, два элемента И, три регистра, группу элементов И, jrpynny умножителей, группу сумматоров

15 счетчик и дешифратор, первый и второй выходы которого соединены с входами записи первого и второго регистров соответственно, выходы которых соединены с входами положи20 тельного и отрицательного значений множителя соответственно умножителей группы, выходы значения произведения которых соединены с входами первого слагаемого соответствующих сумматоров группы, вход синхронизации устройства соединен с входами синхронизации первого и второго регистров и первыми входами первого и второго элементов И, вход сброса

30 устройства соединен с входами сброса счетчика, первого, второго и третьего регистров и триггера, инверсный вход которого соединен с вторым входом первого элемента И, выход ко35 торого соединен с входом разрешения записи третьего регистра и счетнь м входом счетчика, выход которого соединен с входом дешифратора, третий .выход которого является выходом

40 признака сбоя устройства, вход запуска которого соединен с входом установки триггера, прямой выход которого соединен с первыми входами элементов И группы и вторым входом

45 второго элемента И, выход которого является выходом сопровождения данных устройства, вход коэффициентов которого соединен с информационными входами первого и второго регистров,

50 отличающееся тем, что, с целью повышения быстродействия за счет обеспечения параллельного вычисления всего выходного массива fУ;,, ,

оно содержит сумматор, выход которого соединен с информационным входом третьего регистра, выход которого соединен с входами второго слагаемого сумматоров группы, выходы которых образуют информационный выход

устройства, информационный вход которого соединен с вторыми входами элементов И группы, выход (l+m-l)x хп-го элемента И группы соединен с входами 1п-го разряда множимого

23 22

Редактор Л.Лангазо

Составитель Н.Матвеек Техред А.Кравчук

Заказ 5999/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1357949

т-го умножителя (,2,...,k,m I-k+1 j n -.разрядность первого и второго регистров), вход значений коэффициентов устройства соединен с входом сумматора.

22

23

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Вычислительное устройство | 1987 |

|

SU1444759A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| Вычислительное устройство | 1985 |

|

SU1320804A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Цифровой Т-генератор функций комплексного переменного | 1987 |

|

SU1483445A1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации в реальном масштабе времени. Цель изобретения - повышение быстродействия за счет 00 ел о со фиг J

Авторы

Даты

1987-12-07—Публикация

1985-12-04—Подача