1чЭ

ю

оо ю

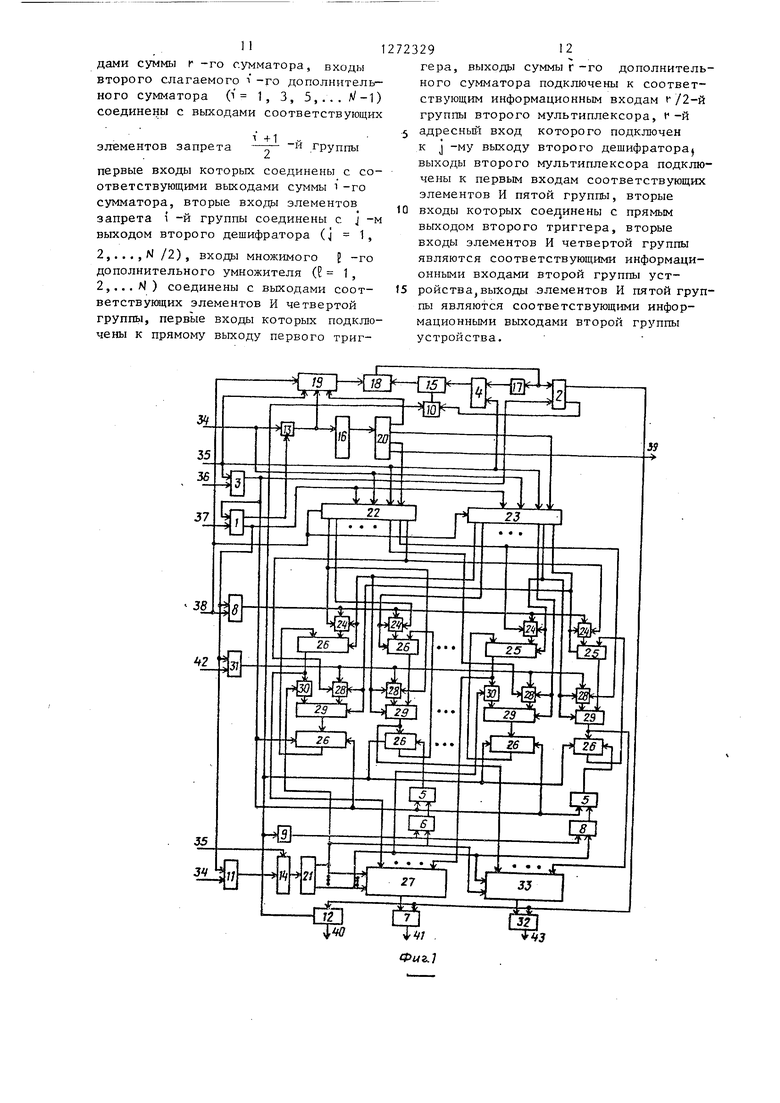

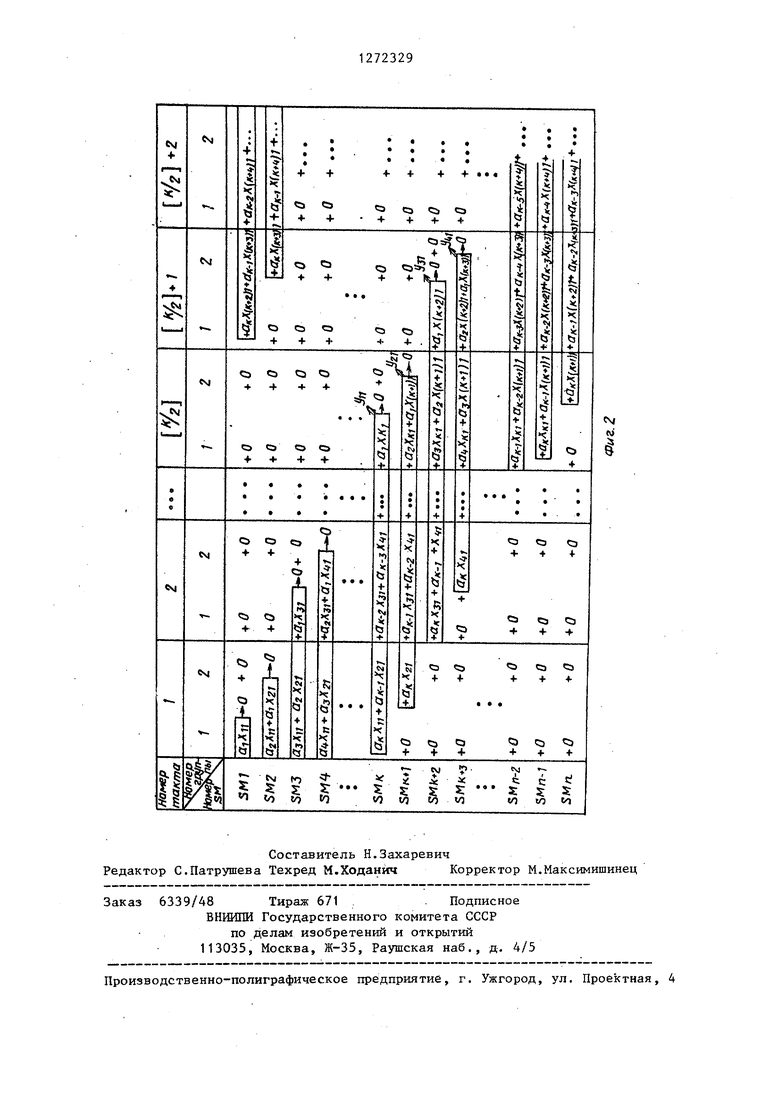

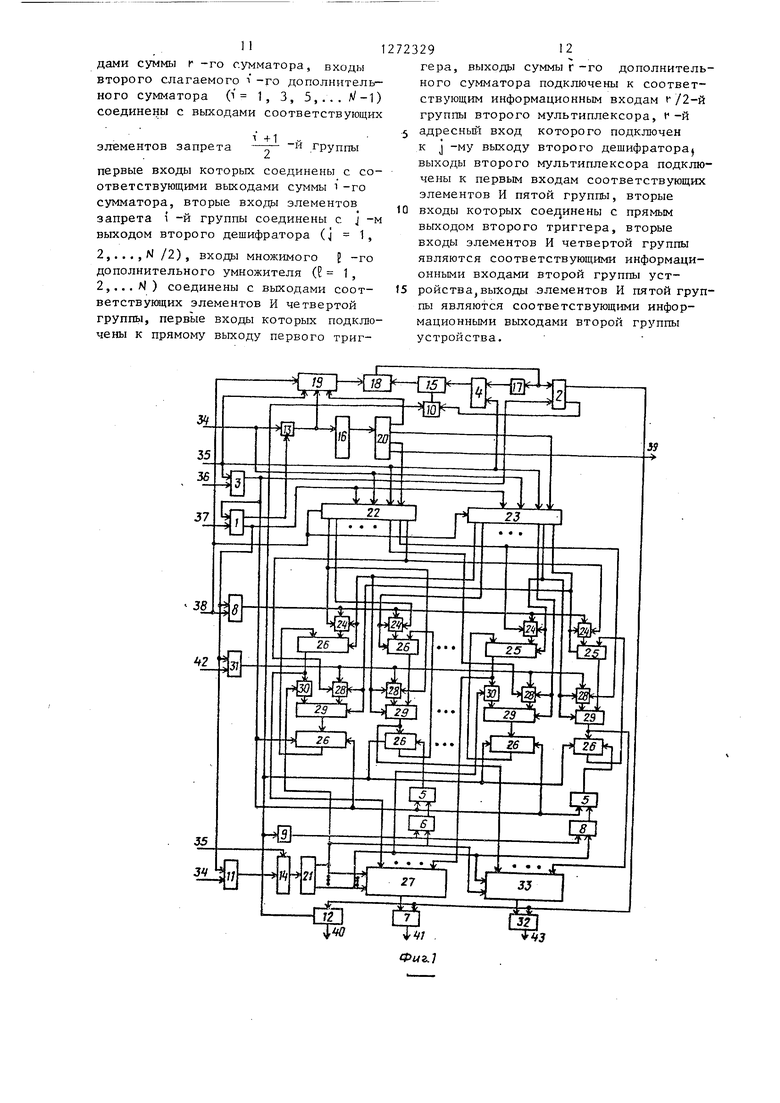

со Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации. Цель изобретения - повышение быстродействия за счет обеспечения возможности двухканальной обработки данных, На фиг. 1 представлена структур ная схема вычислительного устройства; на фиГ. 2 - таблица содержания сумматоров. Устройство содержит первый 1 три гер, второй 2 триггер,, дервый элемент ИЛИ 3, второй элемент ШШ 4, группу элементов ИЛИ 5, первую груп пу элементов И 6, вторую группу эле ментов И 7, третью группу элементов И 8, элемент НЕ 9, первый, второй трет№1-и четвертый элементы И 10 13, первый, второй и третий счетчики 14 - 16, элемент 17 задержки, схему 18 сравнения, регистр 19 числа коэффициентов, первый и второй дешифраторы 20 и 21, первый и второ регистры коэффициента 22 и 23, л/ умножителей 24, л/ сумматоров 25, регистров 26 результата, мультиплек рор 27, V дополнительных умножителей 28, У дополнительных сумматоро 29, элементы 30 запрета, четвертую и пятую группы 31 и 32 элементов И и второй мультиплексор 33. Устройство имеет вход 34 сопрово дения данных, вход 35 сброса, вход 36 признака конца массива,вход 37 пуска, информационные входы 38 первой группы, выход 39 сбоя, выход 40 сопровождения данных, информационные выходы 41 первой группы, информационные входы 42 второй группы, информационные вьпсоды 43 второй группы. Устройство работает следующим образом. Перед началом работы подачей сигналов на вход сброса 35 устройства производится установка устройства в исходное состояние. При этом с входа 35 устройства устанавливает в нулевое состояние регистры 19, 22, 23, счетчики 14, 16, а пройдя через элемент ИЛИ 3 установит в нулевое состояние триггеры 1 и 2 и i -ые регистры 26 результата (т 1, 3, 5,...). Кроме того, пройдя через 55

элементы ИЛИ 5 группы, сигнал сброса установит в нулевое состояние ые регистры 26 результатов ( г 2, 4, 50

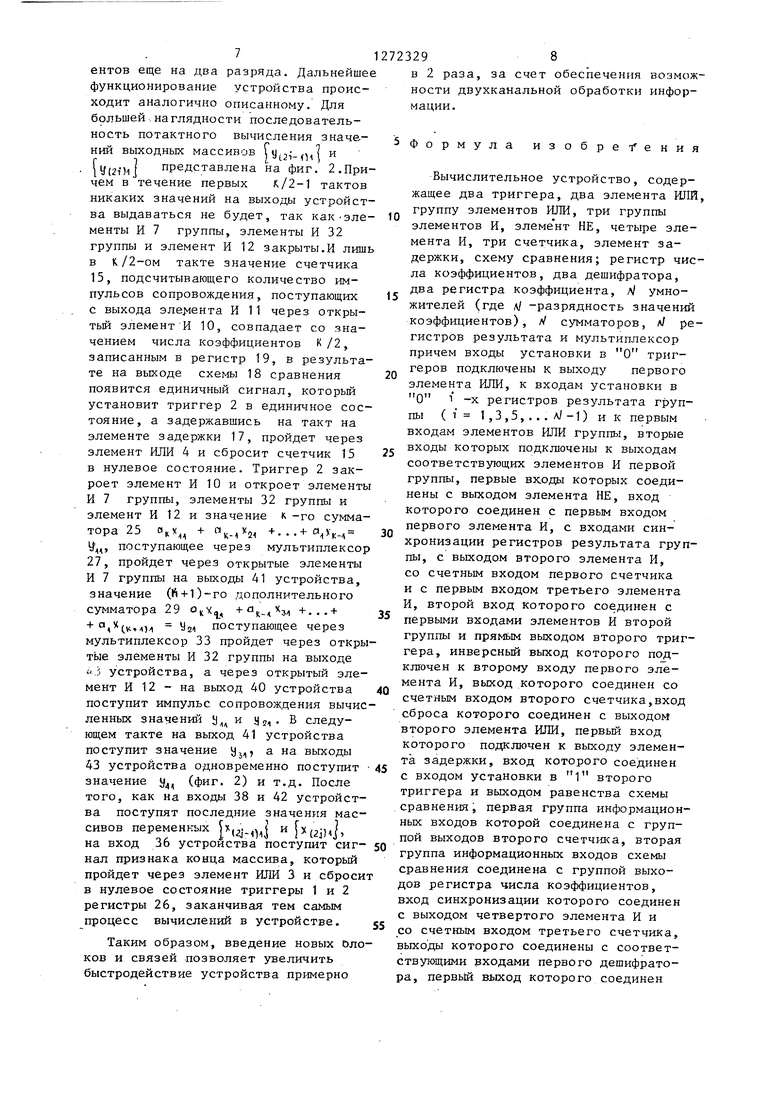

единичньш сигнал, который поступит на вход разрешения записи регистра 23. В следующем такте на входы 38 6,... Л/ ) . Пройдя через второй элемент ИЛИ 4, сигнал сброса установит в нулевое состояние второй счетчик 15. Затем производится ввОд начальных данных.При этом на вход 34 устройства поступает импульс, который проходит через открытый элемент И 13 (триггер 1 установлен в нулевое состояние) на счетный вход счетчика 16 и по -заднему фронту устанавливает этот счетчик в состояние, равное единице. В результате на первом выходе дешифратора 20 появится единичньм сигнал, который поступит на вход разрешения записи регистра 19. В следующем такте на информационные входы 38 устройства подается параллельным кодом значение половины числа коэффициентов а,- + ц.. , (j i , +1,... 1+К-1), равное К /2, где К/2 наименьшее целое, большее или равное К /2, и одновременно на вход 34 подается импульс, который проходит через открытый элемент И 13 на вход синхронизации регистра 19 и осуществляет запись в этот регистр значения числа коэффициентов К/2, поступающего с входов 38 устройства на информационные входы этого регистра, а по заднему фронту этого импульса счетчик 16 установится в состояние, равное двум. В результате, на втором выходе дешифратора 20 появится единичный сигнал, который поступит ;на вход разрешения записи регистра 22. В следующем такте на входы 38 устройства поступят положительные значения коэффициентов di+K-i (коэффициенты а представляются в тернарной,системе кодирования, т.е. принимают значения +1, Oj -1, поэтому и различают положительные значения коэффициентов, когда а,-.- +1, и отрицательные значения, когда -1).Сопровождающий эти данные импульс, подающийся на вход 34 устройства, поступит на вход синхронизации регистра 22 и осуществит запись в этот регистр положительных значений коэффициентов .-, а по заднему фронту этого импульса счетчик 16 установится в состояние, равное трем. В результате, на третьем выходе дешифратора 20 появится устройства поступает отрицательное значение коэффициентов .; , а сопровождающий эти значения импульс подающийся на вход 34, поступит на вход синхронизации регистра 23, и осуществит запись в этот регистр отрицательных значений коэффициенто J а по. заднему фронту этого импульса счетчик 16 установится в состояние, равное четырем. Если же на этапе ввода на входы 38 устройст ва поступят еще какие-либо данные, сопровождаемые импульсом сопровождения, тот этот импульс сопровождения пройдет с входа 34 на счетный вход счетчика 16 и перебросит его по заднему фронту в следующее состояние, равное пяти. В результате на четвертом выходе дешифратора 20 появится единичньй сигнал, который поступит на выход 39 устройства как сигнал сбоя устройства при вводе и процесс ввода начальных дан ньсх осуществляется заново. Если же начальные данные будут введены без сбоя, то после их ввода начинается процесс решения, осуществляемьй следующим образом. На вход 37 устройства подается сигнал Пуск,который поступает на прямой вход триггера 1 и перебрасывает его в единичное состояние.В результате на инверсном выходе этого триггера появится нулевой сигнал который закроет элемент И 13, завер шая тем самым процесс ввода начальных данных в устройство, а на прямом выходе триггера 1 появится единичный сигнал, который откроет эле1 л-нты И 8 третьей группы, элементы И 31 четвертой группы, элемент И 11 и поступит на входы разрешения сдви га регистров 22 и 23. Каждый AJ -разрядный регистр, коэф фициента 22 и 23 представляет собой кольцевой регистр сдвига, причем вы ход К-го разряда каждого регистра 22 и 23 соединен с входом (Р+2)-го разряда соответственно своего регис ра 22 и 23 ( 6 1 , 2,. . . , л1 -2) , выход (-1)-го разряда каждого регист ра 22 и 23 соединен с входом первог разряда соответственно своего регис ра 22 и 23, выход А| -го разряда каждого регистра 22 и 23 значений коэффициентов соединен с входом вто рого разряда соответственно своего регистра 22 и 23.После этого на ин3294формационные входы 38 и 42 устройства начинают поступать параллельно два массива данных ( l cajNij где J 1,2,...,С7 , сопровождаемых импульсами сопровождения, поступающими на вход 34 устройства. В первом такте на входы 38 поступит параллельным кодом значение первой величины (i, массива (jj-Oiii на входы 42 - значение первой величины v i массива х (2i)A I Значение х, пройдет парраллельным кодом через открытые элементы ,И 8 группы на входы множимого всех блоков 24, на входы множителя которых поступает значение коэффициентов д. 1(, из регистров 22 и 23. Таким образом, в первом такте при поступлении значения первой вел1гчины х массива Ix gj-nil вход)1 умножителей 24 произойдет умножение этого значения на коэффициенты п. и произведения if, а. поступят на входы Е-ых сумматоров 25, а так как на вторую группу входов этих сумматоров 25 с выходов регистров 26 результатов группы поступают нулевые значения. Так как регистры 26 предварительно были сброшены в нулевое состояние, то произведения Х„Од пройдут через сумматоры 25 без изменения (за исклзочением случая, когда с(р 1 и в сумматоре к обратному коду произведения ,,0{ добавится в младший разряд единица, переводящая это произведение в дополнительный код). Одновременно аналогичным образом посредством f -го дополнительного умножителя 28 и I -го дополнительного сумматора 29 образуется произведение Х Of., (8 2,3.. . , л/ ), причем, если К А/ , то л/-ые разряды регистров 22 и 23 являются нулевыми |и на выходе первого дополнительного умножителя 28 появится нулевой результат. Если К V, то результат на выходе блока 28 в общем случае ненулевой и является первым слагаемым очередного значения функции У . Для разделения слагаемых и относящихся к разным значеним функции У,- , служит группа элеентов 30 запрета, представляющих обой двухвходоБые элементы И, у коорых вторые входы, соединенные с оответствующими выходами второго ешифратора 21, являются инверсными на первые входы элементов 30 за05 1 рета поступают соответствующие разряды слагаемых из сумматора 25-. В первом такте импульс сопровождения с выхода элемента И 11 поступит на счетньй вход счетчика 14 и по переднему фронту перебросит его в состояние, равное единице,в результате чего на первом выходе дешифратора 21 появится единичньй сигнал, закрывающий инверсные входы первой группы элементов запрета 30, т.е. данные с выхода первого сумматора 25 первой группы не поступят на вход первого дополнительного сумматора 29 и в первый регистр 26 запишется значение 0|с 24 (при К л/) или нуль (приКАл) так как на вход синхронизации регистров 26 через открытый элемент И 11 поступит импульс сопровождения значе НИИ и Х . Во все остальные I ые регистры 26 (6 2,3,..., л/) посту пят суммы Oj Х, + сформирован ные на -ых дополнительных сумматорах 29. Кроме того, единичный сигнал с первого выхода дешифратора 21 обес печит подключение к выходам первого мультиплексора 27 и второго мультиплексора 33, соответственно, сумм . Одновременно этот единичный сигнал с выхода дешиф ратора 21 поступит на вход первого элемента И 6 первой группы, а по : окончании импульса сопровождения данных на выходе элемента НЕ 9 появится единичный сигнал, который прой дет через открытый первый элемент И 6 группы, через первый элемент ИЛИ 5 группы на вход сброса второго регистра 26 группы и установит его в нулевое состояние. Кроме того, импульс сопровождения значения м V ai пройдет с входа 34 на входы синхронизации регистров 22 и 23 и так как на вход разрешения сдвига этих регистров поступает разрешающий сигнал с выхода триггера 1, то по заднему фронту импульса сопровождения в этих регистрах 22 и 23 произойдет сдвиг на два разряда значений коэффициентов, причем значение последнего л/ -го разряда перезаписывается во второй разряд своего регистра, а предпоследнего, (V-l)-ro разряда - в первый разряд своего регистра, т.е. если п л/ то во втором разряде каждого регистра 22 и 23 появится нуль, если к Л/, то во втором разряде каждого регистра 29б появится соответствующее значение К-го коэффициента fl,. Следовательно, в следующем такте на входы множителя первого блока 24 будет поступать значение коэффициента ci на входы второго блока 24 - значение а на входы третьего блока 24 - а и т.д. и поступившее второе значение х массива данных 1. (j.oJ умножится на соответствующий коэффициент dp и поступив на входы сумматора 25, новое произведение х,, «(. просуммируется с предыдущей суммой V,ag + + поступит на входы Р-ых дополнительных сумматоров 29 непосредственно (для S 2, 4, 6,...V) или через элементы 30 запрета (для Р 1, 3,5, . . . , А/-1) . Импульс сопровождения данных, поступив на вход счетчика 14, установит его в состояние, равное двум, и на втором выходе дешифратора появится единичньш сигнал, который закроет элементы 30 запрета второй группы. Следоватедьно, данные с выхода третьего сумматора 25 не пройдут на входы третьего дополнительного сумматора 29. Получившееся значение + выхода третьего сумматора 25 поступает на вторую группу информационных входов первого мультиплексора 27 и пройдет на выход этого мультиплексора 27, так как на втором управляющем входе мультиплексора - единичный сигнал. В остальных каскадах суммирования Р -ые группы элементов запрета ( 1,3, 4, ... л/ /2) будут открыты и сумма „, с + + мОе-г поступив иа входы дополнительного сумматора 29, просуммируется со слагаемым запишет в t-ые регистры 26, причем с выхода четвертого дополнительного сумматора 29 сумма + + )л°2 . поступит на вторую группу информационных входов второго мультиплексора 33 и далее - на его выход, так как на втором управляющем входе этого мультиплексора 33 - единичный сигнал.Кроме того, единичный сигнал со второго выхода деши.фратора 21 откроет второй элемент И 6 первой группы и по окончании импульса сопровождения обеспечит установку в нулевое состояние четвертого регистра 26 результата (фиг. 2), а в регистрах 22 и 23 произойдет сдвиг значений коэффициентов еще на два разряда. Дальнейше функционирование устройства происходит аналогично описанному. Для большей.наглядности последовательность потактного вычисления значений выходных массивов lyLji-fli 1(27)1 представлена на фиг. 2.При чем в течение первых тактов никаких значений на выходы устройст ва выдаваться не будет, так как-эле менты И 7 группы, элементы И 32 группы и элемент И 12 закрыты.И лиш в К/2-ом такте значение счетчика 15, подсчитывающего количество импульсов сопровождения, поступающих с выхода эле 1ента И 11 через открытьм элемент И 10, совпадает со значением числа коэффициентов К/2, записанным в регистр 19, в результа те на вькоде схемы 18 сравнения появится единичный сигнал, которьй установит триггер 2 в единичное сос тояние, а задержавшись на такт на элементе задержки 17, пройдет через элемент ИЛИ 4 и сбросит счетчик 15 в нулевое состояние. Триггер 2 закроет элемент И 10 и откроет элементы И 7 группы, элементы 32 группы и элемент И 12 и значение к -го сумматора 25 + ,.,Х2 +...+ . tf, поступающее через мультиплексор 27, пройдет через открытые элементы И 7 группы на выходы 41 устройства, значение (Й+1)-го дополнительного сумматора 29 , + );., +...+ + )i УЙЧ поступающее через мультиплексор 33 пройдет через откры тые элементы И 32 группы на выходе i-.j устройства, а через открытый элемент И 12 - на выход 40 устройства поступит импульс сопровождения вычис ленных значений У и у ji В следующем такте на выход 41 устройства поступит значение j,, а на выходы 43 устройства одновременно поступит значение у,, (фиг. 2) и т.д. После того, как на входы 38 и 42 устройства поступят последние значения массивов переменных .,;, и x(2j)i, на вход 36 устройства поступит сигнал признака конца массива, который пройдет через элемент ИЛИ 3 и сброси в нулевое состояние триггеры 1 и 2 регистры 26, заканчивая тем самым процесс вычислений в устройстве. Таким образом, введение новых оло ков и связей позволяет увеличить быстродействие устройства примерно в 2 раза, за счет обеспечения возможности двухканальной обработки информации. Формула изобретения Вычислительное устройство, содержащее два триггера, два элемента ИЛИ, группу элементов ИЛИ, три группы элементов И, элемент НЕ, четыре элемента И, три счетчика, элемент задержки, схему сравнения; регистр числа коэффициентов, два дешифратора, два регистра коэффициента, л/ умножителей (где л/ -разрядность значений коэффициентов), // сумматоров, л/ регистров результата и мультиплексор причем входы установки в О триггеров подключены к выходу первого элемента ИЛИ, к входам установки в О 1 -X регистров результата группы ( 1 1,3 ,5, . . . л/ -1) и к первым входам элементов ИЛИ группы, вторые входы которых подключены к выходам соответствующих элементов И первой группы, первые вкоды которых соединены с выходом элемента НЕ, вход которого соединен с первым входом первого элемента И, с входами синхронизации регистров результата группы, с выходом второго элемента И, со счетным входом первого счетчика и с первым входом третьего элемента И, второй вход которого соединен с первыми входами элементов И второй группы и прямым выходом второго триггера, инверсный выход которого подключен к второму входу первого элемента И, выход которого соединен со счетным входом второго счетчика,вход сброса которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к вьгходу элемента задержки, вход которого соединен с входом установки в 1 второго триггера и выходом равенства схемы сравнения, первая группа информационных входов которой соединена с группой выходов второго счетчика, вторая группа информационных входов схемы сравнения соединена с группой выхоов регистра числа коэффициентов, ход синхронизации которого соединен с выходом четвертого элемента И и со счетным входом третьего счетчика, ыходы которого соединены с соответтвующими входами первого дешифратоа, первьШ выход которого соединен с входом разрешения записи регистра числа коэффициентов, второй выход первого дешифратора подключен к входу разрешения записи первого регистра коэффициента, третий выход первого дешифратора соединен с входом разрешения записи второго регистра коэффициента, вход разрешения сдвига которого соединен с прямым выходом первого триггера, с первыми входамиэлементов И третьей группы, с первым входом второго элемента Икс входом |разрешения сдвига первого регистра коэффициента, выход К-го разряда которого (К 1, 2,...N/ ) соединен с входом положительного значения разряда множителя К -го умножителя вход отрицательного значения разряда множителя которого подключен к выходу- к -го разряда второго регист ра коэффициента и к входу переноса в младрзий разряд К -го сумматора, входы первого слага.емого которого подключены к соответствующим вьсюдам К-го умножителя, входы множимого которого соединены с выходами соответствующих элементов И третьей группы, входы второго слагаемого К -го сумматора соединены с соответствующими выходами разрядов К -го регистра результата группы выходы сугты К -го и ( 1,3, 5, , . . ,/V -1) соесумматорадинены с соответствующими информаIS+1 „ ционными входами --г- -и группы мультиплексора, выходы которого подключены к вторым входам соответствующих элементов И второй группы, выходы первого счетчика подключены к соответствующим входам второго дешифратора, -и вьгход которого (, 2,... А//2) подключен к -му адресному входу мультиплексора и к второму входу J-го элемента И первой группы, первьй вход четвертого элемента И подключен к инверсному выходу первого триггера, вход уста новки в О г -го ре.гистра результата группы (г 2, 4, 6,...) соединен с выходом г /2-го элемента ШШ группы,вход сопровождения данных устройства подклзочен к второму входу четвертого элемента И, к входам синхронизации первого и второго регистров коэффициента и к второму входу второго элемента И, вход сброса устройства подключен к входам сброса первого и третьего счетчиков, к вхо129 дам установки в О, регистра числа коэффициентов, первого и второго регистров коэффициента, к второму входу второго элемента ИЛИ и к первому входу первого элемента 1ШИ,вход признака конца массива устройства соединен с вторым входом первого элемента ИЛИ, вход пуска, устройства соединен с входом установки в 1 первого триггера, информационные входы- первой группы устройства подключены к входам соответствующих разрядов регистра числа коэффициентов, регистров коэффициента, к вторым входам соответствующих элементов И третьей грулпы, четвертьш выход первого дешифратора подключен к вЬкоду |сбоя устройства, выход третьего элемента И соединен с выходом сопровожг д.,„„,, устройства,выходы р, являются соответствующими информационными выходами первой группы устройства, отличающее ся тем, что, с целью повышения быстродействия устройства за счет обеспечения двухканальной обработки информации оно содержит Л дополнительных умножителей, л/ дополнительных сумматоров 1/2 групп элементов запрета, четвер , элементов И и второй мультиплексор, причем выходы В -го разряда (, 2,...,А/-1) первого и второго регистров коэффициента подключены соответственно к входам положительного и отрицательного значений разряда множителя (Е+1)-го дополнительного умножителя, выходы А -го разряда первого и второго регистров коэффициента соединены соответственно с входами положительного и отрицательного значений множителя первого дополнительного умножителя, выходы Р-го дополнительного умножителя (, 2,...) подключены к соответствующим входам первого слагаемого -го дополнительного сумматора, вход переноса в младший разряд которого соединен с входом отрицательного значения разряда множителя t-ro дополнительного умножителя, выходы В-го дополнительного сумматора пoдKJшчeны к соответствующим информационным входам 1-го регистра результата группы, входы второго слагаемого г-го дополнительного сумматора (г 2, 4, 6,... А/) соединены с соответствую1цими выхо1 1

дами суммы г -го сумматора, входы второго слагаемого -го дополнительного сумматора 0 1, 3, 5,.. . А/-1) соединены с выходами соответствующих

+ 1

и .группы

элементов запрета

первые входы которых соединены с соответствующими выходами суммы 1 -го сумматора, вторые входы элементов запрета i -и группы соединены с j -м выходом второго дешифратора (j 1,

2,...,М /2), входы множимого 5 -го дополнительного умножителя (Е 1, 2,.., N ) соединены с выходами соответствующих элементов И четвертой группь, первые входы которых подключены к прямому выходу первого триг3

7232912

гера, выходы суммы г-го дополнительного сумматора подключены к соответствующим информационным входам f/2-й группы второго мультиплексора,

-5 адресный вход которого подключен к J -му выходу второго дешифратора выходы второго мультиплексора подключены к первым входам соответствующих элементов И пятой группы, вторые

10 входы которых сое; инены с прямым выходом второго триггера, вторые входы элементов И четвертой группы являются соответствующими информационными входами второй группы устt5 ройства выходы элементов И пятой группы являются соответствующими информационными выходами второй группы устройства.

ev)

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Вычислительное устройство | 1987 |

|

SU1444759A1 |

| Вычислительное устройство | 1985 |

|

SU1320804A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Устройство для вычисления выражения @ | 1985 |

|

SU1357949A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и функциональных преобразователях. Целью изобретения является повышение быстродействия устройства путем обеспечения двухканальной обработки информации. С этой целью устройство содержит дополнительные сумматоры и умножители, образующие совместно с четвертой и пятой группами элементов И и вторым мультиплексором второй канал обработки. Вычисление значения результирующего полинома выполняется по двум каналам обработки со сдвигом на такт, в совмещенном режиме,2 ил.

| Устройство для вычисления выражений вида | 1973 |

|

SU444193A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-23—Публикация

1985-04-02—Подача