11

Изобретение относится к вычислительной технике и может быть использовано для интерпретации экспериментальных зависимостей, в частности дл решения задач технической диагностики, задач коррекции динамических характеристик измерительных и управляющих систем.

Целью изобретения является повыше ние быстродействия устройства.

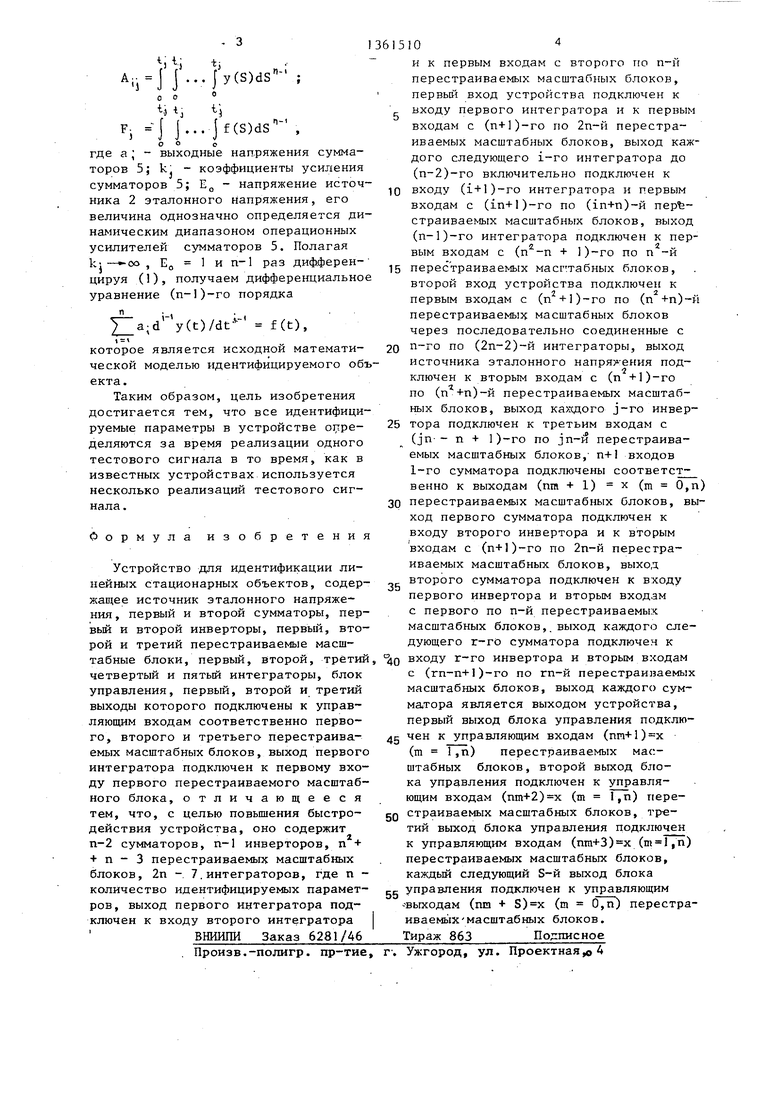

На чертеже приведена структурная схема устройства.

Устройство состоит из 2п-2 интеграторов 1(1), 1(2), ..., 1(2п-2). источника 2 эталонного напряжения, п+1 инверторов 3(1), 3(2), ..., 3(п+1), п + п перестраиваемых масштабных блоков 4(1), 4(2), ..., 4( п), п сумматоров 5 ( 1), 5(2), .., 5(п) и блока 6 управления, где п - количество идентифицируемых параметров. Здесь и везде в дальнейшем цифрами в скобках, следующими за номером позиции (цифрой не в скобках) показаны порядковые номера совершенн одинаковых по своему техническому исполнению соответственно блоков,узлов, элементов, а просто цифрами в скобках, стоящими около контура бло- ка, узла, элемента - порядковые номера его входов и выходов. Выход первого интегратора 1(1) подключен к входу второго интегратора 1(2) и к первым входам с 4(1)-го по 4(п)-й перестраиваемых масштабных блоков, первый вход устройства (вход тесто- . вого сигнала y(t)) подключен к вхо- ду первого интегратора 1(1) и к первым входам с 4(п+1)-го по 4(2п)-й перестраиваемых масштабных блоков, выход каждого следуюш;его 1 (i)-ro интегратора до I (п-2)-го включительно подключен, к входу i(i + l)-ro интегратора и первым входам с 4 (in-f-l )- Го по 4(1п+п)-й перестраиваемых масштаб 1ых блоков, выход 1(п-1)-го интегратора подключен к первым входам с 4(п -п+1)-го по 4(п)-й перестраиваемых масштабных блоков, второй вход , устройства (вход реакции объекта f(t) подключен к первым входам с 4(п +1)-го по 4(п +п)-й перестраиваемых масштабных блоков через последовательно соединенные с 1(п)-го по 1 (2п-2)-й интеграторы, выход источника 2 эталонного напряжения подключен к вторым входам с 4()-го по 4 (п +n)-j перестраиваемых масштабных

102

блоков, выход каждого 3(j)-ro инвертора (J О, п-ь 1) подключен к третьим входам с 4(jn - п +1)-го по 4(п)-й перестраиваемых масштабных блоков, п+1 входов каждого 1-го сумматора (1 1,п) подключены соответственно к выходам 4(пт + 1) х(т 0,п) перестраиваемых масштабных блоков, выход первого сумматора 5(1) подключен к входу второго инвертора 3(2) и к вторым входам с 4(п+1)-го по 4(2п)-й перестраиваемых масштабных блоков, выход второго сумматора 5(2) подключен к входу первого инвертора и вторым входам с первого 4(1) по 4(п)-й перестраиваемых масштабных блоков, выход каждогс1 следующего г-го сумматора (г 3,п) подключен к входу г-го инвертора и вто рым входам с 4(гп - п+1)-го по 4(гп)-й перестраиваемых масштабных блоков, выход каждого сумматора является выходом устройства, каждый

S-й выход блока управления (S 1,п) подключен к управляющим входам (nm + + S) X (m О,и) перестраиваемых масштабных блоков.

Устройство работает следующим образом.

Импульс запуска Пуск поступает на соответствующий вход блока 6 управления, запускает тактовый генератор и формирователь тестового сигнала y(t). Блок управления распределяет тактовые импульсы на свои выходы в соответствии с их порядковым номером. Первый тактовый импульс поступает на первьй его выход, второй тактовый импульс - на второй его выход и т.д., последний тактовый импульс - на последний его выход. По окончании каждого S-ro тактового импульса (S 1,п) в соответствии с величиной и знаком напряжения на первых входах устанавливаются коэффициенты передачи с второго или третьего входа на выход (nm + S) x(m 0,n) перестраиваемых масштабных блоков. Длительность одного тактового импульса в п раз меньше длительности тестового сигнала y(t). По окончании последнег тактового импульса в соответствии с законами Кирхгоффа распределение потенциалов в устройстве определяется системой линейных алгебраических уранениип

- А;. .

.,/kj;

(1)

- 3

.1 1)

A;.J J...Jy(S)dS

n-1

0 0

i;

t

J J

J J... Jf(S)dS

о о о

n-1

где a; - выходные напряжения сумматоров 5; k - коэффициенты усиления сумматоров 5; Е - напряжение источника 2 эталонного напряжения, его величина однозначно определяется динамическим диапазоном операционных усилителей сумматоров 5. Полагая

k

-оо

ЕО

1 и п-1 раз дифференцируя (), получаем дифференциальное уравнение (п-1)-го порядка п

и

a;d

y(t)/df f(t),

которое является исходной математической моделью идентифицируемого объекта.

Таким образом, цель изобретения достигается тем, что все идентифицируемые параметры в устройстве оцре- деляются за время реализации одного тестового сигнала в то время, как в известных устройствах используется несколько реализаций тестового сигнала.

Оормула изобретения Устройство для идентификации линейных стационарных объектов, содер- 35 сумматора подключен к входу жап1ее источник эталонного напряже-- ния, первый и второй сумматоры, первый и второй инверторы, первый, второй и третий перестраиваемые масштабные блоки, первый, второй, третий, г-го инвертора и вторым входам

первого инвертора и вторым входам с первого по п-й перестраиваемых масштабных блоков,, выход каждого следующего г-го сумматора подключен к

четвертый и пятый интеграторы, блок управления, первый, второй и третий выходы которого подключены к управляющим входам соответственно первого, второго и третьего перестраиваемых масштабных блоков, выход первого интегратора подключен к первому входу первого перестраиваемого масштабного блока, отличающееся тем, что, с целью повьш ения быстродействия устройства, оно содержит п-2 сумматоров, п-1 инверторов, + п - 3 перестраиваемых масштабных блоков, 2п - 7.интеграторов, где п - количество идентифицируемых параметров, выход первого интегратора подключен к входу второго интегратора ВНИИПИ Заказ 6281/46

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная А

61510

и к первым входам с второго по п-й перестраиваемых масштабных блоков, первый вход устройства подключен к

входу первого интегратора и к первым входам с (п+1)-го по 2п-й перестраиваемых масштабных блоков, выход каждого следующего i-ro интегратора до (п-2)-го включительно подключен к

10 входу (i+l)-ro интегратора и первым входам с (in+l)-ro по (1п+п)-й nepfe- страиваемых масштабных блоков, выход (п-1)-го интегратора подключен к первым входам с ( + 1)-го по п -и

15 перестраиваемых масг табных блоков, второй вход устройства подключен к первым входам с ()-го по ()-й перестраиваемы масштабных блоков через последовательно соединенные с

20 по (2п-2)й интеграторы, выход источника эталонного напряжения подключен к вторым входам с (п +1)-го по (п +п)-й перестраиваемых масштабных блоков, выход каждого j-ro инвер25 тора подключен к третьим входам с (jn-- п + 1)-го по jn-й перестраиваемых масштабных блоков, п+1 входов 1-го сумматора подключены соответст- венно к выходам (пга +1) х (,n)

30 перестраиваемых масштабных блоков, выход первого сумматора подключен к входу второго инвертора и к вторым входам с (п+1)-го по 2п-й перестраиваемых масштабных блоков, выход

сумматора подключен к входу г-го инвертора и вторым входам

первого инвертора и вторым входам с первого по п-й перестраиваемых масштабных блоков,, выход каждого следующего г-го сумматора подключен к

с (гп-п+1)-го по гп-й перестраинаемых масштабных блоков, выход каждого сум- является выходом устройства, первый выход блока управления подклю45 чен к управляющим входам (пга+1)х (т 1,п) перестраиваемых масштабных блоков, второй выход блока управления подключен к управляющим входам (nm+2)x (m l,n) переgQ страиваемых масштабных блоков, третий выход блока управления цодключен к управляющим входам (пта+3)х (,п) перестраиваемых масштабных блоков, каждый следующий S-й выход блока

eg управления подключен к управляющим -выходам (nm + S)x (m 0,n) перестра- иваемь1Х масштабных блоков. Тираж 863 Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое вычислительное устройство | 1987 |

|

SU1506456A1 |

| Устройство для определения коэффициентов разложения корреляционной функции по системе ортонормированных базисных функций | 1985 |

|

SU1287196A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Кусочно-полиномиальный аппроксиматор | 1986 |

|

SU1322327A1 |

| Устройство для диагностирования логических схем | 1988 |

|

SU1684757A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Изобретение относится к области аналоговой вычислительной техники и может быть использовано для интерпретации экспериментальных зависимостей, / Г-I Г-1 JoKm - Пуск в частности для решения задач технической диагностики, задач коррекции динамических характеристик измерительных и управляющих систем. Цель изобретения - повышение быстродействия устройства. Устройство состоит из интеграторов 1(1), 1(2),,..., 1(2п-2), источника эталонного напряжения 2, инверторов 3(1), 3(2), ..., 3(п+1), перестраиваемых масштабных блоков 4, соединенных в матрицу-размерностью п строк на п+1 столбцов, сумматоров 5(1), 5(2), ..., 5(п), блока управления 6. Значения всех идентифицируемых параметров определяются за время реализации одного тестового сигнала, что и обусловливает повышение быстродействия устройства. I ил. S (Л со :л

| Система индентификации параметров объекта | 1977 |

|

SU703779A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Идентификатор параметров динамической системы второго порядка | 1981 |

|

SU1038922A1 |

Авторы

Даты

1987-12-23—Публикация

1985-09-23—Подача