первые входы элементов ИЛИ группы подключены к информационным входам преобразователя, второй вход -го (i 1, п 1) элемента ИЛИ группы соединен с выходом ()-ro элемента ИЛИ группы, выход 1-го элемента ИЛИ группы (,n) соединен с первым входом (i+1)-ro элемента И группы, выход первого элемента ИЛИ группы через nepBbd) элемент НЕ соединен с первым входом первого элемента группы, первый вход (п+1)-го элемента И группы соединен с п-м информационным входом преобразователя, первь1Й управляющий вход преобразователя соединен через второй элемента НЕ с первым вхо 115 9 дом элемента И, выход которого соединен с вторыми входами элементов И группы, выход i-ro (,n-1) элемента И группы подключен к первому вхоДУ (i-l)-ro сумматора по модулю два группы, вторые входы сумматоров по модулю два группы подключены к информационным входам преобразователя третьи входы соединены с выходом первого элемента И группы, а выходы соединены с информационными выходами Преобразователя, вькод второго элемента И группы соединен с выходом переноса преобразователя, второй вход элемента И подключен к второму управляющему входу преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1990 |

|

SU1791816A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

1. УСТРОЙСТВО МАСШТАБИРОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО АНАЛИЗАТОРА, содержащее формирователь синхроимпульсов, регистр дробной части интеграла, сумматор-вычитатель дробной части и регистр дробной части масштаба, причем тактовый вход устройства подключен ко входу формирователя синхроимпульсов, выход которого соединен с входом синхронизации регистра дробной части интеграла, выходы которого соединены с первой группой входов сумматора-вычитателя дробной части, управляющий вход которого подключен к информационному входу устройства, вторая группа входов подключена к выходам регистра дробной части масштаба, а выходы соединены с информационными входами регистра дробной части интеграла, отличающееся тем, что, с целью повышения быстродействия и расширения пределов масштабирования, в. него введены регистр целой части интеграла, преобразователь кодов, сумматор-вычитатель целой части и регистр целой части масштаба, причем выход формиро.вателя синхроимпульсов соединен с входом синхронизации регистра целой части интеграла, выходы информационных разрядов которого соединены с информационными входами преобразователя кодов, информационные выходы которого соединены с первой группой информационных входов сумматора-вычитателя целой части, первый- вход знака которого подключен к выходу знакового разряда регистра целой части интеграла, выхо ды информационньпс разрядов и выход знакового разряда регистра целой части масштаба соединены соответственно с второй группой информационных вхо- § дов и вторым входом знака сумматора(Л вычитателя целой части, выходы которого соединены с информационнь ми входами регистра целой части интеграла, выход старшего разряда которого сое- а динен с выходом устройства, выход; старшего разряда дробной части интеграпа соединен с-первым управляюпщм , СП входом преобразователя кодов и первым О5 -входом переноса сумматора-вычитателя целой части, информационный вход усто ройства подключён к управляющему О5 входу сумматора-вычитателя целой чассо ти и второму управляющему входу преобразователя кодов,выход переноса которого соединен с вторым входом переноса второго сумматора-вычитателя целой части. : 2. Устройство по п. 1, о т л ичающееся тем, что преобразовя тель кодов содержит группу -(-О-го элемента ИЛИ (где п- разрядность информации), труппу (г + 1)-го элемента И, группу сумматоров по мoдyJШ два, два элемента НЕ и элемент И, причем

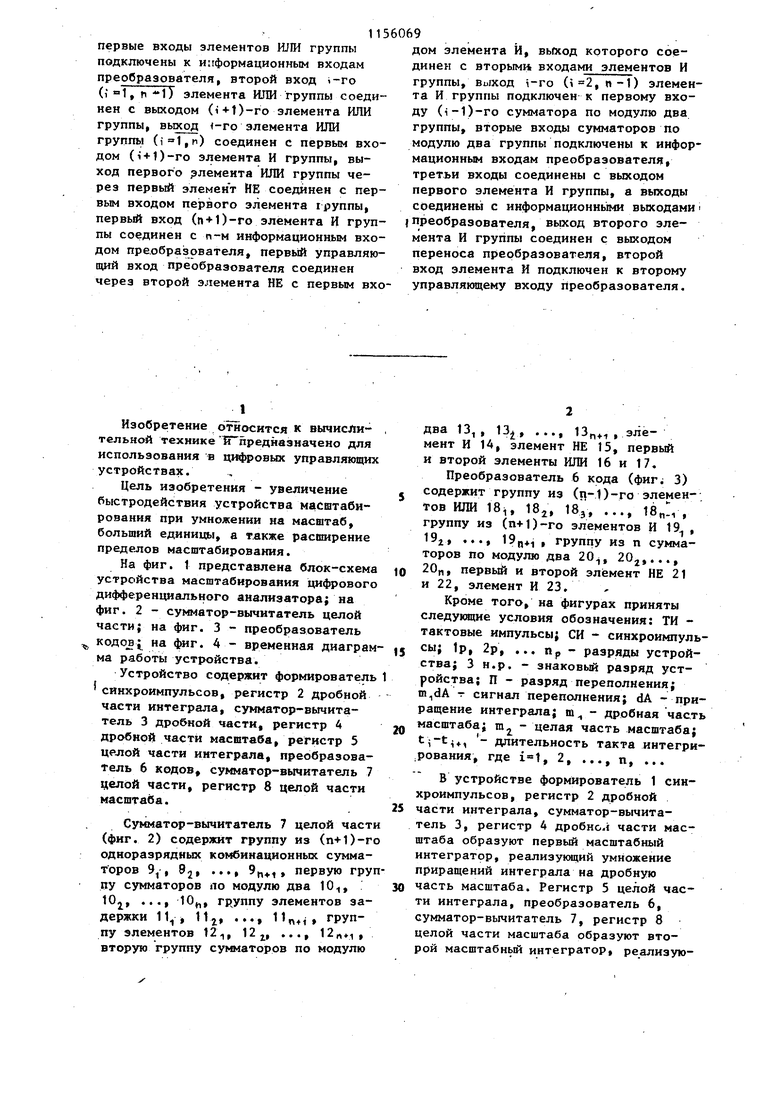

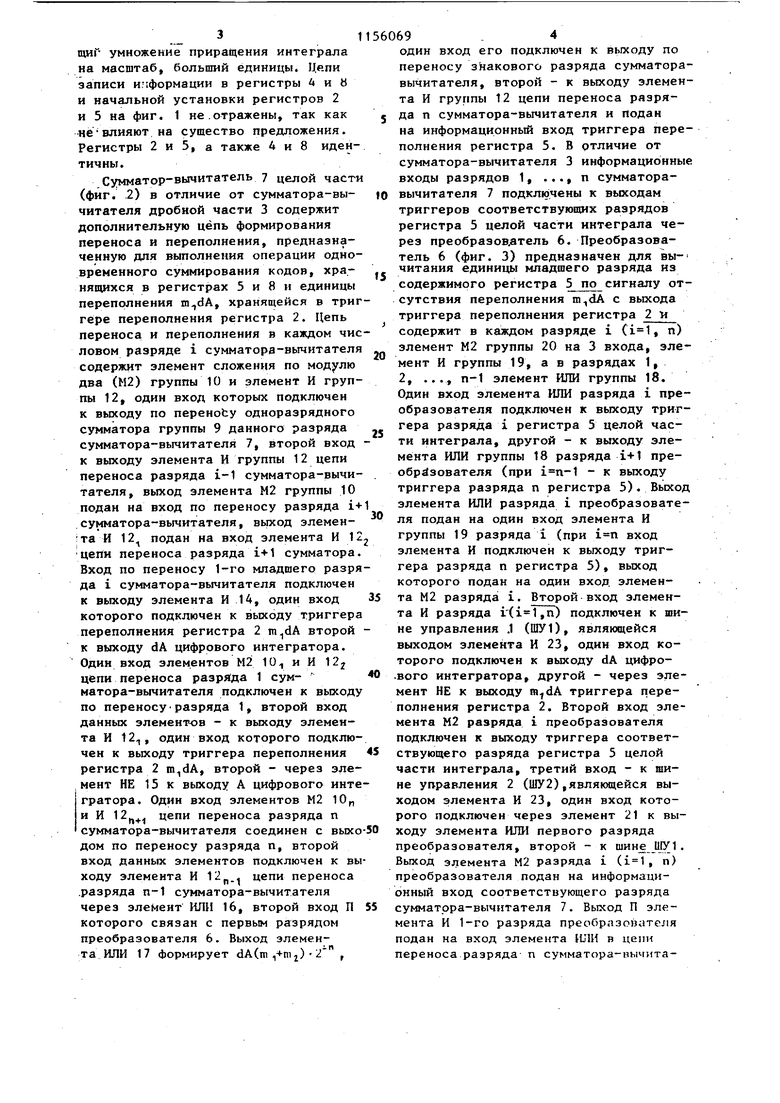

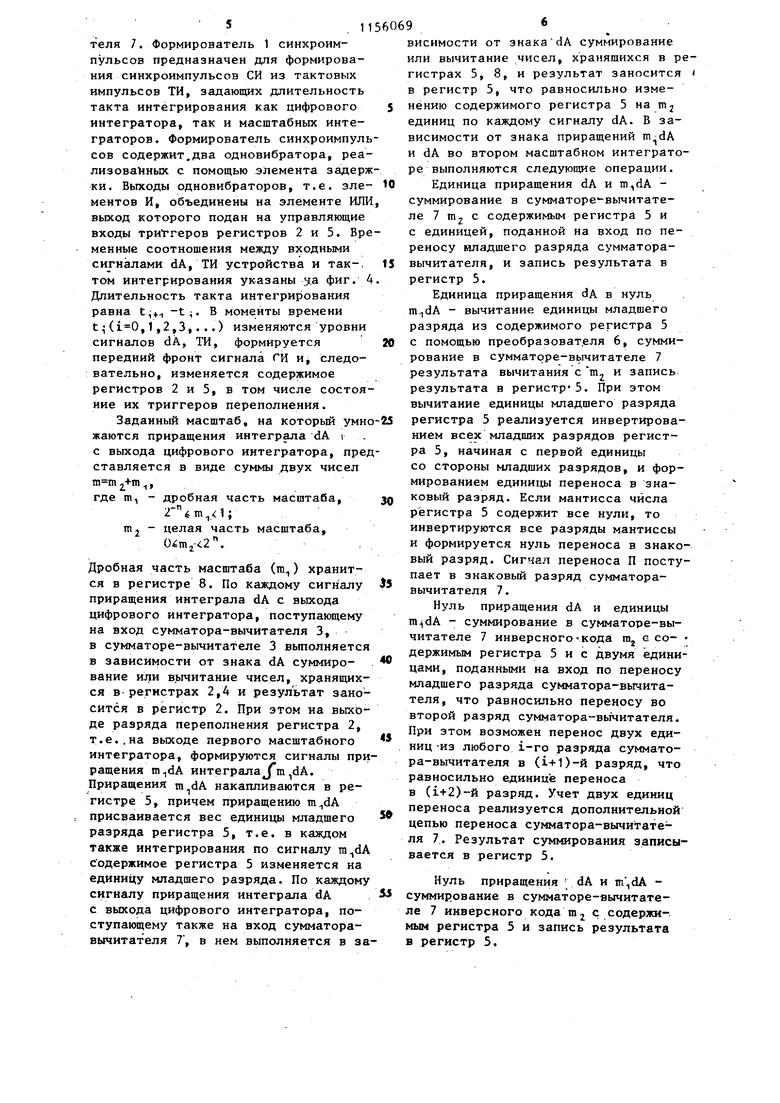

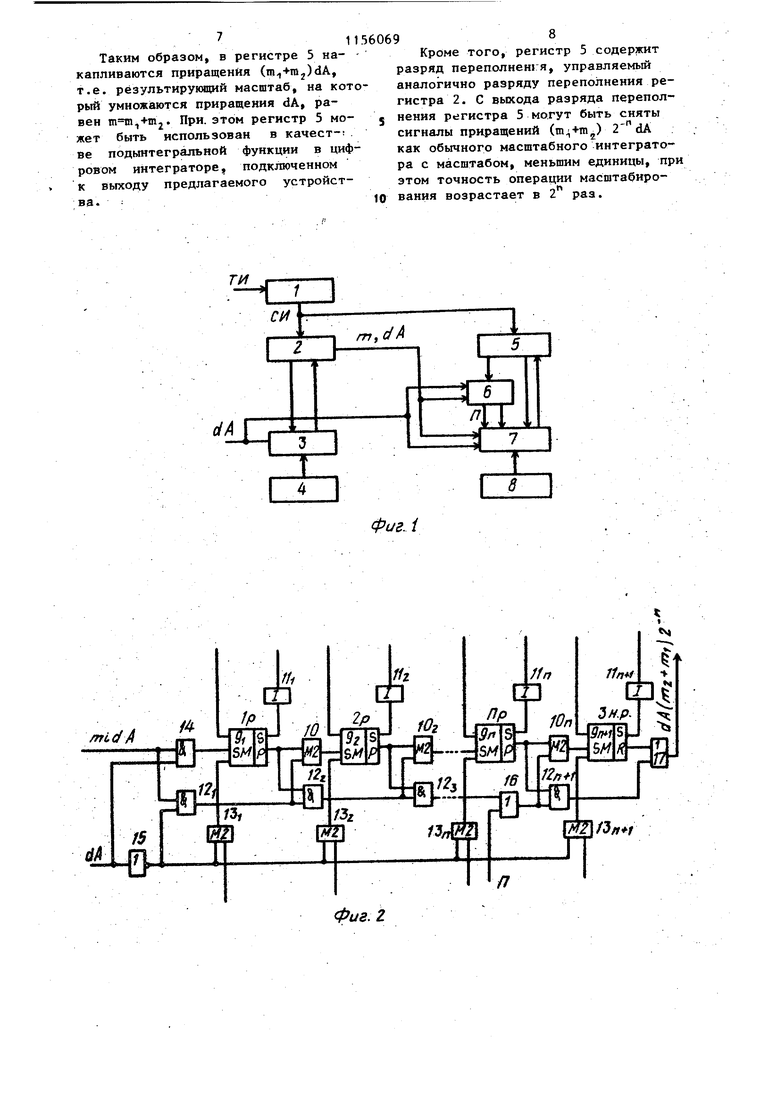

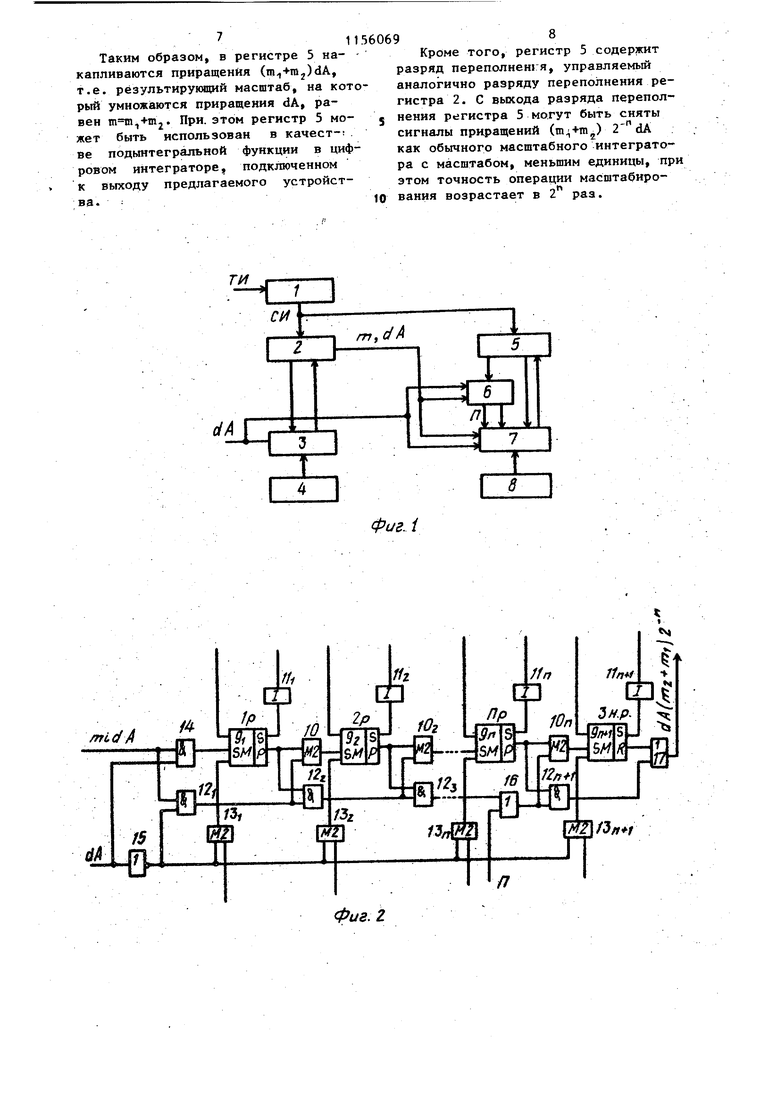

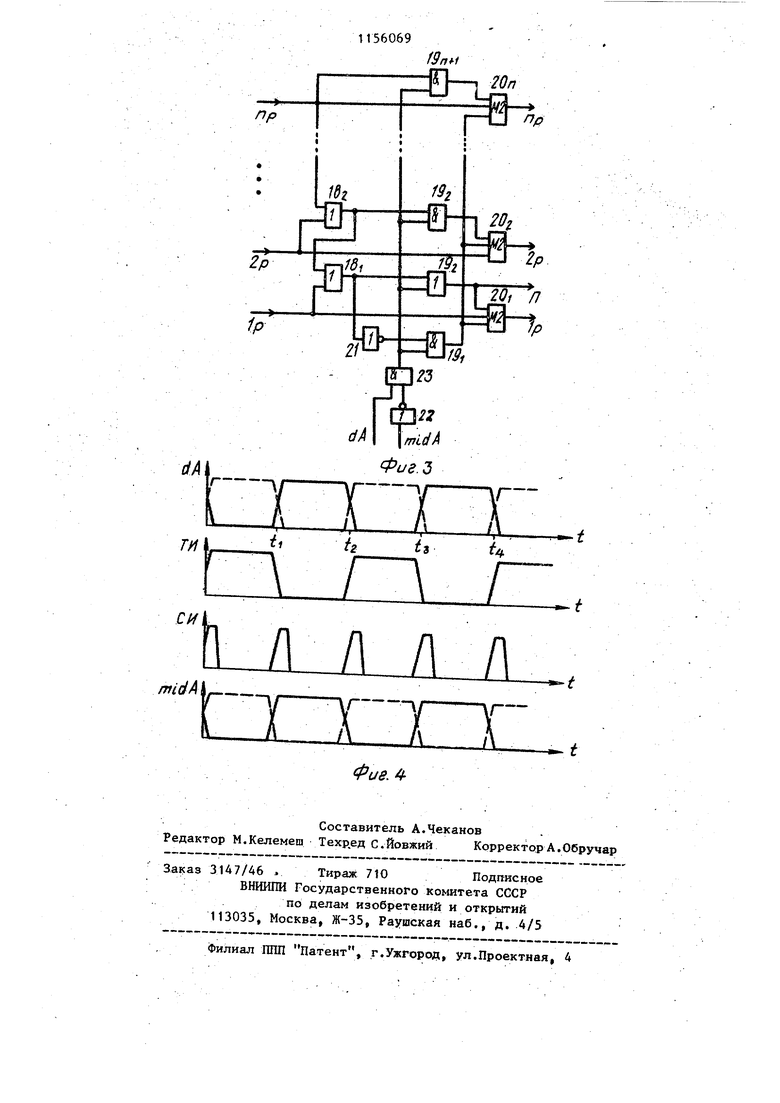

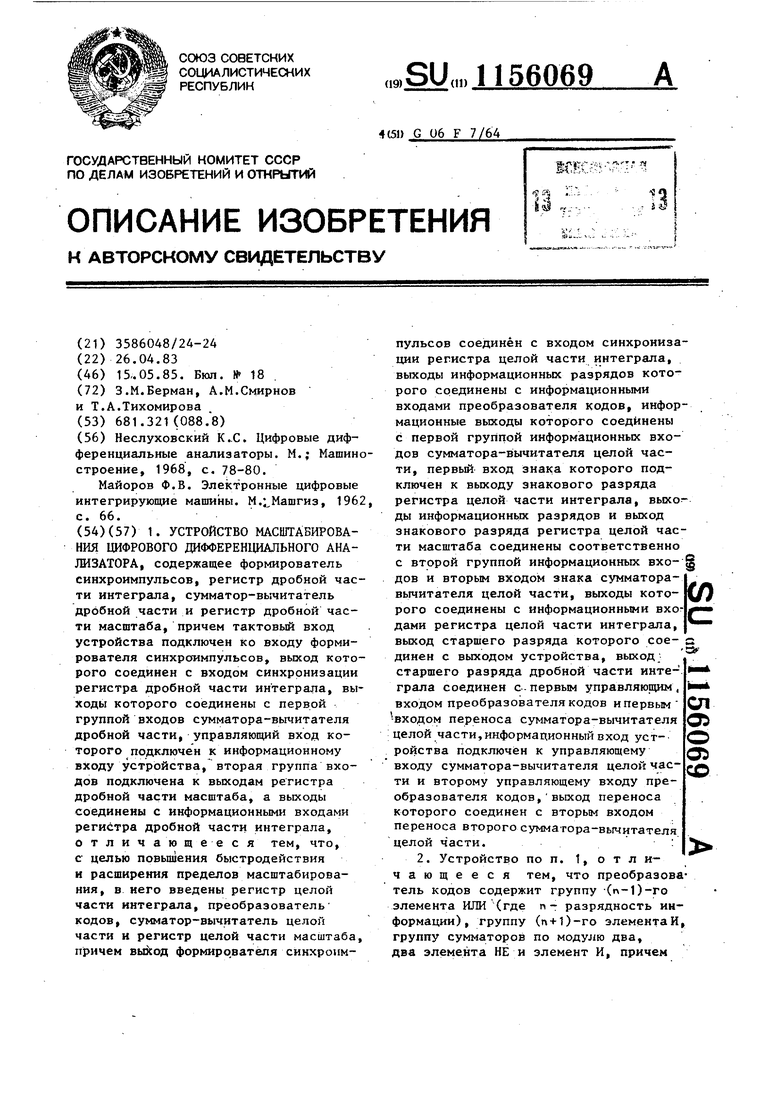

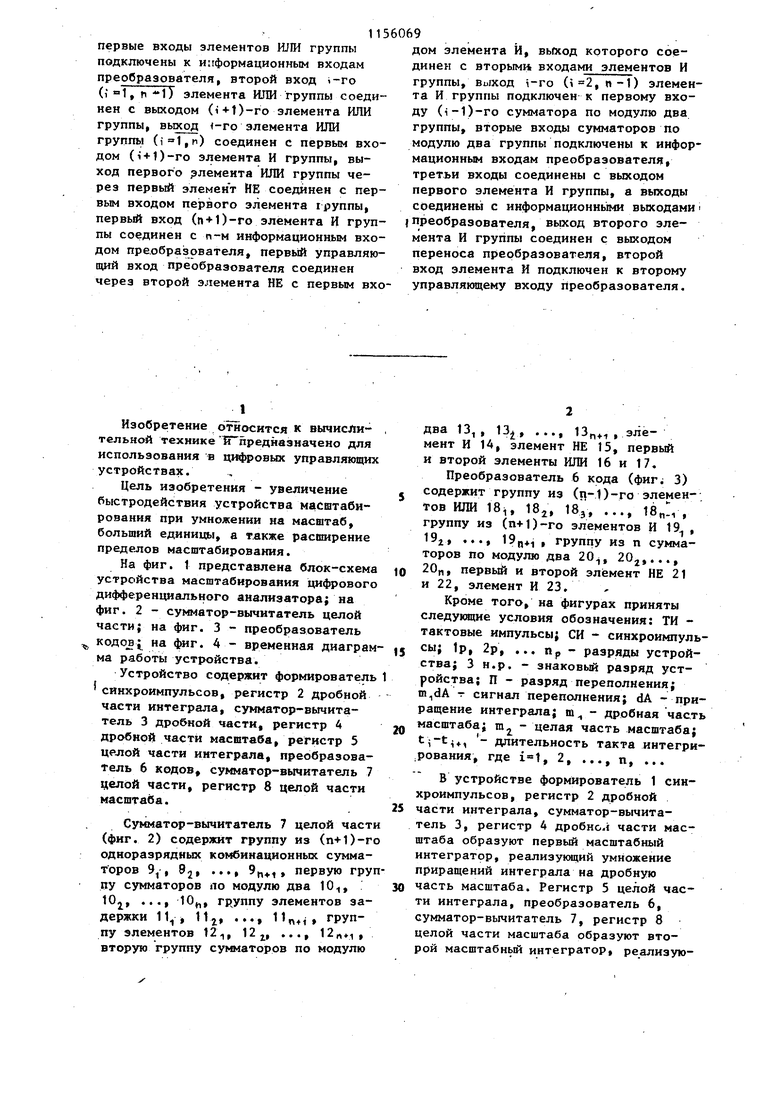

Изобретение относится к вычислительной технике 15Гпредназначено для использования в Ц1 фовых управляющих устройствах. Цель изобретения - увеличение быстродействия устройства масштабирования при умножении на масштаб, больший единицы, а т.акже расширение пределов масштабирования. На фиг. 1 представлена блок-схема устройства масштабирования цифрового дифференциального анализатора; на фиг. 2 - сумматор-вычитатель целой части; на фиг. 3 - преобразователь KOAoji на фиг. 4 - временная диаграм ма работы устройства. Устройство содержит формирователь синхроимпульсов, регистр 2 дробной части интеграла, сумматор-вычитатель 3 дробной части, регистр 4 дробной части масштаба, регистр 5 целой части интеграла, преобразователь 6 кодов, сумматор-вычитатель 7 целой части, регистр 8 целой части масштаба. Сумматор-вычитатель 7 целой част (фиг. 2) содержит группу из (п+1)-г одноразрядных комбинационных сумматоров 9, 92 первую гру пу сумматоров по модулю два 10, 10,, ..., 10, группу элементов задержки 11, 112, ..., 11п41 группу элементов 12-,, 12, ..., , вторую группу суьматоров по модулю два 13,, 13,, ..., 13f,.i , элемент И 14, элемент НЕ 15, первый и второй элементы ИЛИ 16 и 17. Преобразователь 6 кода (фиг; 3) содержит группу из (ц-1)-го элементов ИЛИ 18,, 18, 18э, ..., 18„ , группу из (п+1)-го элементов И 19 , 19j, ,.., 19(1+1 группу из п сумматоров по модулю два 20, 20,..., 20„, первый и второй элемент НЕ 21 и 22, элемент И 23. Кроме того, на фигурах приняты следуквдие условия обозначения: ТИ тактовые импульсы; СИ - синхроимпульсы; 1р, 2р, ... Пр - разряды устройства; 3 н.р. - знаковый разряд устройства; П - разряд переполнения; т сигнал переполнения; dA - приращение интеграла; ю - дробная часть масштаба; га - целая часть масштаба; , - длительность такта интегри рования, где , 2п, ... В устройстве формирователь 1 синхроимпульсов, регистр 2 дробной части интеграла, сумматор-вычитатель 3, регистр 4 дробней части масштаба образуют первый масштабный интегратор, реализующий умножение приращений интеграла на дробную часть масштаба. Регистр 5 целой части интеграла, преобразователь 6, сумматор-вычитатель 7, регистр 8 целой части масштаба образуют второй масштабный интегратор, реализуюЩИГ умножение приращения интеграла на масштаб, больший единицы. Цепи записи информации в регистры 4 и Н и начальной установки регистров 2 и 5 на фиг. 1 не.отражены, так как невлияют на существо предложения. Регистры 2 и 5, а также 4 и 8 идентичны. Сумматор-вычитатель 7 целой части (фиг. .2) в отличие от сумматора-вычитателя дробной части 3 содержит дополнительную цепь формирования переноса и переполнения, предназначенную для выполнения операции одно временного суммирования кодов, хранящихся в регистрах 5 и 8 и единицы переполнения , хранящейся в три reipe переполнения регистра 2. Цепь переноса и переполнения в каждом чис ловом разряде i сумматора-вычитателя содержит элемент сложения по модулю два (М2) группы 10 и элемент И группы 12, один вход которых подключен к выходу по переноЬу одноразрядного сумматора группы 9 данного разряда сумматора-вычитателя 7, второй вход к выходу элемента И группы 12 цепи переноса разряда i-1 сумматора-рычитателя, выход элемента М2 группы 10 подан на вход по переносу разряда i+ .сумматора-вычитателя, вьпсод элемента И 12 подан на вход элемента И 12 цепи переноса разряда i-bl сумматора Вход по переносу 1-го младшего разря да i сумматора-вычитателя подключен к выходу элемента И 14, один вход которого подключен к выходу триггера переполнения регистра 2 второй к выходу dA цифрового интегратора. Один вход элементов М2 10-, и И 12 цепи переноса разряда 1 сумматора-вычитателя подключен к выходу по переносуразряда 1, второй вход данных элементов - к выходу элемента И 12, один вход которого подключен к вьжоду триггера переполнения регистра 2 , второй - через элемент НЕ 15 к выходу А цифрового инте гратора. Один вход элементов М2 10„ и И 12j| цепи переноса разряда п сумматора-вычитателя соединен с выхо дом по переносу разряда п, второй вход данных элементов подключен к вы ходу элемента И 12. цепи переноса .разряда п-1 сумматора-вычитателя через элемент ИЛИ 16, второй вход П которого связан с первым разрядом преобразователя 6. Выход элемента ИЛИ 17 формирует dA(m,mj)2 , 69 - 4 один вход его подключен к вьгходу по переносу знакового разряда сумматоравычитателя, второй - к выходу элемента И группы 12 цепи переноса разряда п сумматора-вычитателя и подан на информационный вход триггера переполнения регистра 5. В отличие от сумматора-вычитателя 3 информационные входы разрядов 1, ..., п сумматоравычитателя 7 подключены к выходам триггеров соответствующих разрядов регистра 5 целой части интеграла через преобразователь 6. Преобразователь 6 (фиг. 3) предназначен для вычитания единицы младшего разряда из содержимого регистра сигналу отсутствия переполнения m.,dA с выхода триггера переполнения регистра 2 я содержит в каждом разряде i (, п) элемент М2 группы 20 на 3 входа, элемент И группы 19, а в разрядах 1, 2, ..., п-1 элемент ИЛИ группы 18. Один вход элемента ИЛИ разряда i преобразователя подключен к выходу триггера разряда i регистра 5 целой части интеграла, другой - к выходу элемента ИЛИ группы 18 разряда i+1 преобр зователя (при - к выходу триггера разряда п регистра 5). Выход элемента ИЛИ разряда i преобразователя подан на один вход элемента И группы 19 разряда i (при вход элемента И подключен к выходу триггера разряда п регистра 5), выход которого подан на один вход, элемента М2 разряда i. Второй вход элемента И разряда i( ,п) подключен к шине управления .1 (ШУ1), являющейся выходом элемента И 23, один вход которого подключен к выходу dA цифрового интегратора, другой - через элемент НЕ к выходу m.,dA триггера переполнения регистра 2. Второй вход элемента М2 разряда i преобразователя подключен к выходу триггера соответствующего разряда регистра 5 целой части интеграла, третий вход - к шине управления 2 (ШУ2),являющейся выходом элемента И 23, один вход которого подключен через элемент 21 к выходу элемента ИЛИ первого разряда преобразователя, второй - к шине UIYI . Выход элемента М2 разряда i (, n) преобразователя подан на информационный вход соответствующего разряда сумматора-вычитателя 7. Выход П элемента И 1-го разряда преобразователя подан на вход элемента ИЛИ в цепи ереноса разряда- п сумматора-вычитателя 7. Формирователь 1 синхроимпульсов предназначен для формирования синхроимпульсов СИ из тактовых импульсов ТИ, задающих длительность такта интегрирования как цифрового интегратора, так и масштабных интеграторов. Формирователь синхроимпуль сов содержит,два одновибратора, реализованных с помощью элемента задерж ки. Выходы одновибраторов, т.е. элементов И, объединены на элементе ИЛИ выход которого подан на управляющие входы триггеров регистров 2 и 5. Вре менные соотношения между входными сигналами dA, ТИ устройства и так-, том интегрирования указаны уа фиг. Длительность такта интегрирования равна t,. t;. В моменты времени t(,1,2,3,...) изменяются уровни сигналов dA, ТИ, формируется передний фронт сигнала ГИ и, следовательно, изменяется содержимое регистров 2 и 5, в том числе состоя ние их триггеров переполнения. Заданный масштаб, на который умн жаются приращения интеграла dA i с выхода цифрового интегратора, пре ставляется в виде суммы двух чисел +m , где т, - дробная часть масштаба. 2 6 m 1; целая часть масштаба, Дробная часть масштаба (т) хранится в регистре 8. По каждому сигналу приращения интеграла dA с вьжода цифрового интегратора, поступающему на вход сумматора-вычитателя 3, в сумматоре-вычитателе 3 выполняется в зависимости от знака dA суммирование или в.ычитание чисел, хранящихся в регистрах 2,4 и результат заносится в регистр 2. При этом на выходе разряда переполнения регистра 2, т.е..на выходе первого масштабного интегратора, формируются сигналы при ращения интeгpaлa m dA. Приращения накапливаются в регистре 5, причем приращению присваивается вес единицы младшего разряда регистра 5, т.е. в каждом также интегрирования по сигналу Содержимое регистра 5 изменяется на единицу младшего разряда. По каждому сигналу приращения интеграла dA с выхода цифрового интегратора, поступающему также на вход сумматоравычитателя 7, в нем выполняется в за 1 . исимости от знакаdA суммирование или вычитание чисел, хранящихся в регистрах 5, 8, и результат заносится в регистр 5, что равносильно изменению содержимого регистра 5 на т единиц по каждому сигналу dA. В зависимости от знака приращений и dA во втором масштабном интеграторе выполняются следующие операции. Единица приращения dA и m,dA суммирование в сумматоре-вычитателе 7 т с содержимым регистра 5 и с единицей, поданной на вход по переносу младшего разряда сумматоравычитателя, и запись результата в регистр 5. Единица приращения dA в нуль - вычитание единицы младшего разряда из содержимого регистра 5 с помощью преобразователя 6, суммирование в сумматоре-вьгчитателе 7 результата вычитания с т и запись результата в регистр-5. При этом вычитание единицы младшего разряда регистра 5 реализуется инвертированием всех младших разрядов регистра 5, начиная с первой единицы со стороны младших разрядов, и формированием единицы переноса в знаковый разряд. Если мантисса числа регистра 5 содержит все нули, то инвертируются все разряды мантиссы и формируется нуль переноса в знаковый разряд. Сигнал переноса П поступает в знаковый разряд сумматоравычитателя 7. Нуль приращения dA и единицы - суммирование в сумматоре-вычитателе 7 инверсного-кода га с со- держимым регистра 5 и с двумя ieдиницами, поданными на вход по переносу младшего разряда сумматора-вьиитателя, что равносильно переносу во второй разряд сумматора-вьгчитателя. При этом возможен перенос двух единиц -из любого i-ro разряда сумматора-вычитателя в (1+1)-й разряд, что равносильно единице переноса в (1+2)-й разряд. Учет двух единиц переноса реализуется дополнительной цепью переноса сумматора-вычитателя 7. Результат суммирования записывается в регистр 5. Нуль приращения ; dA и суммирование в сумматоре-вычитателе 7 инверсного кода mj с содержиЮЛ4 регистра 5 и запись результата в регистр 5.

Таким образом, в регистре 5 на- капливаются приращения ()dA, т.е. результирующий масштаб, на который умнож аются приращения dA, равен . При. этом регистр 5 может быть использован в качест- ве подынтегральной функции в цифровом интеграторе подключенном к выходу предлагаемого устройства.

ТИ

1

Кроме того, регистр 5 содержит разряд переполненгя, управляемый аналогично разряду переполнения регистра 2. С выхода разряда переполнения регистра 5 могут быть сняты сигналы приращений (.) 2 dA как обычного масштабного интегратора с масштабом, меньшим единицы, при этом точность операции масштабирования возрастает в 2 раз.

фиг. i

| Неслуховский К..С, Цифровые дифференциальные анализаторы | |||

| М.; Машиностроение, 1968, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Майоров Ф.В | |||

| Электронные цифровые интегрирующие машины | |||

| М.;,Машгиз, 1962, с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

Авторы

Даты

1985-05-15—Публикация

1983-04-26—Подача