Изобретение относится к вычислительной технике и может быть использовано при построении специализированных цифровых вычислительных сие- тем.

Цель изобретения - повьппение производительности за счет возможности одновременного выполнения операции деления над несколькими парами one- рандов.

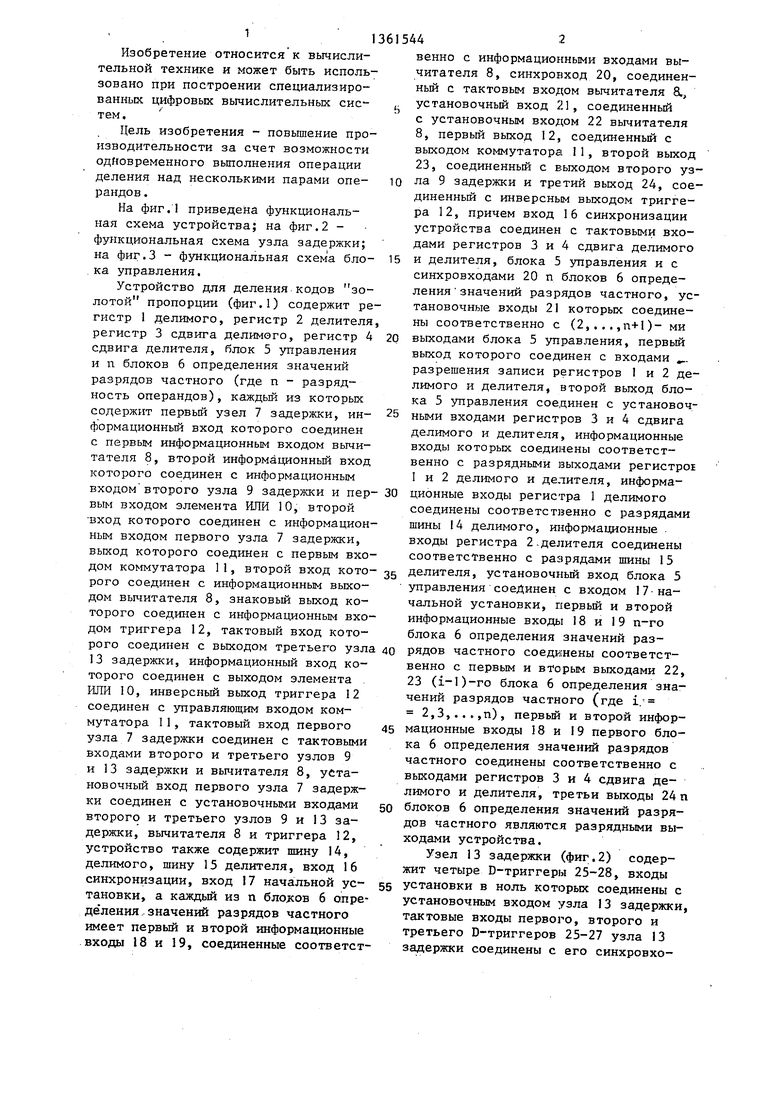

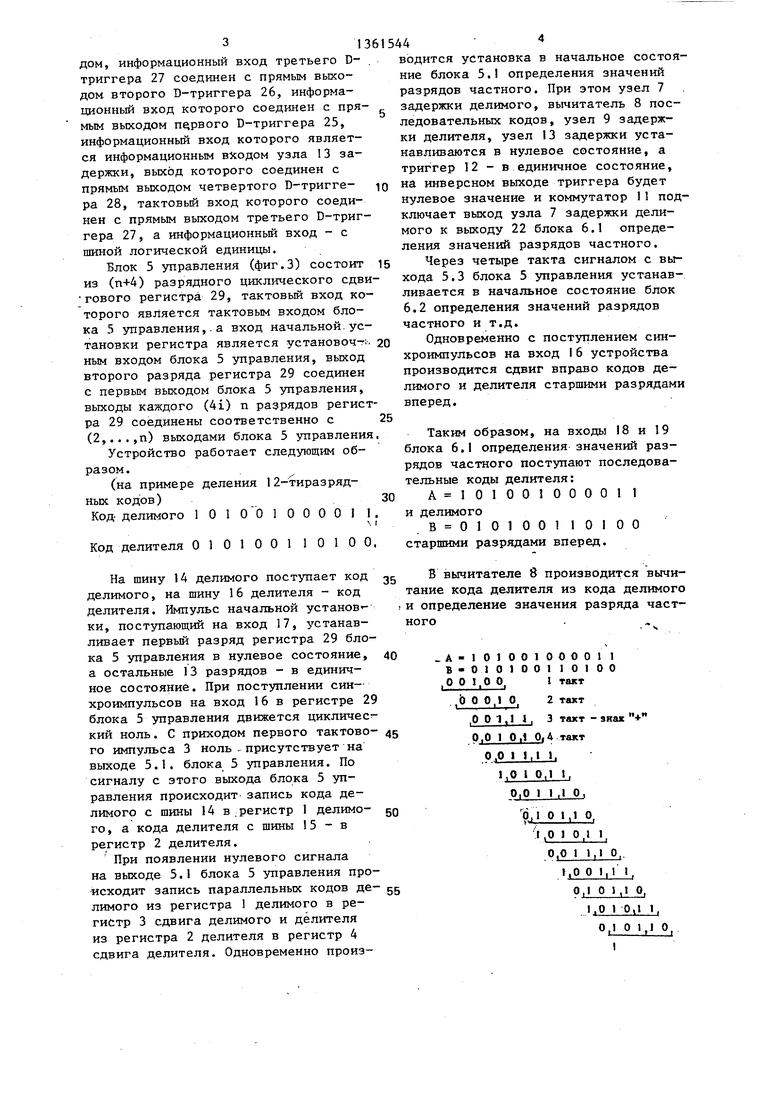

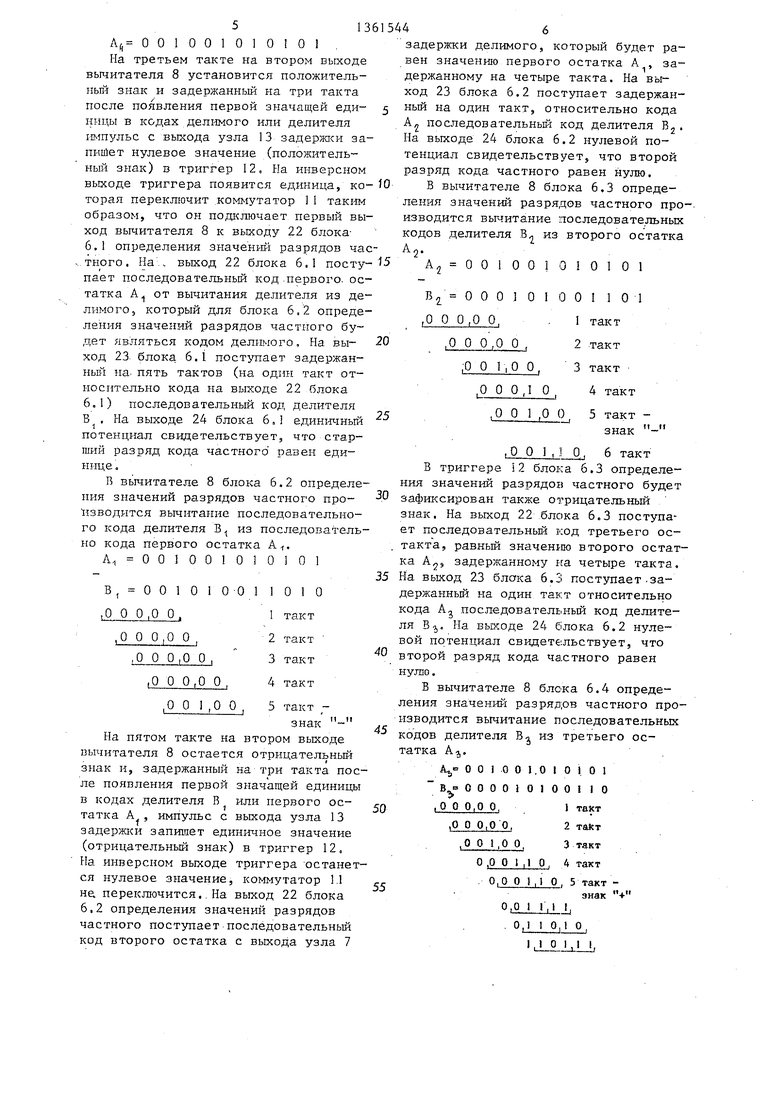

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема узла задержки; на фиг.З - функциональная схема бло- ка управления.

Устройство для деления кодов золотой пропорции (фиг.1) содержит регистр 1 делимого, регистр 2 делителя регистр 3 сдвига делимого, регистр 4 сдвига делителя, блок 5 управления и п блоков 6 определения значений разрядов частного (где п - разрядность операндов), каждый из которых содержит первый узел 7 задержки, ин- формационный вход которого соединен с первым информационным входом вычи- тателя 8, второй информационньй вход которого соединен с информационным входом второго узла 9 задержки и пер- вым входом элемента ИЛИ 10, второй вход которого соединен с информационным входом первого узла 7 задержки, выход которого соединен с первым входом коммутатора 11, второй вход кото- 35 делителя, установочный вход блока 5

рого соединен с информационным выходом вьгчитателя 8, знаковый выход которого соединен с информационным входом триггера 12, тактовый вход которого соединен с выходом третьего узла 40 13 задержки, информационный вход которого соединен с выходом элемента ШШ 10, инверсный выход триггера 12 соединен с управляющим входом коммутатора 1I, тактовый вход первого узла 7 задержки соединен с тактовыми входами второго и третьего узлов 9 и 13 задержки и вычитателя 8, установочный вход первого узла 7 задержки соединен с установочными входами второго и третьего узлов 9 и 13 задержки, вычитателя 8 и триггера 12, устройство также содержит шину 14, делимого, шину 15 делителя, вход 16 синхронизации, вход 17 начальной установки, а каждый из п блоков 6 определения значений разрядов частного имеет первый и второй информационные входы 18 и 19, соединенные соответступравления соединен с входом 17-начальной установки, первый и второй информационные входы 18 и 19 п-го блока 6 определения значений разрядов частного соединены соответственно с первым и вторым выходами 22, 23 (i-l)-ro блока 6 определения значений разрядов частного (где i/ 2,3,...,п), первьй и второй инфор- 45 мационные входы 18 и 19 первого блока 6 определения значений разрядов частного соединены соответственно с выходами регистров 3 и 4 сдвига делимого и делителя, третьи выходы 24п блоков 6 определения значений разрядов частного являются разрядными выходами устройства.

Узел 13 задержки (фиг,2) содержит четыре D-триггеры 25-28, входы установки в ноль которых соединены с установочным входом узла 13 задержки тактовые входы первого, второго и третьего D-триггеров 25-27 узла 13 задержки соединены с его синхровхо50

55

венно с информационными входами вы- читателя 8, синхровход 20, соединенный с тактовым входом вьгчитателя 8. установочный вход 21, соединенньш с установочным входом 22 вычитателя 8, первый выход 12, соединенньй с выходом коммутатора I1, второй выход 23, соединенный с выходом второго узла 9 задержки и третий выход 24, соединенньш с инверсным выходом триггера 12, причем вход 16 синхронизации устройства соединен с тактовыми входами регистров 3 и 4 сдвига делимого и делителя, блока 5 управления и с синхровходами 20 п блоков 6 определения значений разрядов частного, установочные входы 21 которых соединены соответственно с (2,...,п+1)- ми выходами блока 5 управления, первый выход которого соединен с входами . разрешения записи регистров 1 и 2 делимого и делителя, второй выход блока 5 управления соединен с установочными входами регистров 3 и 4 сдвига делимого и делителя, информационные входы которых соединены соответственно с разрядными выходами регистров I и 2 делимого и делителя, информационные входы регистра 1 делимого соединены соответственно с разрядами шины 14 делимого, информационные . входы регистра 2,делителя соединены соответственно с разрядами шины 15

0

управления соединен с входом 17-начальной установки, первый и второй информационные входы 18 и 19 п-го блока 6 определения значений разрядов частного соединены соответственно с первым и вторым выходами 22, 23 (i-l)-ro блока 6 определения значений разрядов частного (где i/ 2,3,...,п), первьй и второй инфор- 5 мационные входы 18 и 19 первого блока 6 определения значений разрядов частного соединены соответственно с выходами регистров 3 и 4 сдвига делимого и делителя, третьи выходы 24п блоков 6 определения значений разрядов частного являются разрядными выходами устройства.

Узел 13 задержки (фиг,2) содержит четыре D-триггеры 25-28, входы установки в ноль которых соединены с установочным входом узла 13 задержки, тактовые входы первого, второго и третьего D-триггеров 25-27 узла 13 задержки соединены с его синхровхо0

5

дом, информационный вход третьего D- триггера 27 соединен с прямым выходом второго D-триггера 26, информационный вход которого соединен с прямым выходом первого D-триггера 25, информационный вход которого является информационным входом узла 13 задержки, выход которого соединен с прямым выходом четвертого D-тригге- ра 28, тактовый вход которого соединен с прямым выходом третьего D-триггера 27, а информационный вход - с шиной логической единицы.

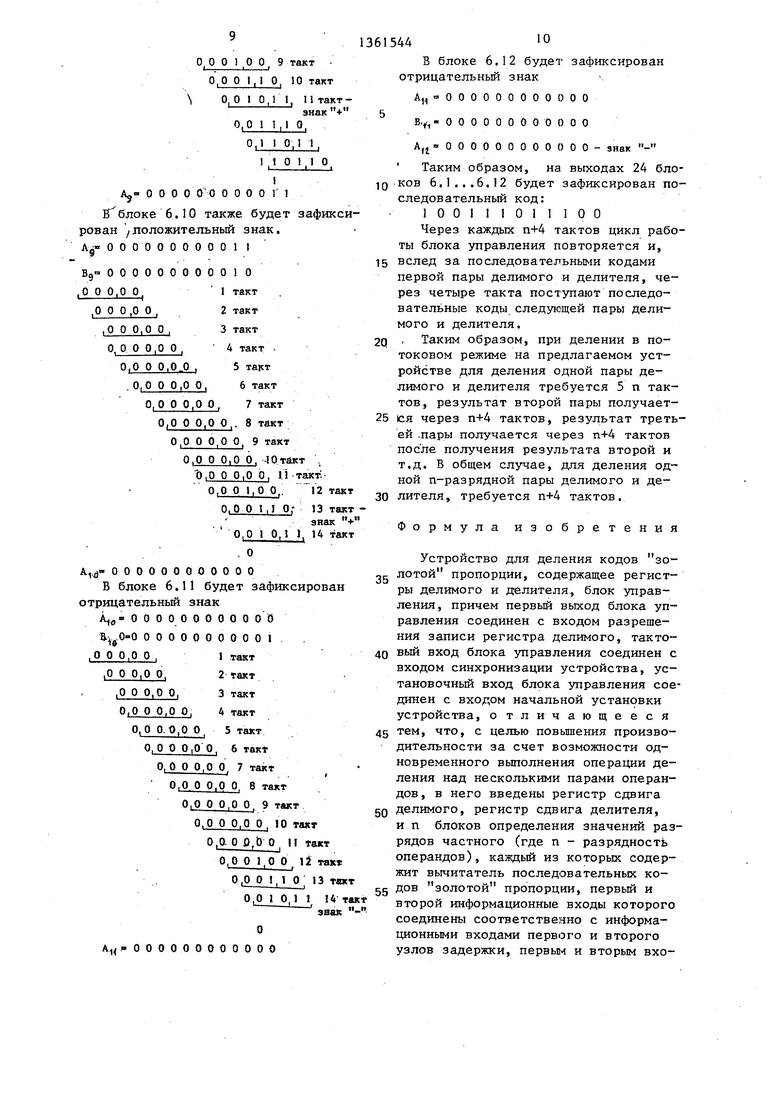

Блок 5 управления (фиг.З) состоит из (п+4) разрядного циклического сдви- гового регистра 29, тактовьй вход которого является тактовым входом блока 5 управления,.а вход начальной.установки регистра является установоч-;. ным входом блока 5 управления, выход второго разряда регистра 29 соединен с первым выходом блока 5 управления, выходы каждого (41) п разрядов регистра 29 соединены соответственно с (2,...,п) выходами блока 5 управления

Устройство работает следующим образом.

(на примере деления 12-тиразрядных кодов) Код делимого 1 О 1 О О 1 О О О О 1 1.

г

Код делителя 0101001 10100.

На шину 14 делимого поступает код делимого, на шину 16 делителя - код делителя. Импульс начальной установ - ки, поступающий на вход 17, устанавливает первый разряд регистра 29 блока 5 управления в нулевое состояние, а остальные 13 разрядов - в единичное состояние. При поступлении синхроимпульсов на вход 16 в регистре 29 блока 5 управления движется циклический ноль. С приходом первого тактового импульса 3 ноль - присутствует на выходе 5.1. блока 5 управления. По сигналу с этого выхода блока 5 управления происходит запись кода делимого с шины 14 в ;регистр 1 делимого , а кода делителя с шины 15 - в регистр 2 делителя.

При появлении нулевого сигнала на выходе 5.1 блока 5 управления происходит запись параллельных кодов де- лимого из регистра 1 делимого в регистр 3 сдвига делимого и делителя из регистра 2 делителя в регистр 4 сдвига делителя. Одновременно произ

5

0

5

водится установка в начальное состояние блока 5. определения значений разрядов частного. При этом узел 7 задержки делимого, вычитатель 8 последовательных кодов, узел 9 задержки делителя, узел 13 задержки устанавливаются в нулевое состояние, а триггер 12 - в единичное состояние, на инверсном выходе триггера будет нулевое значение и коммутатор 11 подключает выход узла 7 задержки делимого к выходу 22 блока 6.1 определения значений разрядов частного.

Через четыре такта сигналом с выхода 5.3 блока 5 управления устанавливается в начальное состояние блок 6.2 определения значений разрядов частного и т.д.

Одновременно с поступлением синхроимпульсов на вход I6 устройства производится сдвиг вправо кодов делимого и делителя старшими разрядами вперед.

Таким образом, на входы 18 и 19 блока 6.1 определения значений разрядов частного поступают последовательные коды делителя:

А 101001000011 и делимого

8 010100110100 старшими разрядами вперед.

В вычитателе 8 производится вычитание кода делителя из кода делимого и определение значения разряда частного

3 такт - знак

н..«

А-101001000011 В-0 101001 10100 ,001,00,I такт

,Ь О 0,1 О, 2 такт ,0 О 1 , 3 такт 0,0 1 O.i 0,4 такт 0.0 1.1 1. 1.0 1 0,1 1, 0,0 1 1 .1 О,

0.101.10

)U .I I

J,0 1 0,t 1

.OiO Ь о,

1,0 о 1)1 1, 1,1 0 1 0,1 1,

о. о J Oj I

00 1001010101

На третьем такте на втором выходе вычитателя 8 установится положитель- ньш знак и задержанный на три такта после появления первой значащей единицы в кодах делимого или делителя ттулъс с выхода узла 13 задерлжи за- пийет нулевое значение (положительный знак) в триггер 12, Ыа инверсном выходе триггера появится единица, которая переключит .коммутатор 1I таким образом, что он подключает первый выход вычитателя 8 к выходу 22 блока- 6.1 определения значенж разрядов час .тного. На., выход 22 блока 6.1 поступает последовательный код .первого, остатка А от вычитания делителя из делимого, который для блока 6.2 определения значений разрядов частного будет являться кодом делимого. На выход 23 блока 6.1 поступает задержан- HLDi на. пять тактов (на один такт относительно кода на выходе 22 блока 6.1) последовательный код делителя В , На выходе 24 блока 6, 1 единтшый потенциал свидетельствует, что старший разряд кода частного равен единице .

В вьгчитателе 8 блока 6.2 определения значений разрядов частного про- изводится вычитание последовательного кода делителя В из последовательно кода первого остатка А. А, 001001010101

знак -

На пятом такте на втором выходе цычитателя 8 остается отрицательный знак и, задержанный на три такта после появления первой значащей единицы в кодах делителя В или первого остатка А , импульс с выхода узла 13 задерж1си запишет единичное значение (отрицательный знак) в триггер 12, На инверсном выходе триггера останется нулевое значение, коммутатор 1.1 не переключится..На выход 22 блока 6.2 определения значений разрядов частного поступает последовательный код второго остатка с выхода узла 7

задержки делимого, который будет равен значению первого остатка А , задержанному на четыре такта. На выход 23 блока 6.2 поступает задержанный на один такт, относительно кода А2 последовательньй код делителя Bj. На выходе 24 блока 6.2 нулевой потенциал свидетельствует, что второй разряд кода частного равен нулю.

В вычитателе 8 блока 6.3 определения значений разрядов частного производится вычитание последовательных кодов делителя В,, из второго остатка Aj.

Aj О О

О О О i О 1 О 1

Б О О О О I О О I 1 О 1 ,0 О 0,0 О, . 1 такт

0

5

0

5

0

5

,00 1 , О,, 6 такт В триггере 12 блока 6.3 определения значений разрядов частного будет зафиксирован также отрицательный знак. На выход 22 блока 6.3 поступает последовательньй код третьего ос- такта, равньш значению второго остатка А, задержанному на четыре такта. На выход 23 блака 6.3 поступает-за- держанньй на один такт относительно кода AJ последовательный код делителя В. На выходе 24 блока 6.2 нулевой потенциал свидете;льствует, что второй разряд кода частного равен куто,

В вычитателе 8 блока 6.4 определения значений разрядов частного производится вычитание последовательных кодов делителя В из третьего остатка А,,.. А.., О О 1 О О J. О I О I О 1

В ° 000010100110

,0 о 0,0 о,1 такт

,0 О 0,00,2 такт

,001,0 О,3 такт

О ,0 01 |1 О,4 такт

0|0 О 1,1 О , 5 такт знак «

0,011,11д

О, 3 0,1 О, J-°-lal b

71

1,0 1 1,1 0 0,1 I 0,1 1 , 1,01 1,1 о, 1,0 о 1,1 1, 0,0 1 1,10, 0. t I о I t

1

о о о о 1 101 1001

в триггере 12 блока 6.4 определения значений разрядов частного будет зафиксирован положительный знак.

В блоке 6.5 будет зафиксирован также положительный знак.

А 000011011001

в. О 00001010011

ч ,

о 0,0 о , . 0 о 0,0 о,

,0 о 0,0 о, о 0,0 о, 0.0 о 1 ,00.

1такт

2такт

3такт

4такт

5такт

0,0 О 1,10, 6 такт

0,0 1 0,1 1, 7 такт знак + О, I 01,1 О ,

1,0 1 1,11, 1 ,001,1 о, 0,0 о 1,1 о, 0.0 1 0,1 1 , 0.1 о 1,1 0.

1 о 1 0,1 1.

А 000001 100010 в блоке 6.6 будет зафиксирован акже положительный знак.

.А 000001100010 В 0 О О О О О 1 О 1 001 |0 6 0,0 такт

,0 О О ,0 О 2 такт

,0 О 0,0 так

0,0 О 0,0 0 4 такт 0,0 О 0,0 0 5« такт 0|0.0 1,1 О, 6 такт 0,0 О 1,1 0 7 такт

0,0 1 0,1 1 8 такт- знак + О , О 1,1 о

1. I 1 о I 1

oj-LAUL,

J о , JL 1

00000001 101 1

3615448

В блоке 6.7 будет зафиксирован отрицательный знак

А« 000000011 011

Bg 000000010100

.о о 0,0 о,

, такт

,0 О 0,0 О ,2 такт

0 О 0,0 О ,3 такт

,0 О 0,0 О, 4 такт ,0 О 0.0 О, 5 такт .0 О 0,0 О, 6 такт ,0 О 0,0 О, 7 такт ,0 00,0 О , 8 такт ,0 01,0 0 9 такт

,0 О 0,1 О, 10 такт - знак -

,001,1 I ,И такт;

. V

В блоке 6.8 будет зафиксирован положительный знак, А 000000011011

В,- О О О О О О О О I О 1 О ,Р о 0,0 о,I такт

,0 О 0,0 О .2 такт

,0 О 0,0 О ,3 такт

О ,0 О О ,0 О . 4 такт 0,0 О а, О О , 5 такт 0,0 О 0,0 0,6 такт 0,0 О 0,0 такт 0,0 О 1,00.

0,0 О 1,1 о

8 такт 9 такт

10 такт и..«

0,0 1 0,1 1

знак ОJ О 1,1 О , П такт

1 ,01 1.1 1 1,00 1,1 О

OJ) 1 О, i 1,

Ag° 000000001 1 00

45 В блоке 6.9 будет зафиксирован положительный знак.

А„- 000000001 1 00

р

Bg-OOUOOOOOOl 01 ,о 0-0,0 о ,1 такт

,0 О 0,0 О,2 такт

,0 О 0,0 О 3 такт

0,00 0,0 О ,4 такт

0,0 О 0,0 О , 5 такт 0,0 О 0,00 , 6 такт О 0,0 О 7 такт О,0 О 0,0 О 8 такт

о о о I о о 9 такт

11 такт - tf. II

0,0 01,1 о, 10 такт

О, О 1 0,11,

знак 0,0 1 1 ,1 0

1 J О 1,1 0

1

AJ- о о о о О о о о о о г 1

В блоке 6.10 также будет зафиксирован /лоложительный знак. АО 000000000011

g 00000000001

о 0,0 о 0 0,0 о , ,0 о 0,0 о, 0. 00 0,0 0 0,0 о 0.0.0 . .0,0 о 0,0 0.

о,о о 0.0 о,

о

1такт

2такт

3такт

4 такт - 5 такт 6 такт

7 такт 0,0 О 0,0 0.. 8 такт 0,0 О 0,0 О, 9 такт

0,0 О 0,0 6. -10ТАКТ , О ,0 О 0,0 О, 11 - такт , 0,0 О 1,00 12 такт

О, О О 1,1 такт знак

0|0 1 О, Д.I такт ,0

,- 000000000000

В блоке 6.11 будет зафиксирован трицательньй знак

А, О о о о О о О О о о о б

00000000001

.00 0,00 ,1 такт

.0 о 0,0 0.2 такт

.0 О 0,0 О,3 такт

0,0 О 0,0 О, 4 такт О, О 0. 0,0 О 5 такт О, О О 0|0 О, б такт О, 00 0,0 О, 7 такт

. ,.1

0,0 О 0.0 О, 8 такт Oij О 0,0 0 9 такт 0.0 О 0,0 0 10 такт О,а О 0,Ь 0 П такт 0,0 О 1,0 О . li так 0,0 О 1,1 О 13 такт 0.0 1 0,1 1 U такт

III I „J ft

знак

«.,

А эОООО о 0000000

1361544 О

В блоке 6.12 будет зафиксирован отрицательньй знак

А 5

Ml

By,.

А.

кт

«.,

000000000000 000000000000

,j-000000000000- знак -

Таким образом, на выходах 24 бло10 ков 6,1...6.12 будет зафиксирован последовательный код:

100111011100 Через каждых п+4 тактов цикл работы блока управления повторяется и,

15 вслед за последовательными кодами первой пары делимого и делителя, через четыре такта поступают последовательные коды следующей пары делимого и делителя.

2Q . Таким образом, при делении в потоковом режиме на предлагаемом устройстве для деления одной пары делимого и делителя требуется 5 п тактов, результат второй пары получает25 ся через п+4 тактов, результат третьей .пары получается через п+4 тактов после получения результата второй и т.д. В общем случае, для деления одной п-разрядной пары делимого и де30 лителя, требуется п+4 тактов.

Формула

Устройство для деления кодов зо-g лотой пропорции, содержащее регистры делимого и делителя, блок управления, причем первый выход блока управления соединен с входом разрешения записи регистра делимого, такто40 вый вход блока управления соединен с входом синхронизации устройства, установочный вход блока управления соединен с входом начальной установки устройства, о тличающееся

45 тем, что, с целью повышения производительности за счет возможности одновременного выполнения операции деления над несколькими парами операндов , в него введены регистр сдвига

50 делимого, регистр сдвига делителя, и п блоков определения значений разрядов частного (где п - разрядность операндов), каждьй из которых содержит вычитатель последовательных кодов золотой пропорции, первый и второй информационные входы которого соединены соответственно с информационными входами первого и второго узлов задержки, первьм и вторым вхоизобретения

11

дами элемента ИЛИ и являются первым и вторым информационными входами, блока, определения значений разрядов частного, синхровход которого соединен с тактовыми входами его первого, второго и третьего узлов задержки и вычитателя, установочный вход блока определения значений разрядов частного соединен с ус танов очнь1ми входа- ми его первого, второго и третьего узлов задержки, вычитателя и триггера, тактовый вход которого соединен с выходом третьего узла задержки, информационный вход которого соеди- нен с выходом элемента ИЛИ, выход первого узла задержки соединен с первым входом коммутатора, второй вход которого соединен с информационным выходом вычитателя, знаковый выход которого соединен с информационным входом триггера, инверсный выход которого соединен с управляющим входом коммутатора, выход которого соединен с первым выходом блока определения значений разрядов частного, второй выход которого соединен с выходом второго узла задержки, а третий выход блока определения значений разрядов частного соединен с инверсным выходом его триггера,причем вход синхр

61544

12

ю15 20 30о25

низации устройства соединен с тактовыми рходами регистров сдвига делимого и делителя и с синхровходами п блоков определения значений разрядов частного, установочные входы которых соединены соответственно с выходами блока управления с второго по (п+1)-й, первый выход которого соединен с входом разрешения записи регистра делителя, а второй вькод блока управления соединен с установочными входами регистров сдвига делимого и делителя, информационные входы которых соединены соответственно с разрядными выходами регистров делимого и делителя, первый и второй информационные входы i-ro блока определения значений разрядов частного соединены соответственно с первым и вторым выходами (i-l)-ro блока определения значений разрядов частного (где ,...,п), первый и второй информационные входы первого блока определения значений разрядов частного соединены соответственно с выходами регистров сдвига делимого и делителя, третьи выходы п блоков определения значений разрядов частного являются разрядными выходами устройства.

Фиг. 2

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных цифровых вычислительных систем. Цель изобретения - повышение производительности за счет возможности одновременного выполнения операции деления над несколькими парами операндов. Устройство для деления кодов золотой пропорции содержит регистры 1, 2 делимого и делителя, регистры 3, 4 сдвига делимого и делителя, блок 5 управления и п блоков 6 определения значений разрядов частот-- ного с соответствующими связями. Каж- дьй из п блоков 6 определения значений разрядов частного содержит первый узел 7 задержки, вычитатель 8, .BTpjjoM узел 9 задержки, элемент ИЛИ 10, коммутатор 11, триггер 12 .и третий узел 13 задержки с соответствующими связями. Устройство вьшолняет операцию деления двух кодов золотой пропорции путем последовательного вычитания двух операндов, поступающих старшими разрядами вперед. 3 ил. i (Л оо 05 сд 4 4; Й/г/

| Устройство для деления | 1978 |

|

SU744564A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-04-29—Подача