(5) ИНТЕРПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Параболический интерполятор | 1981 |

|

SU1018128A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Параболический интерполятор | 1986 |

|

SU1399778A2 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Интерполятор | 1986 |

|

SU1345217A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1124338A1 |

| Линейный интерполятор | 1979 |

|

SU842914A1 |

| Интерполятор | 1973 |

|

SU480094A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ПОЛУТОНОВЫХ ИЗОБРАЖЕНИЙ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ПРИЕМНИКА | 1994 |

|

RU2105355C1 |

| Аналоговый интерполятор | 1988 |

|

SU1536406A1 |

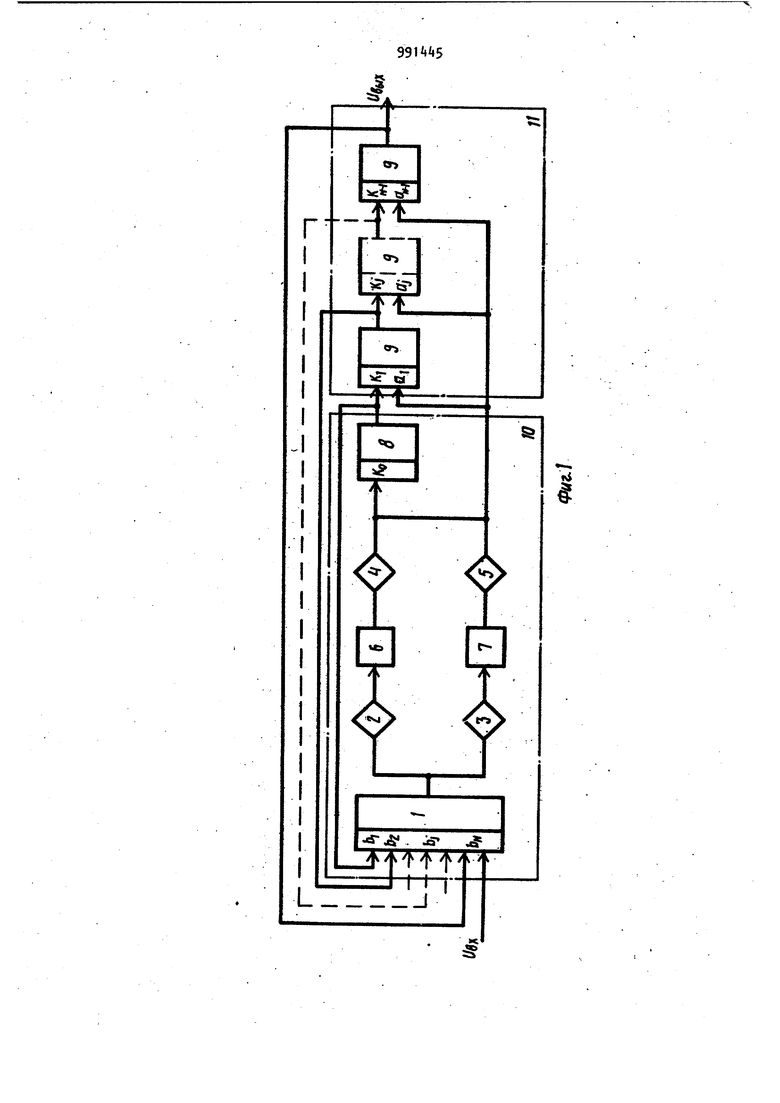

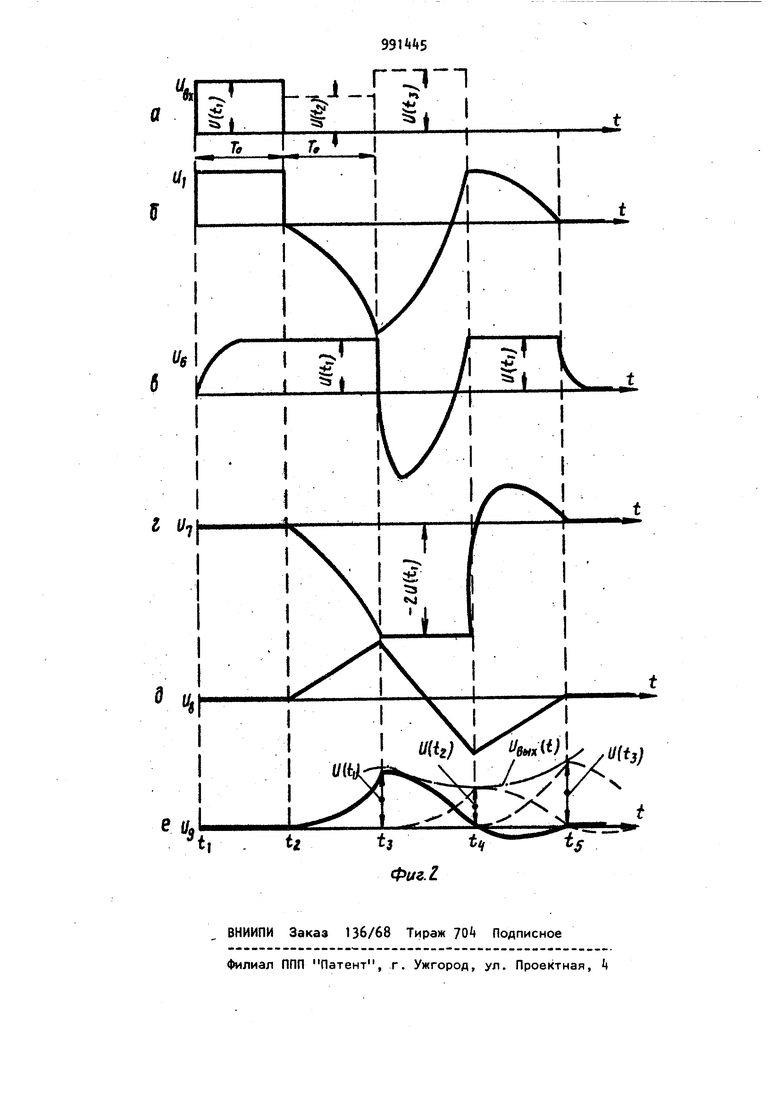

Изобретение относится к преобразо вателям дискретных (по времени) сигналов в непрерывные и может быть использовано в импульсных системах автоматического управления и устройствах обработки дискретных результатов измерений. Известен интерполятор произволь- . ного порядка, использующий отрицательную обратную связь для компенсации на каждом последующем шаге инструментальных ошибок интегрирования, накопленных на предыдущем шаге, содержащий цепочки, каждая из которых выполнена в виде последовательно соединенных сумматора, ключа, аналогового запоминающего устройства и интегратора, а между входами и выходам интеграторов каждой цепочки, кроме . первой, установлены дополнительные ключи t1 . Недостатком этого устройства является наличие погрешности восстановления функции, обусловленной тем, что процесс фиксации приращений накладывается на процесс интегрирования этих приращений. Наиболее близким по технической сущности к изобретению является интерполятор, содержащий блок повьяиения порядка интерполяции, выполненный на (N-l)-M интеграторе, выход каждого из которых соединен с первым входом последующего интегратора, и блок интерполяции первого порядка, состоящий из сумматора и интегратора, выход которого соединен с первым входом сумматора, второй вход сумматора является входом устройства, а выход соединен с входом интегратора блока интерполяции первого порядка через две соединенные параллельно цепочки, каждая из которых состоит из последовательно соединенных первого ключа,, запоминающего элемента и второго ключаС2 . 3 .9 Недостатком этого устройства яаляется его сложность, обусловленная необходимостью использования двух блоков нелинейной интерполяции, двух дополнительнительных сумматоров и двух дополнительных ключей. Целью изобретения является упрощение устройства. Поставленная цель достигается тем что в интерполяторе, содержащем блок повышения порядка интерполяции, выполненный на (N-I)-M интеграторе, вы ход каждого из которых соединен с первым входом последующего интегратора, и блок интерполяции первого порядка, состоящий из сумматора и ин тегратора , выход которого соединен с первым входом сумматора, второй вход сумматора, второй вход сумматора является входом устройства, а выход соединен с входом интегратора блока интерполяции первого порядка через две соединенные параллельно цепочки, каждая из которых состоит из последовательно соединенных первого ключа запоминающего элемента и второго клю ча, сумматор дополнительно содержит (N-1) входов, каждый из которых соединен с выходом соответствующего интегратора блока повышения порядка интерполяции, вторые входы интеграторов блока повышения порядка интерполяции соединены с входом интегратора блока интерполяции первого порядка, а выход (N-l)-ro интегратора блока повышения порядка интерполяции является выходом устройства. На фиг,1 представлена блок-схема устройства; на фиг.2 - графики сигна лов, поясняющие принцип работы интер полятора , Блок-схема устройства содержит сумматор 1, ключи 2-5, запоминающие элементы 6 и 7, интегратор 8 блока интерполяции первого порядка, интеграторы 9 блока повышения порядка инт терполяции, блок 10 интерполяции пер вого порядка, блок 11 повышения порядка интерполяции. Интерполятор работает следующим образом.. Пусть порядок интерполяции , В этом случае блок 11 повышения порядка интерполяции содержит только один интегратор 9, на один вход которого поступает сигнал с выхода интегратора 8. Коэффициент передачи этой цепи К1 должен быть равен 1. На другой ВХОД интегратора 9 поступает сигнал с выходов ключей j и 5 Коэффициент передачи по этой цепи а должен быть равен 0,5, Сигналы обратных связей подается с выходов интеграторов 8 и 9, на входы сумматора 1 с коэффициентами Ъ -1 , Ъ.2.-1, На вход интерполятора в момент времени t с периодом Т, равным постоянной времени интеграторов 8 и 9. поступает ступенчатое напряжение, величина каждой ступени которого соответствует значению интерполируемой функции в указанный момент времени. Работа интерполятора различна для четных и нечетных периодов интерполирования. В нечетные интервалы времени замкнуты ключи 2 и 5 остальные ключи - 3 и - разомкнуты, в четные - наоборот. В нечетные интервалы времени осуществляется запоминание на элементе 6 значения напряжения, поступающего с выхода сумматЬра 1, и интегрирование выходного сигнала запоминающего элемента 7 с целью формирования сигналов обратных связей и выходного сигнала интерполятора, В четные интервалы времени происходит запоминание на элементе 7 значения напряжения, поступающего с выхода сумматора 1, и интегрирование выхбдного сигнала запоминающего элемента 6 с целью формирования сигналов обратных связей и выходного сигнала интерполятора, Таким образом осуществляется разделение во времени процессов запоминания приращений и их интерполирования. Более подробно принцип действия интерполятора поясняет пример формирования его реакции на одиночный импульс. В исходном состоянии выходные на пряжения запоминающих элементов 6 и 7 и интеграторов 8 и 9 равны нулю. При поступлении в момент времени t входного импульса с амплитудой U(t) {фиг.2а) ключи 2 и 5 открываются, а на выходе сумматора 1 появляется импульс прямоугольной формы (фиг,26), На отрезке t, t производится запоминание амплитуды этого импульса в элементе 6 (фиг,2в). Сигналы на выходах интеграторов 8 и 9 не изменяются (фиг,2д и е) потому, что через открытый ключ 5 на входы интеграторов

поступает сигнал нулевой амплитуды (фиг.2г).В момент, времени t амплитуда входного сигнала уменьшается до нуля. Ключи 2 и 5 закрываются, а ключи 3 и i открываются. Через открытый ключ 4 напряжение, амплитуда которого постоянна и равна U(t|), подается с выхода запоминающего элемента 6 иа входы интеграторов 3 и 9. ,

Принимая во внимение, что , К 1, ,5, аналитические выражения сигналов на выходе интеграторов 8 и 9 можно записать в виде

, и CG) для , О) UqCG)0,5(6/T)+0, , (.2)

где (х t,- tf,.

Начиная с момента времени t, на , выходе сумматора 1 формируется сигнал соответствующий инверсной сумме напряжений, которые формируются на интеграторах 8 и 9- Выходное напряжение сумматора на отрезке t, 1,,подается через открытый ключ 3 на вход запоминающего элемента, на выходе которого в момент времени ц фиксируется напряжение с амплитудой -2и(ц ) .

В момент времени t-j, ключи 3 и t закрываются, а ключи 2 и 5 открываются. Через открытый ключ 5 выходное напряжение запоминающего элемента 7, равное -2U(t.), подается на входы интеграторов 8 и 9. Аналитические выражения сигналов на выходах интеграторов на отрезке t, t имеют вид

Ug(()4-2((3/T)MSOiGrsT4 1 Uq(er))(sT 4)

где О t - t/i, .

Выходное напряжение сумматора на отрезке t, t подается через открытый ключ 2 на вход запоминающего элемента 6, на выходе которого в момент времени t.. фиксируется напряжение U(t,). /

При ключи 2 и 5 закрываются, а ключи 3 и if открываются. Через открытый ключ k выходное напряжение запоминающего элемента 6 величиной U(t ) подается на входы интеграторов 8 и 9.

Аналитические выражения для сигналов на выходах интеграторов на отрезке tjj, имеют вид идСа)} , АЛ510 {Г«Т, (5) ид(.6)0,5СС-МТ ;-0,)ДД9 0(, (Ь} гдеа-t - t4.

Выходное напряжение сумматора на отрезке t, 1с1г1одается через открытый ключ 3 на вход запоминающего-элемента 7, на выходе которого в момент времени t фиксируется напряжение, равное ну/1ю.

В момент времени t ключи 3 и М закрываются, а ключи 2 и 5 открываются Через открытый ключ 5 выходное напряжение запоминающего элемента равное нулю, подается на входы интегратр ров 8 и 9. Выходные сигналы интеграторов не изменяются , поэтому напряжения на выходах интеграторов В и 9 и сумматора 1 на отрезке t, t равны нулю. Через открытый ключ 2 выходное напряжение сумматора подается на вхо запоминающего элемента 6 и фиксируется. ;

Таким образом, после момента времени t амплитуда выходных напряже, НИИ запоминающих элементов и интеграторов становится равной нулю, т.е. восстанавливаются нулевые начальные условия.

Если на вход интерполятора поступает ступейчатое напряжение показанное на фиг.2а пунктиром, выходной сигнал интерполятора можно представить ввиде интерполяционного многочлена в форме Лагранжа. Лля произвольного момента времени CW 1 (Г

ЬЫХ ()-0,5 (SSn iy .,(,.,{o.5|-.Oj5.U)

Таким образом, если блок повышени порядка интерполяции содержит один интегратор, интерполятор решает задачу интерполяции входного сигнала многочленом второй степени. В том случае, когда блок повышения порядка интерполяции содержит (N-1) интегратор, устройство осуществляет интерполяцию входного сигнала многочленом степени N.

В процессе преобразования ступенчатого напряжения, поступающего на вход интерполятора, в .непрерывный сигнал, возникает задержка, равная периоду замы,кания ключей 2-5- :

Упрощение интерполятора достигнуто за счет использования одного блока повышения порядка интерполяции вместо двух блоков нелинейной интерполяции. Кроме того, блок повышения порядка интерполяции по сравнению с блоком нелинейной интерполяции, не содержит разрядных ключей, сумматоров, блоков выборки и хранения. Таким образом, данный интерполято позволяет осуществлять интерполюцию сигналов без методической погрешности, причем для его построения требуется меньше злементов. Формула изобретения Интерполятор, содержащий блок повышения, порядка интерполяции, выполненный на (N-I)-OM интеграторе, выхо каждого ид которых соединен с первым входом последующего интегратора, и блок интерполяции первого порядка, состоящий из сумматора и интегратора выход которого соединен с первым вхо дом сумматора, второй вход сумматора является входом устройства, а выход соединен с входом интегратора блока 9 58 интерполяции первого порядка через две соединенные параллельно цепочки, каждая из которых состоит из последовательно соединенных первого ключа, запоминающего элемента и второго ключа, отличающийся тем, что, с целью упрощения конструкции, сумматор дополнительно содержит (N-1) вхо-, доз, каждый из которых соединен с выходом соответствующего интегратора блока повышения порядка интерполяции, вторые входы интеграторов блока повышения порядка интерполяции соединенны с входом интегратора блока интерполяции первого порядка, а выход (N-t) го интегратора блока повышения порядка интерполяции является выходом устройства. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 1Г 8009, кл. G Об К 7/10, 1975. 2.Авторское свидетельство СССР If 765821, кл. G 06 G 7/30, 1980 (прототип).

1

Авторы

Даты

1983-01-23—Публикация

1981-06-12—Подача