Изобретение относится к области вычислительной техники и может быть использовано для воспроизведения функций при вьшоде информации на электронно-лучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных системах. Известно интерполирующее устройст во, содержащее регистр, выход которо го соединен с параллельными цепочками, каждая из которых содержит после довательно соединенные цифроаналоговый преобразователь и интерполятор Ш. Недостатком этого устройства явля ется низкая точность воспроизведения функций, связанная с неточностью работы интерполяторов, с накоплением ошибок интегрирования. Наиболее близким по технической сущности и предлагаемому является линейный интерполятор с двумя аналоговыми запоминакицими устройствами,со держащий регистр, соединенный с параллельными цепочками, в каждой из которых вход цифроаналогового преобразователя соединен с выходом регист ра, а выход соединен с первым входом сумматора, выход которого через ключ соединен со входами аналоговых запоминающих устройств, выходы аналоговых запоминающих устройств через ключи, соединены со входом интегратора; чей выход соединен со вторым входом сумматора. Выход интегратора является выходом цепочки 2. Недостатком устройства является большой объем оборудования. Цель изобретения - сокращение объема оборудования. Наставленная цель достигается тем, что линейный-интерполятор, содержащий последовательно соединенные регистр и цифроаналоговый преобразователь, выход которого подключен ко входам каналов, каждый из которых состоит из сумматора, первый вход которого является входом соответствующего канала, а выход через первый и второй ключи соединен соответственно со входами первого и второго запоминающих блоков, и интегратора,вход которого через третий и четвертый ключи подключен соответственно к выходам первого и второго запоминающих блоков, а выход соединен со вторым входом сумматора, э каждый канал,кроме последнего, введены дополнительные запоминающий блок и ключ, соединенные последовательно и включенные между выходом интегратора и третьим входом сумматора.

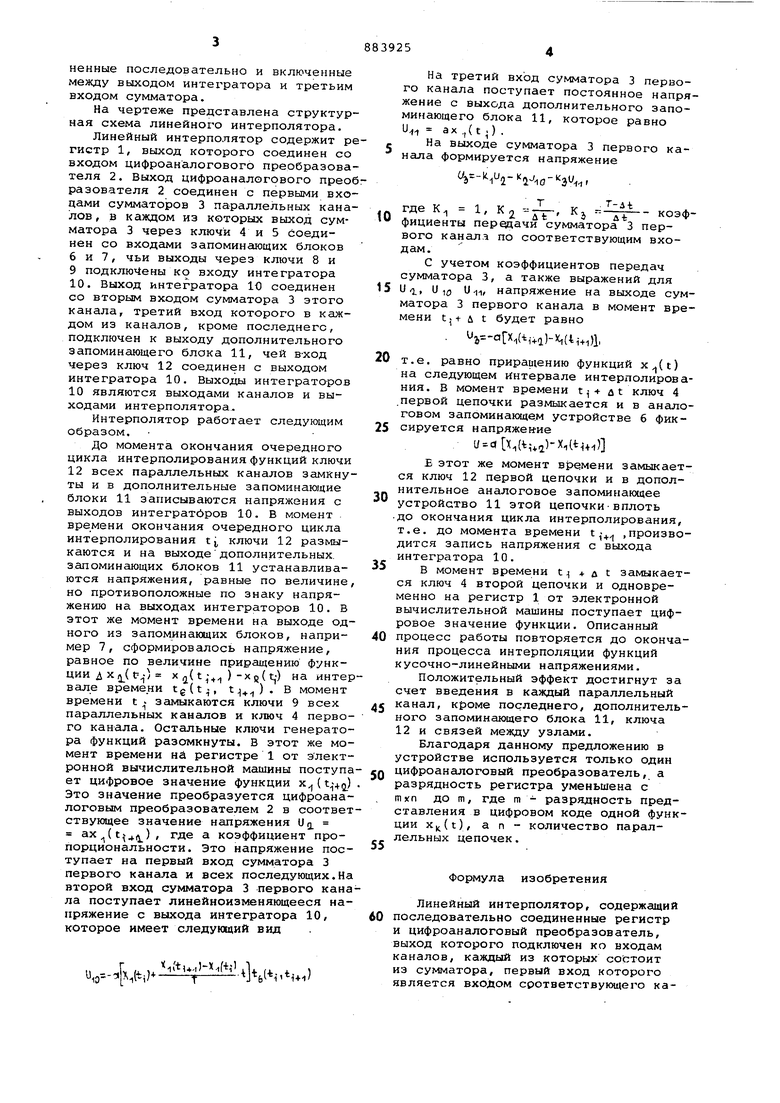

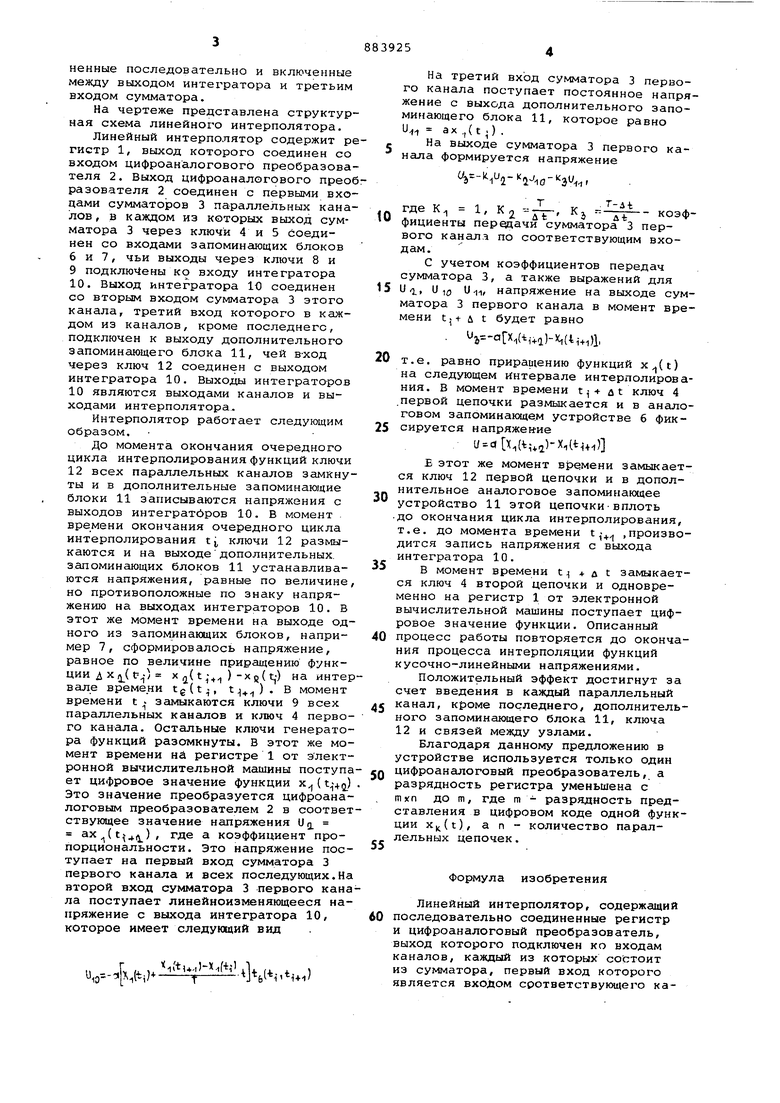

На чертеже представлена структурная схема линейного интерполятора.

Линейный интерполятор содержит регистр 1, выход которого соединен со входом цифроаналогового преобразователя 2. Выход цифроаналогового преоб раэователя 2 соединен с первыми входами сумматоров 3 параллельных каналов , в каждом из которых выход сумматора 3 через ключи 4 и 5 соединен со входами запоминающих блоков 6 и 7, чьи выходы через ключи 8 и

9подключены ко входу интегратора 10. Выход интегратора 10 соединен со вторым входом сумматора 3 этого канала, третий вход которого в каждом из каналов, кроме последнего, подключен к выходу дополнительного запоминающего блока 11, чей в-ход через ключ 12 соединен с выходом интегратора 10. Выходы интеграторов

10являются выходами каналов и выходами интерполятора.

Интерполятор работает следующим образом.

До момента окончания очередного цикла интерполирования функций ключи 12 всех параллельных каналов замкнуты и в дополнительные запоминающие блоки 11 записываются напряжения с выходов интеграторов 10. В момент времени окончания очередного цикла интерполирования tj ключи 12 размыкаются и на выходедополнительных, запоминающих блоков 11 устанавливаются напряжения, равные по величине, но противоположные по знаку напряжению на выходах интеграторов 10. В этот же момент времени на выходе одного из запоминающих блоков, например 7, сформировалось напряжение, равное по величине приращению функции д х,( ) x,j{t,- + )-xg(t,) на интервале времени tg(t,-, t.) . В момент времени t замыкаются ключи 9 всех параллельных каналов и ключ 4 первого канала. Остальные ключи генератора функций разомкнуты. В этот же момент времени на регистре 1 от электронной вычислительной машины поступает цифровое значение функции х(ц+2.) Это значение преобразуется цифроаналоговым преобразователем 2 в соответствующее значение напряжения U ax(t,-), где а коэффициент пропорциональности. Это напряжение поступает на первый вход сумматора 3 первого канала и всех поеледующих.На второй вход сумматора 3 первого канала поступает линейноизменяющееся напряжение с выхода интегратора 10, которое имеет следующий вид

„,,...4.,,.1..ф,,„.,.,)

На третий вход сумматора 3 первого канала поступает постоянное напряжение с выхода дополнительного запоминающего блока 11, которое равно и-,1 ax,,(t,).

с На выходе сумматора 3 первого канала формируется напряжение

(,,

где К, 1, Kj, , Kj ----- коэффициенты передачи сумматора 3 первого канала по соответствующим входам.

С учетом коэффициентов передач сумматора 3, а также выражений для 5 и, и ,(3 и 11, напряжение на выходе сумматора 3 первого канала в момент времени л t будет равно

. ,(i,-,i)-)(,()l,

т.е. равно приращению функций x(t) на следующем интервале интерполирования. В момент времени t -i- д t ключ 4 .первой цепочки размыкается и в аналоговом запоминанием устройстве 6 фиксируется напряжение

U ,(t,4)-Xi(tu-t)

Б этот же момент времени замыкается ключ 12 первой цепочки и в дополнительное аналоговое запоминающее устройство 11 этой цепочки-вплоть до окончания цикла интерполирования, т.е. до момента времени t ,- .производится запись напряжения с выхода интегратора 10.

В момент времени t + д t замыкается ключ 4 второй цепочки и одновременно на регистр 1 от электронной вычислительной машины поступает цифpojBOe значение функции. Описанный процесс работы повторяется до окончания процесса интерполяции функций кусочно-линейными напряжениями.

Положительный эффект достигнут за счет введения в каждый параллельный канал, последнего, дополнительного запоминающего блока 11, ключа 12 и связей между узлами.

Благодаря данному предложению в устройстве используется только один цифроаналоговый преобразователь, а разрядность регистра уменьшена с тип до т, где m - разрядность представления в цифровом коде одной функции x(t), а п - количество параллельных цепочек.

Формула изобретения

Линейный интерполятор, содержащий последовательно соединенные регистр и цифроаналоговый преобразователь, выход которого подключен ко входам каналов, каждый из которых состоит из сумматора, первый вход которого является входом соответствующего канала, а выход через первый и второй ключи соединен соответственно со входами первого и второго запомингиощих блоков, и интегратора, вход которого через третий и четвертый ключи подключен соответственно к выходам первого и второго запоминающих блоков, а выход соединен со вторым входом сумматора, отличающийся тем, что, с целью сокращения объема оборудования, в каждый канал, кроме последнего, введены дополнительно запоминающий блок и ключ, соединенные последовательно и включенные мехзду

выходом интегратора и третьим входом сумматора.

Источники информации, принятые во внимание при экспертизе

1.Коробейников В.Н. Исследование и разработка вопросов преобразования инфс омации в устройствах графического взаимодействия Экспериментатор - малая ЦВМ. Дис. на соиск. уч. степ. канд. тех. наук, Киев, 1973, с. 129-134.

0

2. Авторское свидетельство СССР по заявке 2631141/24, кл. G 06 G 7/26, 1978 (прототип).

и$м

iO

-Ф

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1982 |

|

SU1042038A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Генератор функций | 1980 |

|

SU962995A1 |

| Интерполятор | 1986 |

|

SU1345217A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| Интерполятор | 1981 |

|

SU991445A1 |

| Устройство для программного управления толщиной стенки заготовки | 1982 |

|

SU1074733A1 |

Авторы

Даты

1981-11-23—Публикация

1980-03-03—Подача