11

Изобретение относится к вычислительной технике и может быть использовано для -воспроизведения функций при выводе информации на ЗЛТ, графопостроители и исполнительные механиэ- мы S управляющих вычислительных машинах, а также в качестве программируемого генератора функций или генератора сигналов.

Цель изобретения - повышение точности за счет формирования функций времени с переменным шагом интерполирования.

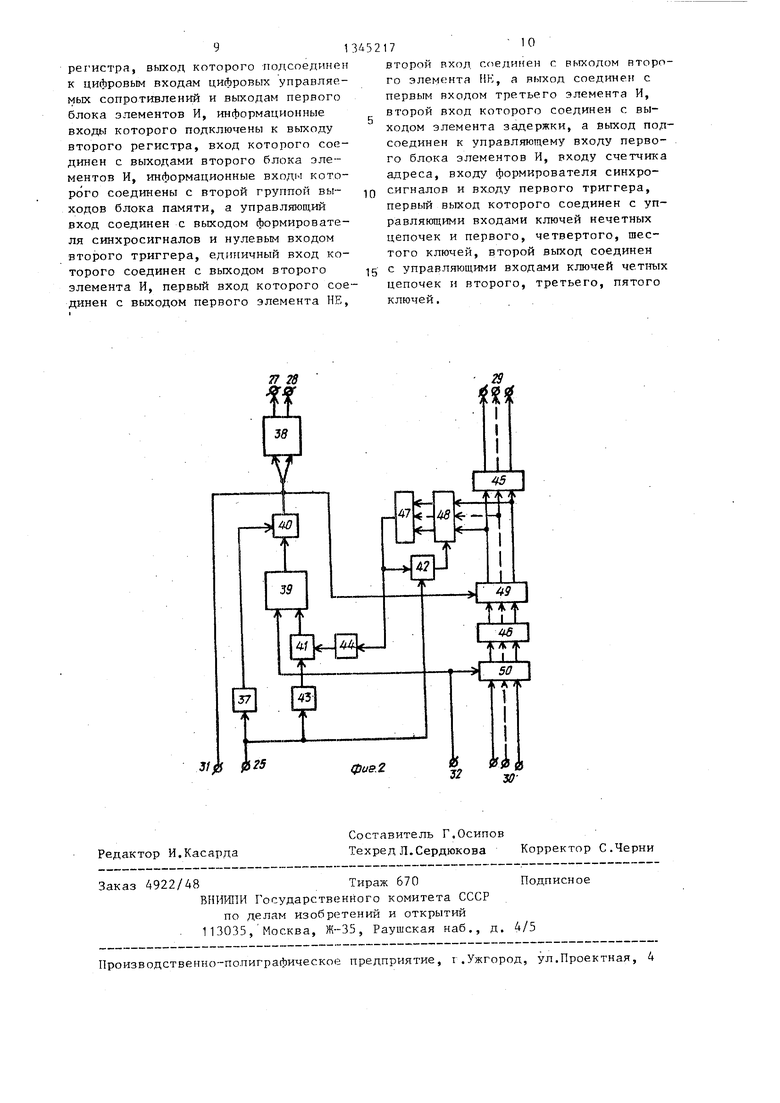

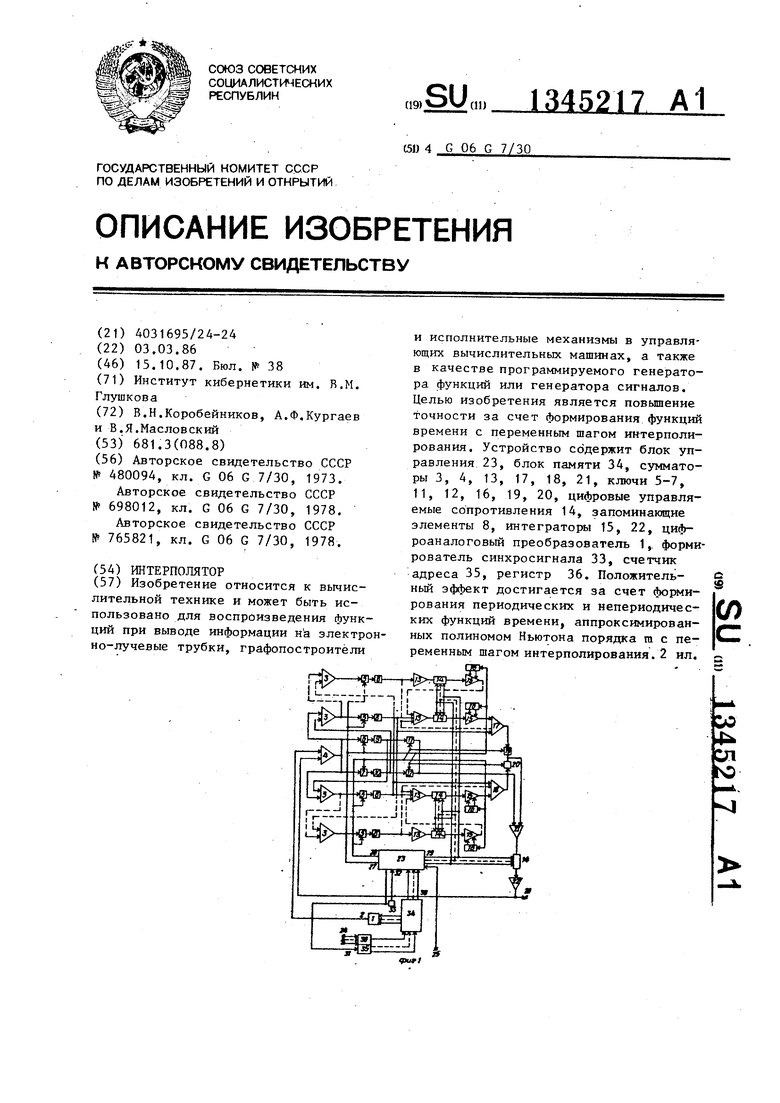

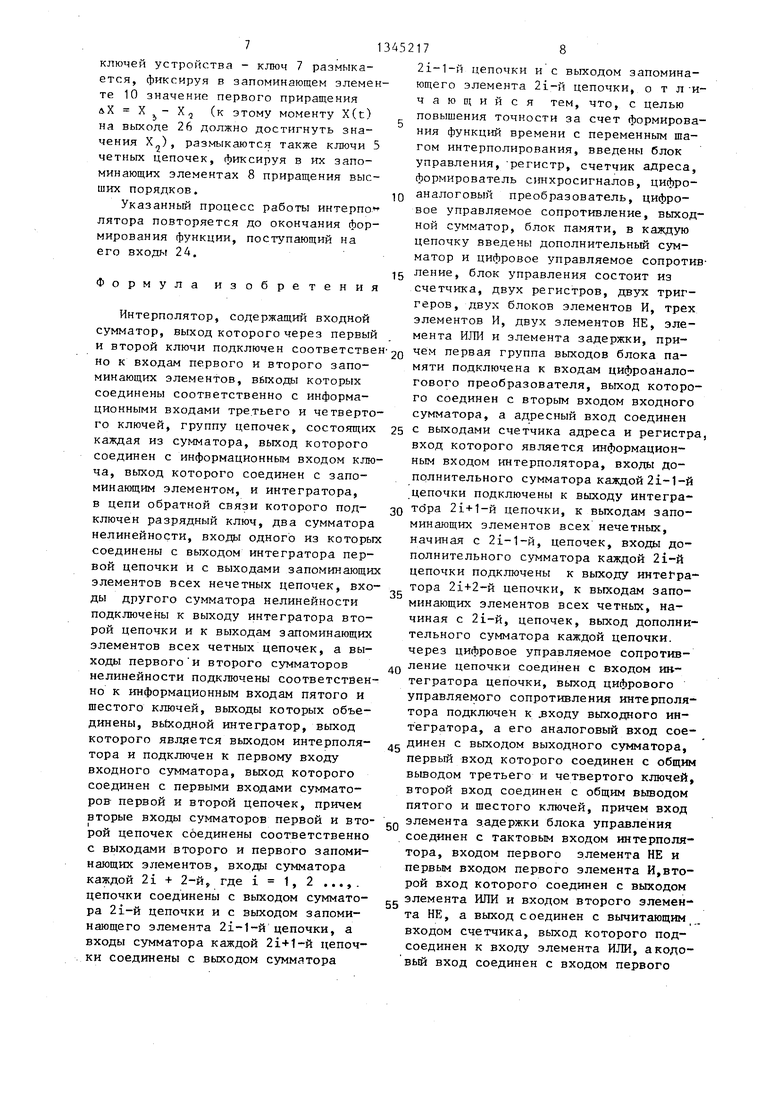

На фиг. 1 показана блок-схема ин- терполятора; на фиг. 2 - блок управ-- .ления.

Интерполятор содержит цифроаналоговый преобразователь 1 с выходом 2, сумматоры 3, входной сумматор 4, клю- чи 5-7, запоминающие элементы 8-10, ключи 11 и 12, дополнительн 1е сумматоры 13, цифровые управляемые сопротивления 14, интеграторы 15, разрядные ключи 16, сумматоры 17 и 18 не- линейности, ключи 19 и 20, выходной сумматор 21, выходной интегратор 22, блок 23 управления, информационные входы 24, тактовый вход 25, выход 26 интерполятора, управляющие выходы 27- 30, вход 31 запроса гтаформации, вход 32 синхросигналов, формирователь 33 синхросигналов, блок 34 памяти, счетчик 35 адреса, регистр 36. I

Блок управления содержит элемент

37 задержки, триггеры 38 и 39, эле менты И 40-42, элементы НЕ 43 и 44, регистры 45 и 46, элемент ИЛИ 47, счетчик 48, блоки элементов И 49 и 50.

Работа-интерполятора основана на формировании периодических и непериодических функций времени, аппроксимированных полиномом Ньютона порядка m с переменным шагом интерполирования представленным в степенной форме

hntri

x(t) x(t.) +II(|-f- (-D Cux x

1 т -

X (

У

0, j k С i (j-1) , , j - k

CJ.,..,, (j-1), k 2, j , 2,

AJX - приращение функции X(t) порядка j 1, m;

,

о 5 о

5

0 5

5

172

X (l:) - значение фу 1кции X(t) , достигнутое на выходе 26 к моменту начала i+1-го (моменту окончания i-ro) шага интерполирования; Т - величина i.-ro шага интер- . полирования, кратная длительности минимального шага Т интерполирсвания.

Интерполятор работает образом.

Информация в виде функции X(t) с входа 24 поступает на регистр 36, в соответствии с которой цифроат алого- вый преобразователь 1 в ответ на каждый сигнал запроса информации, поступающий с выхода 31 блока 23 управления, формирует на выходе 2 ст пенча- тое значение воспроизводимой функции X(t). Сигнал запроса информе1ции с входа 31 поступает на счетный вход счетчика 25 и увеличивает его содержимое на 1.

Новый совместный код счетчика 35 и регистра 36 поступает на входы блока 34 памяти, который формирует на выходах 30 код очередного шагг. интерполирования, а на других выхог;ах - код ступенчатого значения Х-ф нкции Х(г.) 5 которое преобразуется цифроана- логовым преобразователем. Однс1времен- но с этим (с небольшой задерж1 :ой во времени относительно сигнала на входе 31) формирователь 33 формирует на выходе короткий синхросигнал, который поступает в блок 23 упргшления.

Значение X.(t) должно быть достигнуто на выходе 26 интерполятора к моменту окончания следующего тага Т| интерполирования, при условии со. - провождения синхросигналом. Код очередного шага Т - J интерполирования принимается в блок 23 управления, ь значение функции X(t) постуггает на вход сумматора 4, в котором вычисляется разность между этим значе нием и значением функции на выходе 26 интерполятора.

Под действием управляющих сигналов на выходах 27 и 28 управления в течение одного шага интерполирования (например, четного) замкнуты клю-чи 5 и разрядные ключи 16 всех нечетных цепочек (на фиг. 1 - ниже сумматора 4) а также ключи 6, 12 и 20, а разомкнуты ключи 5 и разрядные ключи 6 четных цепочек и ключи 7, 11 и 19. В течение следующего (например, нечетно313

го) шага интерполирования состояния ключей изменяются - ключи 5 и разрядные ключи 16 первой и последуюп1их нечетных цепочек и ключи 6, 12 и 20

разомкнуты, а ключи 5 и разрядные ключи 16 четных цепочек и ключи 7, 11 и 19 - замкнуты.

В четные интервалы времени интеграторы 15 первой и последующих нечет- ных цепочек с помощью ключей 16 устанавливаются в начальное состояние, а их запоминающие элементы 8 ключами 5 подключаются к выходам сумматоров 3. Четные цепочки в четные интервалы времени через сумматор 18 и ключ 20 подключа ются к входу выходного сумматора 21.

Таким образом, в четные интервалы времени происходит подготовка к ра- боте первой и последующих нечетных цепочек - начальная установка их интеграторов 15 и запоминание на элементах 8 значений приращений функции X(t), поступающих с выходов соответ- ствующих сумматоров 3, а четные цепочки в эти периоды времени участвуют в формировании значения функции X(t) на выходе 26. В нечетные интервалы времени происходит подготовка к работе четных цепочек, в то время как первая и последующая нечетные цепочки участвуют в формировании значения функции X(t) на выходе 26.

При этом на выходе сумматора 4 вырабатывается текущее значение разности между ступенчатым значением функции на выходе 2 цифроаналогового преобразователя 1 и значением Аунк- ции X(t) на выходе 26 интерполятора, т.е. первое приращение для следующего шага интеполирования, которое в течение четного интервала времени запоминается в,элементе 9, а в нечетные интервалы времени - в запоминающем элементе 10.

Второе приращение функции X(t) формируется в четные интервалы времени на выходе сумматора 3 первой цепочки и запоминается в элементе 8 этой же цепочки, а в нечетные интервалы времени - формируется на выходе сумматора 3 второй цепочки и запоминается в ее элементе 8.

Аналогично на выходе сумматора 3 |последней нечетной цепочки в четные интервалы времени формируется текущее значение приращения m+1-ro порядка, как разность между текзпцими значения

Q g

5 о

5

5

0

17 .

ми приращения т-го порядка, формируемыми на выходе сумматора 3 предпоследней нечетной цепочки, и значением приращения т-го порядка с выхода элемента 8 предпоследней четной цепочки, запомненным в нем в предыдущем интервале времени.

С выходов сумматора 3 нечетных цепочек приращения функции соответствующего порядка через замкнутые ключи 5 поступают на запоминающие элементы 8 этих же цепочек и в течение четного интервала времени запоминаются в них.

В момент окончания текущего (Т) четного шага интерполирования в запоминающем элементе 9 содержится величина первого приращения AX(tj.,,t/ )« X(t.} - X(t.) функции X(t), а в запоминающих элементах 8 первой и других нечетных цепочек - соответственно второе и йысшие приращения функции X(t)

X(t,,t. ,t,,) uX(t.,t.) - - AX(t,,t..,);

X(t,,t, , ,t .) д X(t-,t- , t-,) (t,. t.,t.p; ...Д-Х.

Текущий шаг интеполирования оканчивается изменением состояний управляющих сигналов на выходах 27 и 28 блока 23 управления, что приводит .к размыканию ранее замкнутых ключей и замыканию разомкнутых и обеспечивает. фиксацию запомненных приращений в соответствующих запоминающих элементах 9 и 8 первой и других нечетных цепочек.

В течение этого же четного шага Т. интерполирования интегратора 15 четных цепочек интегрируют (с постоянной времени., определяемой кодом на выходах 29 блока 23 шага интерполирования) значения приращений функции X(t) , поступакяцих с выходов запоминающих элементов 8 четных цепочек через дополнительные сумматоры 13 и цифровые управляемые сопротивления 14 на входы соответствующих интеграторов 15. С выхода сумматора 18 нелинейная составляющая через открытый ключ 20 поступает на соответствующий вход выходного сумматора 21, где суммируется с первым приращением, и с выхода сумматора 21, умноженная в блоке 14 bia константу, обратную текущему шагу интерполирования, поступает на вход интегратора 22.

51

Во время следующего (нечетного) шага Т.,, интерполирования, в результате переключения всех ключей из замкнутого состояния в разомкнутое и наоборот, функции цепочек изменяются Каждое изменение управляющих сигналов на выходах 27 и 28 сопровождается изменением кода на выходе 29 блока 23 управления, определяющего измене- . ние шага интерполирования. Таким образом, аппроксимация функции X(t) выполняется с переменным шагом в со- . ответствии с интерполяционным полиномом Ньютона.

Блок 23 управления работает следующим образом.

Пусть, например, к моменту прихода на вход 25 очередного тактового сигнала триггер 38 находится в сое- тоянии О на выходе 28 - сигнал управления, поддерживающий разомкнутыми ключи 5 и 16 четных цепочек и ключи 7 , 11 и 19, а на выходе 27 - сигнал управления, поддерживающий замк- нутыми ключи 5 и 16 нечетных цепочек и ключи 6, 12 и 20), счетчик 48 со- держит 1 младшего разряда, в регистре 45 - код текущего шага Т интерполирования, в регистре; 46 - код следующего шага Т интерполирования, а триггер 39 находится в состоянии О - на его единичном выходе,- сигнал, поддержршающий элемент И 40 в закрытом состоянии. К -этому моменту времени в запоминающем элементе 9 и в запоминающих элементах 8 других нечетных цепочек оканчивается запоминание первого (X., - X ,) и высших приращений функции X(t) для последующего шага (первого интерполирования.

Очередной тактовый сигнал с входа 25 поступает на вход элемента И 42, проходит через него (так как на выходе элемента ИЛИ 47 разрешающий сигнал) и поступает на вычитающий вход счетчика 48 - в счетчике 48 устанавливается нулевой код. Нулевой код счетчика 48 устанавливает на выходе элемента ИЛИ 47 логический О, который, пройдя элемент НЕ 44, устанавливает на втором входе элемента И 41 логическую 1. Сразу после окончания тактового сигнала на входе 25 устанавливается логическая 1 и на выходе .элемента НЕ 43 (на первом входе эле- ;мента И 41). В результате элемент И 141 открывается и на единичный вход ,триггера 39 поступает сигнал, уста

5

52

„

5 ,,,

0

5

0

5

,76

навливающий его в 1. Сигнал с выхода элемента задержки 37 и единичное состояние триггера 39 открывают элемент И 40,

Сигнал с его выхода открывает узел элементов И 49, разрешая прие в регистр 45 и счетчик 48 кода следующего шага интерполирования из регистра 46, переводит триггер 38 из кулевого в единичное состояние и поступает на выход 31, являясь сиг :алом запроса информации. Изменение состояния триггера 38 определяется изменением на противоположное состоя:ние управляющих сигналов на выходах 27 и 28, под действием которых все ключи интерполятора изменяют свое состояние.

Сигнал запроса информации с выхода 31 поступает на вход счетчика 35 адреса и вызывает формирование на выходе цифроаналогового преобразователя 1 ступенчатого значения X функции X(t) и на выходах 30 блока 34 памяти - кода следующего шага Т интерполирования, которые сопроЕюждают- ся синхросигналом небольшой длительности (суш;ественной меньшей Т) на входе 32. Синхросигнал с входа 32 блока 23 управления устанавливаем триггер 39 в нулевое состояние и открывает блок элементов И 50, разрешая прием кода шага Т с выходов 30 в регистр 46, В течение оставшейся части шага Т, интерполирования первое приращение лХ .Х - X(t:) запоминается в запоминающем элементе 10, а высшие приращения - в запоминающих элементах 8 четных цепочек,

Следующий тактовьй сигнал с входа 25 проходит через элемент И 42 и, вычитает из кода счетчика 48 1, не вызывая изменения состояний триггеров 38 и 39. Следующий тактовый сигнал с входа 25 проходит через элемент И 42, устанавливает счетчик 48 в нулевое состояние, что после его окончания приводит к установке триггера 39 в единичное состояние. В свою очередь единичное, состояние триггера 39 и задержанный в элементе 37 тактовый сигнал формируют на выходе элемента И 40 сигнал, который открывает блок 49, обеспечивая прием в счетчик 48 и регистр 45 кода шага Т , изменяет состояние триггера 38 и является сигналом запроса информации на входе 31.

Изменение состояния триггера 38 приводит к изменению состояний всех

713452

ключе 11 устройства - ключ 7 размыкается, фиксируя в запоминающем элементе 10 значение первого приращения лХ X - X, (к этому моменту X(t) ня выходе 26 должно достигнуть значения X ), размыкаются также ключи 5 четных цепочек, фиксируя в их запоминающих элементах 8 приращения высших порядков.

Указанный процесс работы интерпо лятора повторяется до окончания формирования функции, поступающий на его входь 24.

Формула изобретения

Интерполятор, содержащий входной сумматор, выход которого через первый и второй ключи подключен соответствен но к входам первого и второго запоминающих элементов, вбгходы которых соединены соответственно с информационными входами третьего и четвертого ключей, группу цепочек, состоящих каждая из сумматора, выход которого соединен с информационным входом ключа, выход которого соединен с запоминающим элементом, и интегратора, в цепи обратной связи которого под- ключен разрядный ключ, два сумматора нелинейности, входы одного из которых соединены с выходом интегратора первой цепочки и с выходами запоминающих элементов всех нечетных цепочек, входы другого сумматора нелинейности подключены к выходу интегратора второй цепочки и к выходам запоминающих элементов всех четных цепочек, а выходы первого и второго сумматоров нелинейности подключены соответственно к информационным входам пятого и шестого ключей, выходы которых объединены, вь1ходной интегратор, выход которого является выходом интерполя- тора и подключен к первому входу входного сумматора, выход которого соединен с первыми входами сумматоров первой и второй цепочек, причем вторые входы сумматоров первой и вто- рой цепочек соединены соответственно с выходами второго и первого запоминающих элементов, входы сумматора каждой 21 + 2-й, где i 1, 2 ...,. цепочки соединены с выходом суммато- pa 21-й цепочки и с выходом запоминающего элемента 21-1-й цепочки, а входы сумматора каждой 21+1-й цепочки соединены с выходом сумматора

Q

5

35

Q 5 о Q g gp gg

178

2i-1-H цепочки и с выходом запоминающего элемента 21-й цепочки, о т л И- ч а ю D; и и с я тем, что, с целью повышения точности за счет формирования функций времени с переменным шагом интерполирования, введены блок управления, -регистр, счетчик адреса, формирователь синхросигналов, цифро- аналоговый преобразователь, цифровое управляемое сопротивление, выходной сумматор, блок памяти, в каждую цепочку введены дополнительный сумматор и цифровое управляемое сопротивление, блок управления состоит из счетчика, двух регистров, двух триггеров, двух блоков элементов И, трех элементов И, двух элементов НЕ, элемента ИЛИ и элемента задержки, причем первая группа выходов блока памяти подключена к входам цифроанало- гового преобразователя, выход которого соединен с вторым входом входного сумматора, а адресный вход соединен с выходами счетчика адреса и регистра, вход которого является информационным входом интерполятора, входы дополнительного сумматора каждой 21-1-й цепочки подключены к выходу интегра- то ра 21+1-й цепочки, к выходам запоминающих элементов всех нечетных, начиная с 21-1-й, цепочек, входы дополнительного сумматора каждой 21-й цепочки подключены к выходу интегратора 21+2-й цепочки, к выходам запоминающих элементов всех четных, начиная с 21-й, цепочек, выход дополнительного сумматора каждой цепочки, через цифровое управляемое сопротивление цепочки соединен с входом интегратора цепочки, выход цифрового управляемого сопротивления интерполятора подключен к ходу выходного интегратора, а его аналоговый вход соединен с выходом выходного сумматора, первый вход которого соединен с общим выводом третьего и четвертого ключей, второй вход соединен с общим выводом пятого и шестого ключей, причем вход элемента з.адержки блока управления соединен с тактовым входом интерполятора, входом первого элемента НЕ и первым входом первого элемента И,второй вход которого соединен с выходом элемента ИЛИ и входом второго элемента НЕ, а выход соединен с вычитающим входом счетчика, выход которого подсоединен к входу элемента ИЛИ, а кодовый вход соединен с входом первого

9П

регистра, выход которого подсоединен к цифровым входам цифровых управляемых сопротивлений и выходам первого блока элементов И, информационные входы которого подключены к выходу второго регистра, вход которого соединен с выходами второго блока элементов И, информационные входы которого соединены с второй группой вы-

ходов блока памяти, а управляющий вход соединен с выходом формирователя синхросигналов и нулевым входом второго триггера, единичный вход которого Соединен с выходом второго элемента И, первый вход которого соединен с выходом первого элемента ИЕ,

7f 28

Редактор И.Касарда

Заказ 4922/48Тираж 670Подписное

ВННШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

17-10

второй вход соединен с выходом второго элемента ИК, а выход соединен с первым входом третьего элемента И, второй вход которого соединен с выходом элемента задержки, а выход подсоединен к управляющему входу первого блока элементов И, входу счетчика адреса, входу формирователя синхросигналов и вх.оду первого триггера, первый выход которого соединен с уп- равля ощими входами ключей нечетных цепочек и первого, четвертого, шестого ключей, второй выход соединен с управляющими входами ключей четных цепочек и второго, третьего, пятого ключей.

29

Составитель Г.Осипов

Техред Л.СердюковаКорректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Линейный интерполятор | 1982 |

|

SU1042038A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Генератор функций | 1980 |

|

SU962995A1 |

| Интерполятор | 1981 |

|

SU1061157A2 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| Интерполятор | 1981 |

|

SU991445A1 |

| Линейный интерполятор | 1980 |

|

SU883925A1 |

Изобретение относится к вычислительной технике и может быть использовано для воспроизведения функций при вьшоде информации н а электронно-лучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных машинах, а также в качестве программируемого генератора функций или генератора сигналов. Целью изобретения является повышение точности за счет формирования функций времени с переменным шагом интерполирования. Устройство содержит блок управления 23, блок памяти 34, сумматоры 3, 4, 13, 17, 18, 21, ключи 5-7, 11, 12, 16, 19, 20, цифровые управляемые сопротивления 14, запоминающие элементы 8, интеграторы 15, 22, циф- роаналоговый преобразователь 1,. формирователь синхросигнала 33, счетчик адреса 35, регистр 36. Положительный эффект достигается за счет формирования периодических и непериодических функций времени, аппроксимированных полиномом Ньютона порядка m с переменным шагом интерполирования. 2 ил. Q (Л

| Интерполятор | 1973 |

|

SU480094A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1986-03-03—Подача