Изобретение относится к вычислительноП технике и может быть использовано для воспроизведения функций при выводе информации на электроннолучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных системах.

Предлагаемый линейный интерполятор служит для вопроизведения функций вида

х ) х Х2 (t)

(1)

х x(t)

где параметром t является время.

Известен линейный интерполятор, содержащий регистр, выход которого соединен с параллельными цепочками, каждая из которых содержит последовательно соединенные цифроаналоговы преобразователь, сумматор,, ifлюч, запоминающий блок и интегратор, выход которого подключен ко второму входу сумматора, выход интегратора является выходом цепочки, а выходы цепочек - являются выходами устройст ва 1 .

Погрешность интерполирования в данном интерполяторе вызвана тем, что процесс запоминания приращения функций в запоминающих блоках происходит одновременно с процессом интегрирования этих приращений интеграторами.

Известен также линейный интерполятор, использующий два запоминающих блока благодаря разделению во времени процессов записи информации в запоминающий блок и интегрирования. Устройство содержит регистр, соединенный с параллельными цепочками, в каждой из которых вход цифроаналогового преобразователя соединен с выходом регистра, а выход соединен с первым входом сумматора, выход которого через ключи поключен ко входам двух запоминающих блоков, чьи выходы через другие ключи соединены со входом интегратора, выход которого является одним из выходов устройства и подключен к второму входу сумматора 2 .

Недостатками устройства являются большая разрядность регистра,которая равна произведению тразрядность представления ординат одной из функций (1), а/п- количество функций (1); большое число , (п) цифроаналоговых преобразовате- леП, так как в каждой из цепочек должен быть отдельный цифроаналоговый преобразователь; узкий класс воспроизводимых функций, ограниг енный реализацией восстановления функций времени с постоянным шаТом интерполирования, и высокие затраты оборудования памяти электронной вычислительной машины, вызванные необходимостью хранить в памяти машины и выдавать через равные промежутки времени на вход устройства значения функции, вне зависимости от поведения функции на итервале интерполирования.

Наиболее близким по технической сущности к предложенног у является лнейный интерполятор, содержащий регистр, выход которого соединен со входом цифроаналогового преобразователя. Выход последнего соединен с первыми входами сумматора параллельных каналов, в каждом из которых выход сумматора через ключи сединен со входами запоминающих, блоков , чьи выходы через ключи подключены ко входу интегратора. Выход интегратора соединен с третьим входом сумматора этого канала, второй вход которого в каждом из ка-налов подключен .к выходу запоминаю,щего блока, чей вход через ключ соединен с выходом интегратора. Выходы интегратора являются выходами каналов и выходами линейного интерполятора 3 .

Недостатки прототипа заключаются в узосг;ч готасса воспроизводимых функций, ограниченного реализацией восстановления функций времени с постоянным шагом инсерполирования,

,е;пь изобретения - расширение класса воспроизводимых функций

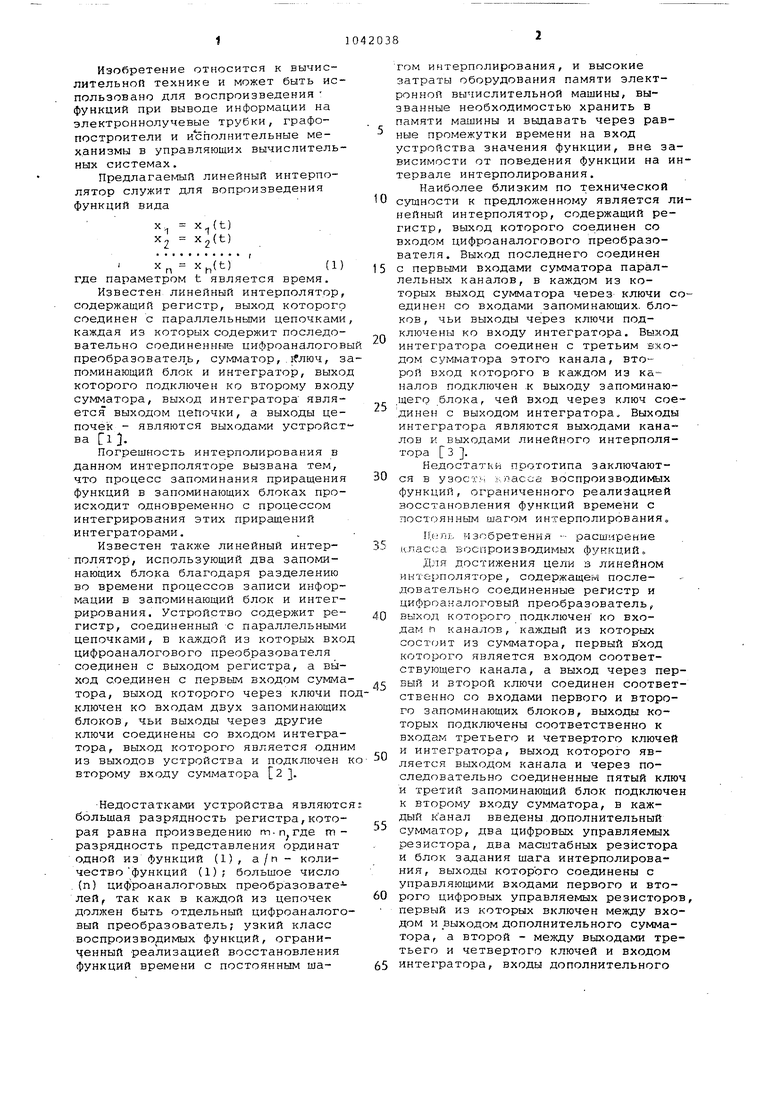

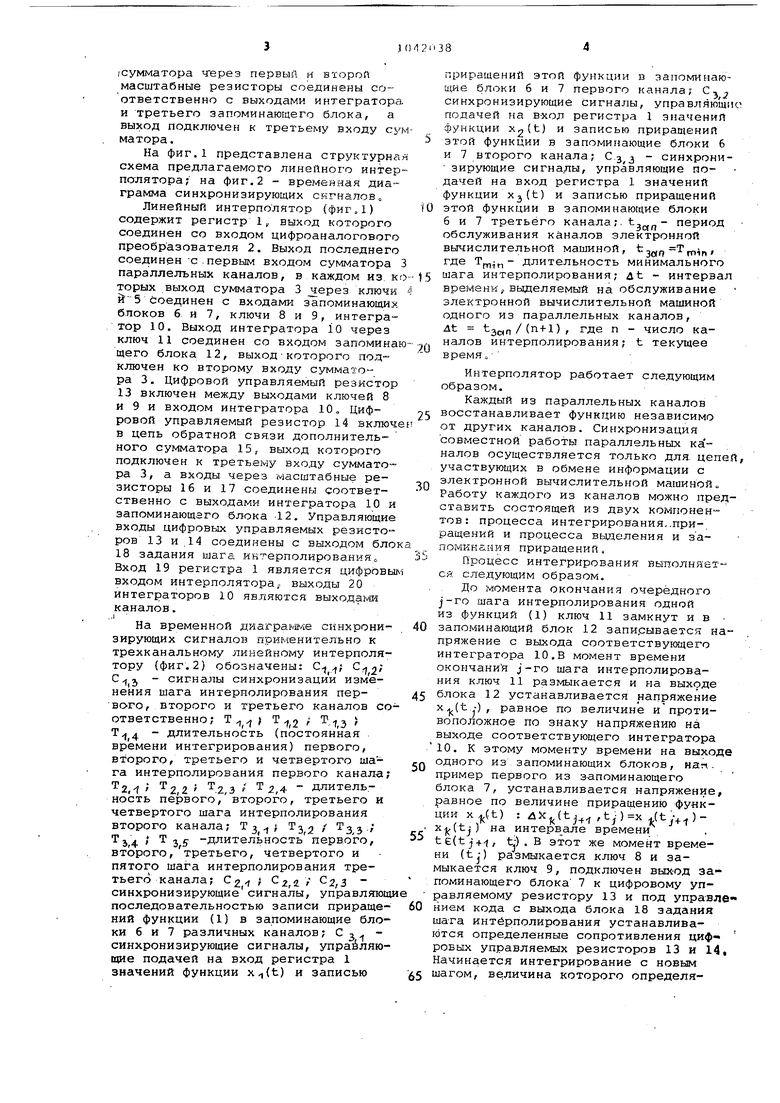

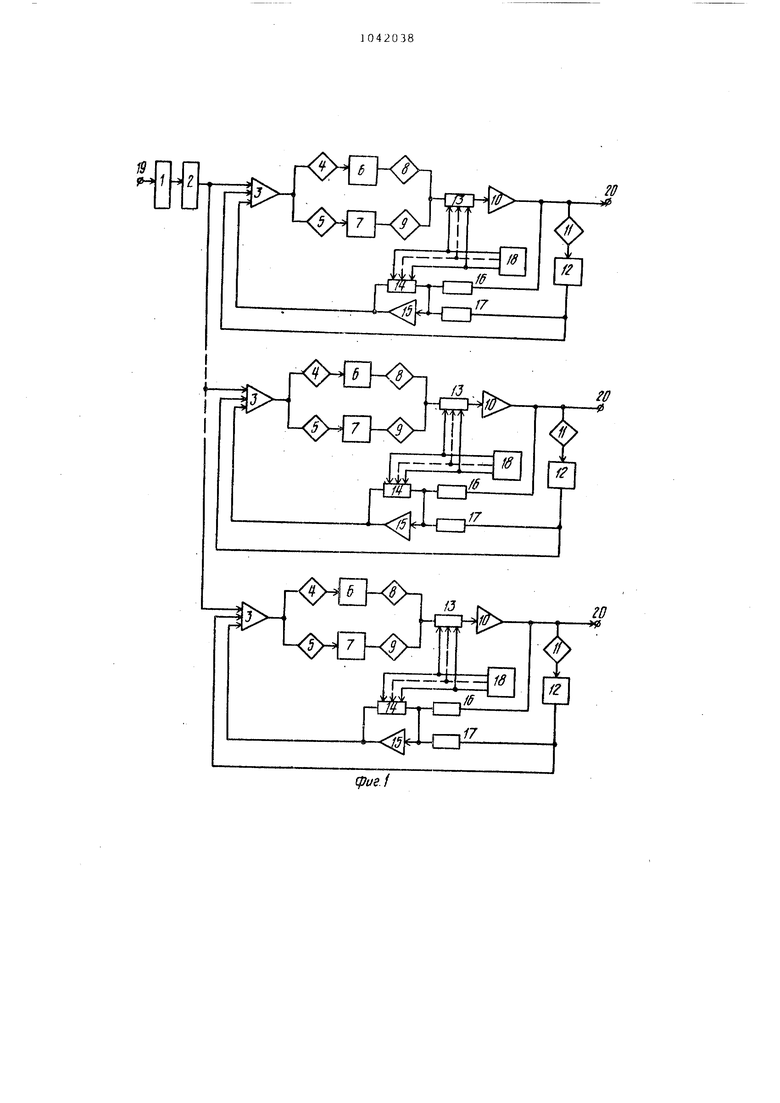

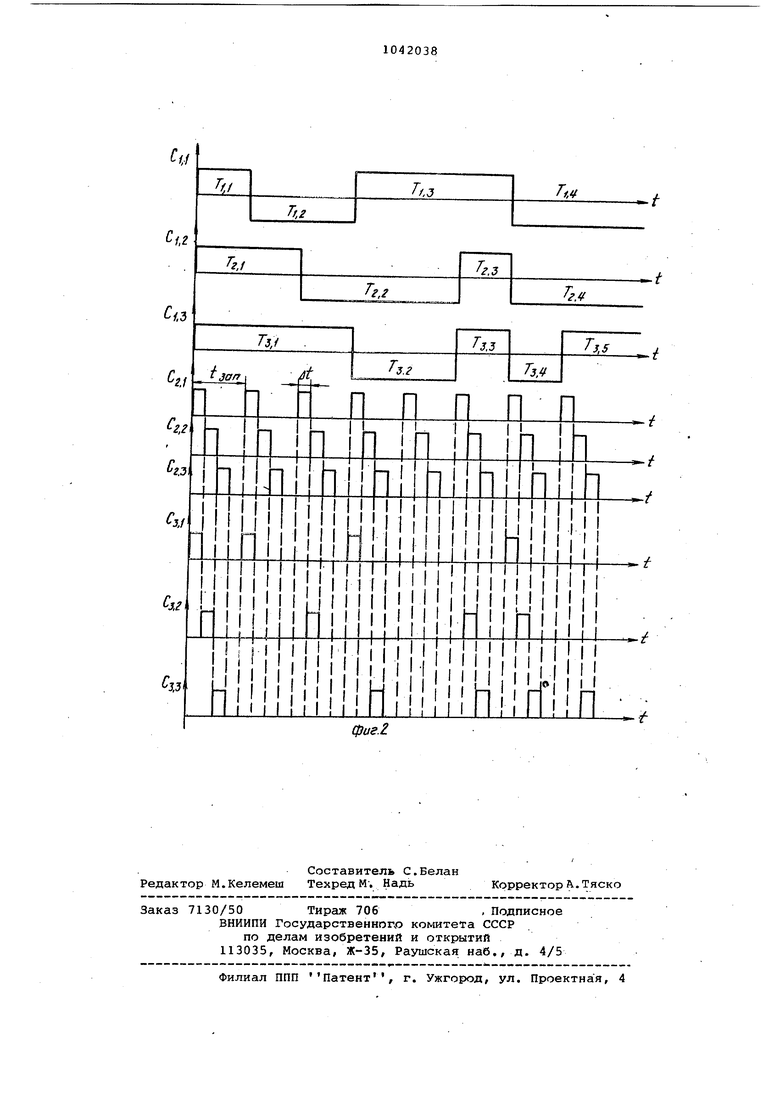

Для достижения цели з линейном интерполяторе, содержащеы1 последовательно соединенные регистр и цифроаналоговый преобразователь, выход которого подключен ко входам п каналов, каждый из которых состоит из сумматора, первый вход которого является входом соответствующего канала, а выход через первый и второй ключи соединен соответственно со входами первого и второго запоминающих блоков, выходы которых подключены соответственно к входам третьего и четвертого ключей и интегратора, выход которого является выходом канала и через последовательно соединенные пятый клю и третий запоминающий блок подключе к второму входу сумматора, в каждый канал введены дополнительный сумматор, два цифровых управляемых резистора, два масштабных резистора и блок задания шага интерполирования, выходы которого соединены с управляющими входами первого и второго цифровых управляемых резисторо первый из которых включен между входом и выходом дополнительного сумматора, а второй - между выходами третьего и четвертого ключей и входом интегратора, входы дополнительного (Сумматора через первый и второй масштабные резисторы соединены соответственно с выходами интегратор и третьего запоминающего блока, а выход подключен к третьему входу с матора. На фиг.1 представлена структурн схема предлагаемого линейного интер полятора; на фиг.2 - временная диа грамма синхронизирующих сигналов о Линейный интерполятор (фигЛ) содержит регистр 1, выход которого соединен со входом цифроаналогового преобразователя 2. Выход последнего соединен с.первым входом сумматора параллельных каналов, в каждом из к торых выход сумматора 3 через ключи соединен с входами запоминающих блоков б и 7, ключи 8 и 9, интегратор 10. Выход интегратора 10 через ключ 11 соединен со входом запомина щего блока 12, выходкоторого подключен ко второму входу сумматора 3. Цифровой управляемый резистор 13 включен между выходами ключей 8 и 9 и входом интегратора 10 , Цифровой управляемый резистор 14 включ в цепь обратной связи дополнительного сумматора 15, выход которого подключен к третьему входу сумматора 3, а входы через масштабные резисторы 16 и 17 соединенр соответственно с выходами интегратора 10 и запоминающего блока 12. Управляющие входы цифровых управляемых резисторов 13 и 14 соединены с выходом бло 18 задания шага интерполирования Вход 19 регистра 1 является цифровы входом интерполятора,- выходы 20 интеграторов 10 являются выходами каналов. На временной диаграмме синхронизирующих сигналов применительно к трехканальному линейному интерполятору (фиг. 2) обозначеныг , - сигналы синхронизации изменения шага интерполирования первого, второго и третьего каналов со ответственно; Т 1,2 ,3 Т 4 длительность (постоянная времени интегрирования) первого, второго, третьего и четвертого шага интерполирования первого канала; .l ,2 ,3 ,4 - длительность первого, второго, третьего и четвертого шага интерполирования второго канала; Т з,-j ; ,2 3,3 Tj4 Т 3 5 -длительность перв.ого, второго,третьего, четвертого и пятого шага интерполирования третьего канала; С2-J / С 2,2 V С2,3 синхронизирующиесигналы, управляющ последовательностью записи приращеНИИ функции (1) в запоминающие блоки 6 и 7 различных каналов; С -( синхронизирующие сигналы, управляющие подачей на вход регистра 1 значений функции x(t) и записью приращений этой функции в запоминающие блоки 6 и 7 первого канала; С синхронизирующие сигналы, управляющие подачей на в-ход регистра 1 значений функции Xglt) и записью приращений этой функции в запоминающие блоки 6 и 7 второго канала; €3,3 - синхронизирующие сигналы, управляющие подачей на вход регистра 1 значений функции XjCt) и записью приращений этой функции в запоминающие блоки б и 7 третьего канала;, период обслуживания каналов электронной вычислительной машиной, , где длительность минимального шага интерполирования; At - интервал времени,выделяемый на обслуживание электронной вычислительной машиной одного из параллельных каналов, At t3c(n/(i + l)/ где п - число каналов интерполирования; t текущее время о Интерполятор работает следующим образом. Каждый из параллельных каналов восстанавливает функцию независимо от других каналов. Синхронизация совместной работы параллельных каналов осуществляется только для. цепей, участвующих в обмене информации с электронной вычислительной машиной. Работу каждого из каналов можно пре;;ставить состоящей из двух компонентов : процесса интегрирования,.при-, ращений и процесса выделения и запоминания приращений. Процесс интегрирования выполняется следующим образом. До .момента окончания очерёдного j-ro шага интерполирования одной из функций (1) ключ 11 замкнут и в запоминающий блок 12 записывается напряжение с выхода соответствукндего интегратора 10.В момент времени окончания j-ro шага интерполирования ключ 11 размыкается и на выходе блока 12 устанавливается напряжение x(t-), равное по величине и противоположное по знаку напряжению на выходе соответствующего интегратора 10. К этому моменту времени на выходе одного из,запоминающих блоков, нал. пример первого из запоминающего блока 7, устанавливается напряжение, равное по величине приращению функ/SX(t j ,ty ) х t,(ty+ ) x(tj) на интервале времени te(t J+-J, t;) . В этот же момент времени () размыкается ключ 8 и замыкается ключ 9, подключен выход эапоминающего блока 7 к цифровому управляемому резистору 13 и под управлением кода с выхода блока 18 задания шага интерполирования устанавливаются определенные сопротивления цифровых управляемых резисторов 13 и 14, Начинается интегрирование с новым шагом, величина которого определяется установленным значением сопротивления соответствующегоцифров управляемого резистора 13. После окончания этого шага интерполирования ключи 9 и 11 размыкаются, замыкается ключ 8 и устанавливаются н вые значения сопротивлений цифровых управляемых резисторов 13 и 14. Выделениа и запоминание в запоминающих блоках б или 7 приращений функций выполняется следующим обраэом. Параллельные каналы обслуживаются электронной вычислительной машиной циклически с периодом, равным Зо1п таким образом, что первый канал обслуживается в течение интерва ла времени AtJ, второй - At, третий - At , и т.д. , д t At2-At-. . . д Эти интервалы следуют последователь но один за другим. Причем к-тый канал обслуживается электронной вычис лительной машиной только в-том слу чае, если в момент начала очередног периода , произошло изменение в этрм канале предыдущего шага интерполирования, Если же предыдущий шаг интерполирования для канала не окончился, а продолжается на текущи период tj,, то соответствующий интервал времени ut выдерживается без использования. В случае необходимости обслуживания k-ro канала в течение времени /at осуществляется вьодача из электронной вычислител ной машины цифрового кода очередного значения восстанавливаемой функции x(ty+2)p причем этого значения в регистр 1, преобразование его в соответствующее значение напряжения на выходе цифроаналогового преобразователя 2,вычисление приращения ДХл, на выходе сумматора 3 и запись запоминающий блок б или 7 k-ro кана ла. Причем приращения лX функции. x(t) для {j+2)-ro шага интерполирования вычисляются и запоминаются в начале (j+l)-ro шага интерполиров ния. Вычисление приращения x.( ty) выполняется на интервале времени teCtj+ {k-l)ЛЬ; в соот ствии с формулой /Vz-V-I WV jf )T ) ( где X, ( ) - напряжение, сохраняемое на выходе цифроаналогового преобразователя 2 в течение интерва ла времени ut, т.е. t (k-l)dt; tj+k4tj, и соответствующее значению функции x.(t), которое должно быть достигнуто на выходе 20 k-ro канала в момент времени t 2 t j+T ,т.е. к моменту окончания (j+2) шага интерполирования; л N ( t , , tj ) х (tj+ ) -X (tj ) напряжение, соответствующее приращеию функции Xj,(t) на интервале вреени t; 4--1 / t.j J, и записанное в один з запоминающих блоков 6 или 7, наприер в блок 7, k-ro канала в начале |-го шага интерполирования.. Это -значение хранится в соответствующем запоминающем блоке 7 до окончания (j + D-ro шага интерполирования,, длительность которого равна Т x(ty) - напряжение, достигнутое а выходе 20 k-ro канала в момент времени tj и записанное в запоминающий блок 12 обратной связи в конце i-ro шага интерполирования; Т ; - длительность (J + 1)-го шага и1 терполирования k-ro канала. Формирование и запоминание в одном из запоминающих блоков 6 или 7 приращений функции (1) выполняется в следующей последовательности. В течение времени от начала (j+l)-ro шага интерполирования до момента окончания обслуживания преД1адущего (k-l)-ro канала, т.е. на .интервале t tj , t j+ (k-1 )4t J , . в k-TOM канале замкнут только ключ, обеспечивающий , подачу на вход интегратора 10 этого канала напряжения, соответствующего приращению функции X на {j+l)-M интервале интерполирования, т.е. -, t +Т|, , Пусть, например, значение J 4х ,j(ty ,tj) хранится в первом запоминающем блоке 7, тогда на интервале ,tj+(krl)4t замкнут только ключ 9, остальные ключи 4,5,8 и 11 этого канала разомкнуты.. В момент времени t t- + (k-l) за ъжaeтcя на время t ключ 4.1k-го канала и одновременно на вход 19 регистра1 из электронной вычислительной машины поступает цифровой код значения функции xAt:.). С выхода цифроаналогового преобразователя 2 соответствующее згначение аналогового напряжения поступает на первый вход сумматора 3 канала, ка второй его вход подается с выхода запоминающего блока 12 напряжение, обратное по знаку и пропорциональное значению x.(t ), а на третий вход - с выхода сумматора 15 обратной связи напряжение, обратное по знаку и пропорциональное разности напряжений на выходах интегратора 10 и запоминающего блока 12, т.е. значение и 15 1 10 2 12 где и напряжение на выходе интегратора 10, пропорциональное -значению S V K SviSнапряжение на выходе запоминающего блоки 12, обратное по знаку и проп циональное величине x(t); - коэффициент передачи нап а, и aj жений по первому и второ входам сумматора 15, их значения определяются от ношением сопротивлений: устанавливаются равными а а - . Jt Величины т постоянны и должны быть пропорциональны значению , т.е. 4t, а R - переменно R Ь Т , его значение определяется величиной те кущего шага интерполирования. Напряжение, вычисленное в соответстВИИ с выражением (2, с выхода сум матора 3 через открытый ключ 4 подается на вход второго запоминающего блока бив течение интервала времени dt, т.е„ за время +(k-l)dt, tj+kAt, запоминается в /этом блоке. После окончания интервала времени ЛЬ размыкается ключ. замыкается ключ 11 k-ro канала и начинается обслуживание (k+l)-ro к нала. После того, как закончится в k-TOM канале (j+l)-fl шаг интерполи рования, на выходе блока 18 изменя ся цифровой код и устанавливается значение сопротивления цифрового управляемого резистора 13, определяющее величину (j+2)-ro шага интерполирования, т.е. Т и значение сопротивления цифрового управляемого резистора 14 . определяющего значения коэффициентов передач aj, и а А сумматора 15, Одновр менно с этим ключи 9 и 11 размыкаются, замыкается ключ 8, подключающий выход второго запоминающег. блока б через цифровой управляе резистор 13 ко входу интегратора 1 Спустя время, равное (k-l)4t от момента следующего изменения шага интерполирования в k-том канале, н регистр 1 поступает цифровой код очередной ординаты ) функции х и включается ключ 5, подключая вход первого запоминающего блока 7 квыходу сумматора 3. В течение последующего ина:ервала времени ut в запоминающем блоке 7 за- , поминается приращение х(Ьд /t j), сформированное, на выходе сумматора 3. В момент времени 4t ключ 5 в k-TOM канале размыкается и замыкается ключ 11. Блоки 18 задания шага интерполирования могут быть реализованы как автономные (с ручным или программным управлением), так и неавтономные. В последнем случае они могут представлять собой два последовательно соединенных регистра, входы одного из которых подключены к выходам электронной вычислительной машины,, а выходы другого - к управляющим входам цифровых управляемых резисторов 13, и 14. Величина очередного шага интерполирования Т устанавливается в соответствиис цифровым кодом на выходах блока 18 управления шагом интерполирования k-ro канала в момент окончания предыдущего ( у+1)-го шага. При неавтономном исполнении .блоков 18 цифровой код значения оче(редного (j+2)-ro шага интерполирования выдается из электронной вычислительной машины, одновременно с выдачей значения ординаты x(tj4.2) и запоминается до окончания ( j +1)-го шага интерполирования на входном регистре блока 18, после чего передается на его выходной регистр. Описанный . процесс работы линейного интерполятора с переменным шагом, интерполирования повторяется до окончания вывода восстанавливаемых функций (1). Класс воспроизводимых функций интерполятора расширяется за счет реализации переменного шага интерполирования, причем одновременно сокращается объем оборудования памяти электронной вычислительной машины, требуемый для восстановления функций времениГс заданной точностью. Согласно фиг.2 для трехканального линейного интерполятора с переменным шагом интерполирования требуется примерно вдвое () меньf 4 . ее оборудование памяти электронной вычислительной машины, чем для такого же интерполятора с постоян-; ным шагом интерполирования.

ei

19

1

М

ЕН

20 Гг I

/

-Щ}

/7 -CD

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Интерполятор | 1986 |

|

SU1345217A1 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Линейный интерполятор | 1980 |

|

SU883925A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

| Генератор функций | 1980 |

|

SU962995A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Интерполятор | 1981 |

|

SU991445A1 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| Интерполятор | 1983 |

|

SU1142848A1 |

ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР, содержащий последовательно соединенные регистр и цифроаналоговый преобразователь, выход которого подключен ко входам ц каналов, каждый из которых состоит из сумматора, первый вход которого является входом соответствующего канала, а выход через первый и второй ключи соединен соответственно со входами первого и второго запоминающих блоков, выходы которых подключены соответств.енно к входам третьего и четвертого ключей и интегратора, выход которого является выходом канала и через последовательно соединённые пятый ключ -и третий запомингиотий блок подключен ко второму входу сумматора, отличающийся тем, что, с целью расширения класса воспроизводимых функций, в kaждый из каналов введены дополнительный сумматор, два цифровых управляемых резистора, два масштабныхрезистора и блок задания шага интерполирования, выходы которого соединены с управляющими входами перво(Л го и второго цифровых управляемых резисторов, первый из которых включен между входом и выходом дополнительного сумматора, а второй а между выходами третьего и четвертого ключей и входом интегратора, входы дополнительного сумматора через первый и второй масштабные резисторы соединены соответственно с вы4;; ходами интегратора и третьего запоминающего блока, а выход подключен to к третьему входу сумматора. о 00 сх

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Коробейников В.н | |||

| Исследование и разработка вопросов преобразования информации в устройствах графического взаимодействия экспериментатор - малая ЦВМ . | |||

| Диссертация на соиск.учен | |||

| степени канд | |||

| техн | |||

| наук, Киев, 1973, с.129-134 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-15—Публикация

1982-04-30—Подача