1

(21)4359097/24-24

(22)06.01.88

(46) 23.12.89. Бкхл. № 47

(72) Н.И.Хцынский, В.А.Ярандин,

В.П.Сидоренко и Л.М.Прокопенко

(53)681.327.6(088.8)

(56)Патент США № 4375085,

кл. G 11 С 11/40, опублик. 1983.

Патент ЕПВ № 0088815, кл. G 11 С 17/00, опублик. 1983.

(54)МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

(57)Изобретение относится к вычислительной технике, а именно к интегральным схемам электрически репрограмми- руемых постоянных запоминающих устройств. Цель изобретения - повьппение

накопитель содержит первые транзисторы 12, 13 предзаряда, вторые транзисторы 14, 15 предзаряда, адресные транзисторы 18, 19, транзисторы 16, 17 стирания с соответствующими связями. В режиме стирания информации высоковольтное напряжение подается на вход 30 стирания. Это напряжение передается одним из транзисторов 16, 17 в нужную секцию накопителя, а одним из транзисторов 18, 19 и транзисторами 6, 7 выборки слов - на электроды стирания (вторые обкладки конденса 1-ороБ 2) выбранных элементов 1 памяти. В результате стирание информации может быть произведено с использованием только одной специальной шины на каждую строку. Уменьшение количества шин снижает па- разистные емкости накопителя и, следовательно, повышает его бьютродейст

(Л

Изобретение относится к вычислительной технике, а именно к интегральным схемам электрически репрограмми- руемых по.стоянных запоминающих уст- РОЙСТВ.

Целью изобретения является повьше- ние быстродействия накопителя.

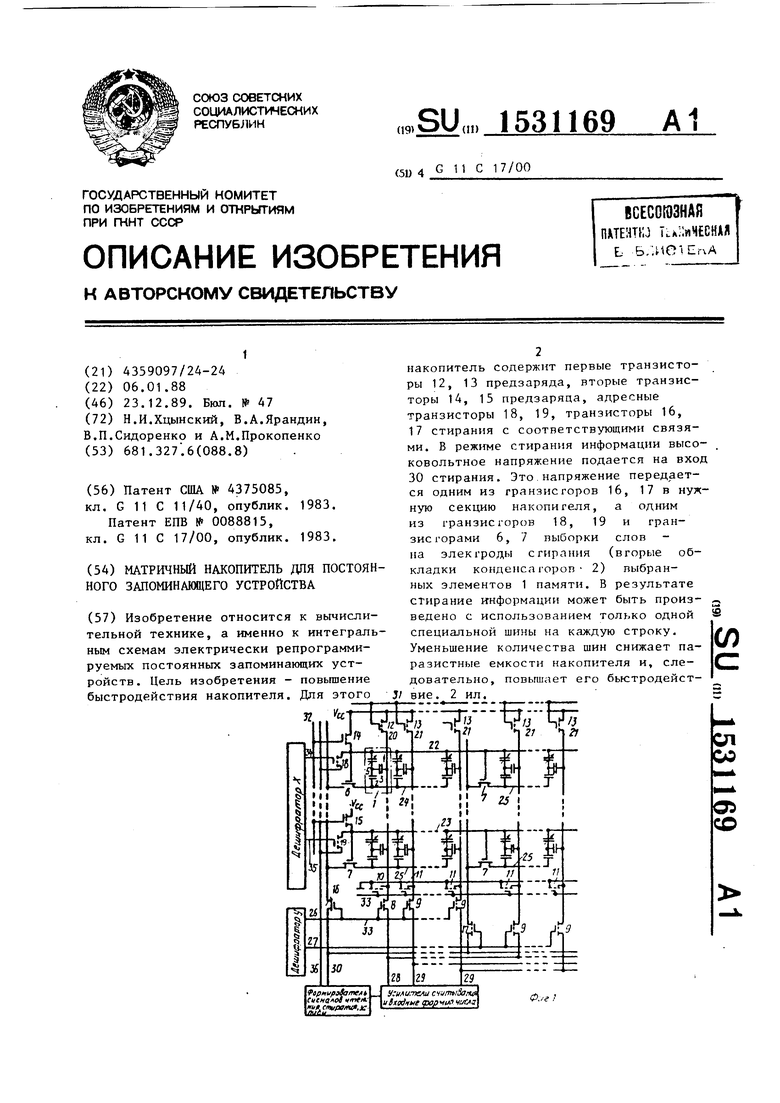

На фиг. 1 представлена электрическая схема накопителяi на фиг. 2 - вре менная диаграмма его работы.

Матричный накопитель содержит элементы 1 памяти, состоящие из трех конденсаторов 2-4, первые обкладки 5 которых объединены, транзисторы 6 и 7 выборки слов, транзисторы 8 и 9 выборки разрядов,разрядные транзисторы 10 и 11, первая группа транзисторов 12 и 13 предзаряда, вторая группа транзисторов 14 и 15 предзаряда, транзисторы 16 и 17 стирания, адресные транзисторы 18 и 19, разрядные шины 20 и 21, первые адресные шины 22 и 23, вторые адресные шины 24 и 25, входы 26 и 27 выборки разрядов, вхо- ды-выходы 28 и 29, вход 30 стирания, три входа 31-33 синхронизации, входы 34 и 35 выборки слов, вход 36 записи-считывания .

Конструктивно элемент 1 памяти представляет собой Г1ЛП-транзистор с плавающим затвором. Конденсатор 2 образован его плавающим и управляющим затворами, конденсатор 3 - туннельной областью и плавающим затвором, кон- денсатор 4 - областью истока и плавающим затвором. Объединенные первые обкладки 5 конденсаторов 2-4 являются плавающим затвором МДП-транзистоРа.

Предлагаемый матричный накопитель работает следующим образом.

При считывании в момент времени t на входы 31 и 32 подаются импульсы напряжения, втечение которых до момента времени с происходит заряд разрядных шин 20 и 21 и первых адресных щин 22 и 23. При этом на первых обкладках 5 элементов 1 памяти наводится за счет емкости конденсатора 3 перепад напряжения положительной полярности. Величина этого перепада зависит от знака заряда, хранимого на первых обкладках 5. Если хранится положительный заряд, то при подаче на адресные и разрядные шины 20-23 напряжения положительной полярности величина наведенного перепада потенциала на обкладках 5 значительно больше

0

,

Q

5 5

Q с

0

45

0

5

аналогичной величины в случае хране- ния на обкладках 5 отрицательного заряда. В момент tj на вход 36 подается отрицательный перепад напряжения от уровня питания, который адресный транзистор 18 при возбуждении его по выбранному входу 34 передается на первую адресную шину 22.

Если на обкладках 5 хранится положительный заряд, то отрицательный перепад напряжения передается на разрядную шину 20. Если на обкладках 5 хранится отрицательный заряд, то отрицательный перепад напряжения с первой адресной шины 22 практически не передается на разрядную шину 20. Далее считанный сигнал с шины 20 через транзистор 8, управляемый по входу 26, передается на вход-выход 28 накопителя. После окончания действия импульса отрицательной полярности в момент времени t через транзисторы 10 и 11 производится разряд шин 20 и 21 при подаче импульса по входу 23 для подготовки следующего акта считывания. В момент вермени t оканчивается действие импульса на входе 33.

Интервалы времени tg-t и относятся к случаям полувыборки элемента 1 по уходам 26 и 34 соответственно. Интервал времени t Сд относится к случаю невыбора элемента 1. В режиме стирания в момент времени t происходит подача сигналов выборки на входы 26 и 34 (высоковольтные сигналы), а также высоковольтных сигналов на вход 36 и через транзистор 18 на выбранную шину 22. В момент времени t на входе 30 стирания формируется высоковольтное напряжение, которое через открытые транзисторы 16 и 6 (шина 22 при этом уже заряжена через транзистор |8) передается на шину 24, Одновременно с этим на разрядных шинах 20 и 21 первой секции формируется нулевой потенциал. При этом высокое напряжение стирания прикладывается к конденсатору 2 выбранных элементов 1 памяти.

Во всех выбранных элементах 1 памяти за счет туннельного пробоя конденсатора 2 происходит накопление положительного заряда на обкладках 5, т.е. высокого логического уровня (1). В момент времени tj оканчивается .действие высоковольтного сигнала стирания, а в момент t4 производится отключение выбранных элементов

51

1 памяти. В течение интервала времени происходит разряд шины 24 на вход 30, находящийся под нулевым потенциалом, а шины 22 на вход 36, также находящийся в это время под нулевым потенциалом. Начиная с момента времени tg до момента времени t, происходит повторение цикла стирания, в течение которого элемент 1 памяти и другие элементы 1 данной секции накопителя оказываются полу- выбрайными по входу ЗА, а в течение интервала времени ,g они полувыбрны по входу 26. В течение указанных интервалов времени не происходит измнение состояния элементов 1 памяти. После момента времени t,o указанные элементы 1 находятся в невыбранном состоянии.

В режиме записи в момент времени с, происходит формирование адресных сигналов выб.орки на входах 26 и 34. В момент времени tj на вход 36 подаюся импульсы положительной полярности, а на входы-выходы 28 и 29 - высоковольтные сигналы записи (если необходимо произвести запись низкого логического уровня (О) в данный элемент 1 памяти) или нулевые потенциалы (если необходимо оставить элемент 1 в состоянии высокого логического уровня (1)). Эти сигналы передаются через транзсторы 8 и 9, открытые по входу 26, на разрядные шины 20 и 21 первой секции. В течение интервала времени t(-t2 происходит разряд шин 20, 22 и 24 до нулевого потенциала, заряженных в процессе предьщущих обращений к накопителю. В момент времени tj на вход 36 подается высокое напряжение, которое передается через транзистор 18 на шину 12. Снгнал записи на разрядных шинах 20 и 21 тех разрядов, где необходимо произвести запись логического уровня О, передается на обкладки 5. элемента 1 невыбранных строк, связанных с выбранной разрядной шиной 20, 21 (столбцом), на соответствующих первых адресных шинах 22 и 23 ранее установлен нулевой потенциал. Для этих элементов 1 на обкладки 5 предается с второй обкладки конденсатора 4 значительно меньшее напряжение. При этом в невыбранных элемента 1 памяти сохраняется существовавший ранее информационный заряд.

6

После окончания действия импульса, записи в момент t происходит разряд разрядных шин 20 и 21 и второй адрес- ной шины 22 через транзисторы 8 на входы-выходы 28 и 29 и вход 36. В момент времени с. прекращается действие сигналов выборки на входах 26 и 34. В течение интервалов рремени tg-tg

и (j происходит полувыборка тех же элементов 1 памяти по входам 26 и 34 соответственно, а после момента времени t- элементы 1 оказываются в невыбранном состоянии. В течение всего-11роцесса записи на входе 30 поддерживается низкий потенциал. В полувыбранном и невыбранном состоянии в процессе записи не создаются условия для изменения информационного заряда элементов 1 памяти.

Формула изобретения

Матричный накопитель для постоянного запоминающего устройства, содержащий секции памяти, каждая из которых состоит из элементов памяти, выполненных на трех конденсаторах, первые обкладки которых объединены, а вторые

подключены соответственно к первым и вторым адресным шинам и к разрядным шинам накопителя, транзисторы выборки слов, истоки которых подключены к соответствующим вторым адресным шинам

накопителя, затворы - к соответствующим первым адресным шинам накопителя,истоки транзисторов выборки слов каждой секции памяти накопителя объединены, соответствующие первые адресные шины всех секций памяти накопителя объединены, транзисторы выборки разрядов, стоки которых подключены к соответствующим разрядным шинам накопителя, затворы транзисторов выборки

разрядов каждой секции памяти объединены и являются соответствующими входами выборки разрядов накопителя, истоки соответствующих транзисторов выборки разрядов всех секций памяти

объединены и являются входами-выходами накопителя, разрядные транизсто- ры, истоки которых подключены к соответствующим разрядным шинам накопителя, отличающийся тем,

что, с целью повьш1ёния быстродействия накопителя, он содержит первую группу транзсторов предзаряда, вторую группу транзисторов предзаряда, адресные транзисторы, а в каждой секции памяти транзистор стирания, сток которого соединен со стоками транзис-- торов выборки слов этой секции памяти, затвор соединен с затворами транзисторов выборки разрядов этой секции памяти, а истоки транзисторов стирания всех секций памяти объединены и являются входом стирания накопителя, стоки транзисторов предзаряда первой и второй групп подключены к шине питания накопителя, затворы транзисторов предзаряда первой группы объединены и являются первым входом синхронизации накопителя, а истоки под- ключены к соответствующим разрядным шинам накопителя, затворы транзисто

ров предзаряда второй группы объединены и являются вторым входом синхронизации накопителя, а истоки соединены со стоками соответствующих адресных транзисторов и подключены к соответствующим первым адресным шинам, затворы адресных транзисторов являются входами выборки слов накопителя, а истоки объединены и являются входом записи-считывания накопителя, затворы транзисторов разряда объединены и являются третьим входом синхронизации накопителя, а истоки подключены к шине нулевого потенциала накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Постоянное запоминающее устройство | 1989 |

|

SU1635219A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

Изобретение относится к вычислительной технике, а именно к интегральным схемам электрически репрограммируемых постоянных запоминающих устройств. Цель изобретения - повышение быстродействия накопителя. Для этого накопитель содержит первые транзисторы 12, 13 предзаряда, вторые транзисторы 14, 15 предзаряда, адресные транзисторы 18, 19, транзисторы 16, 17 стирания с соответствующими связями. В режиме стирание информации высоковольтное напряжение подается на вход 30 стирания. Это напряжение передается одним из транзисторов 16, 17 в нужную секцию накопителя, а одним из транзисторов 18, 19 и транзисторами 6, 7 выборки слов - на электроды стирания (вторые обкладки конденсаторов 2) выбранных элементов 1 памяти. В результате стирание информации может быть произведено с использованием только одной специальной шины на кажду строку. Уменьшение количества шин снижает паразитные емкости накопителя и, следовательно, повышает его быстродействие. 2 ил.

t,t,t, tj t,t t,t,t,tttrtt tg, t t hVtit,tt t (а сттыввнае (9)стирате 2 (ft)

Авторы

Даты

1989-12-23—Публикация

1988-01-06—Подача