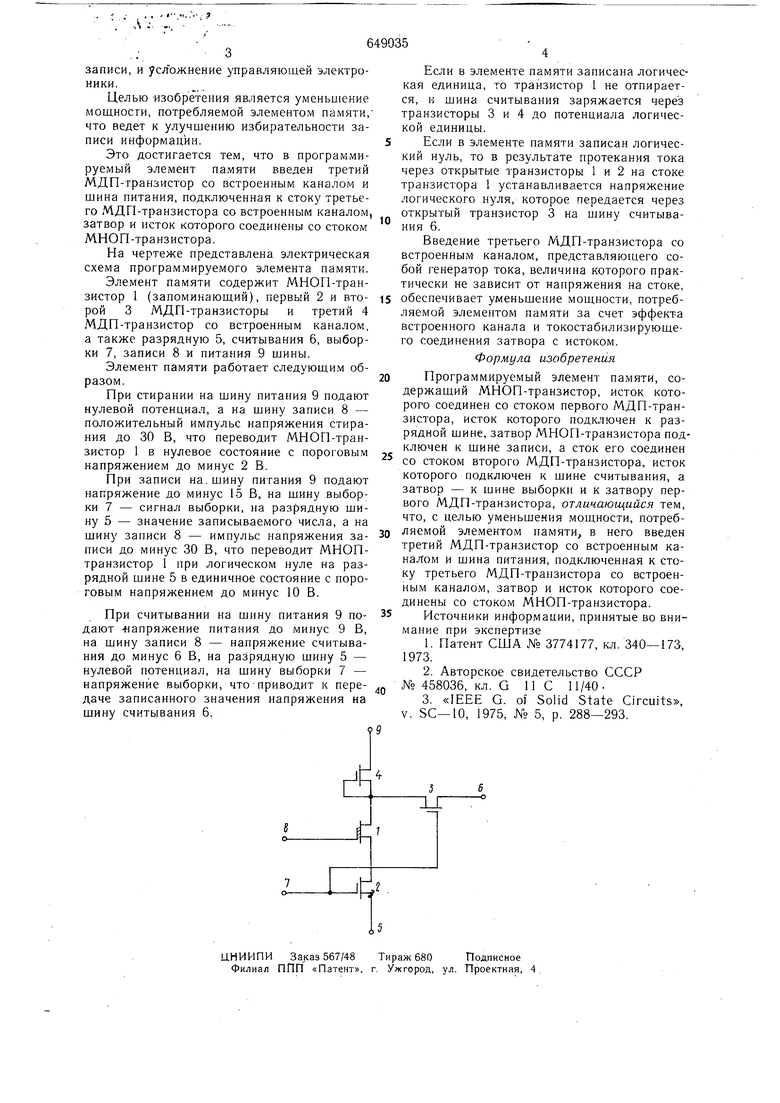

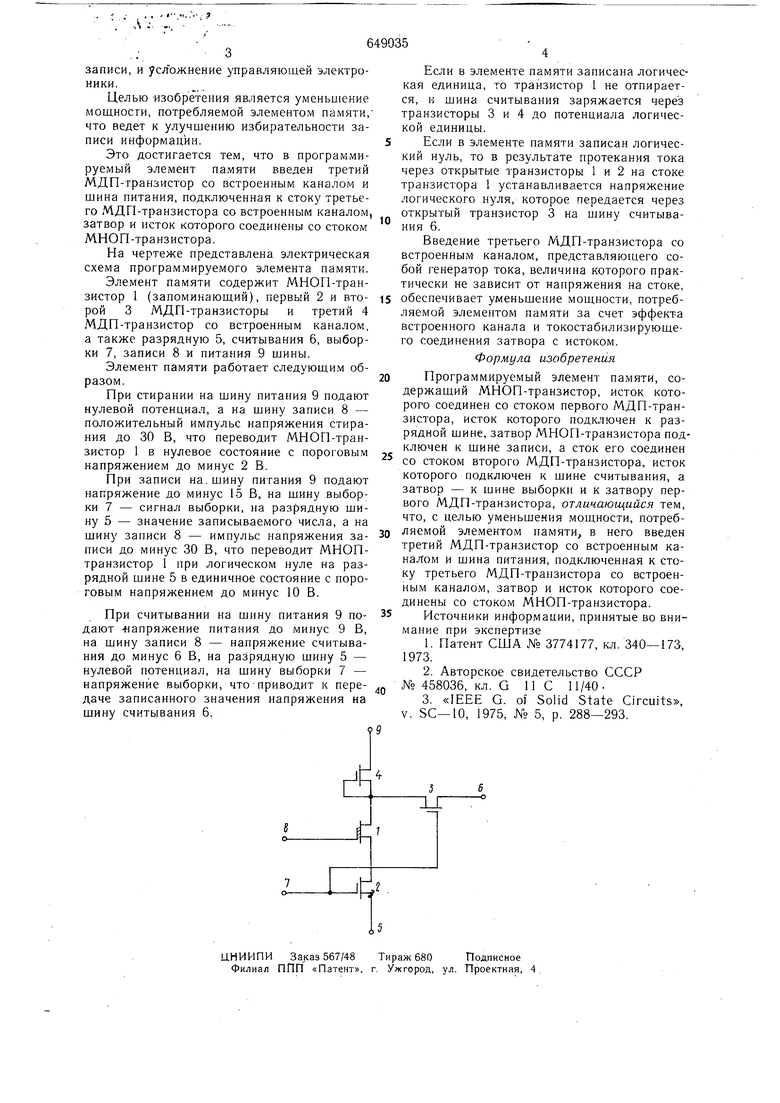

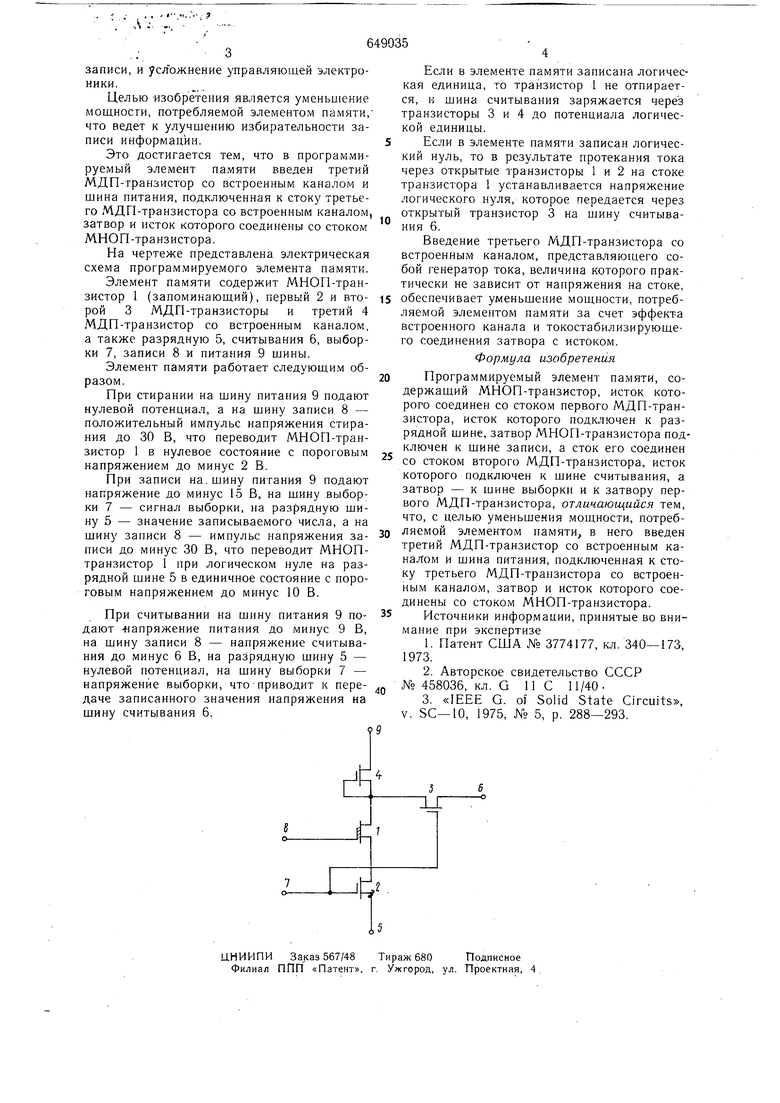

Изобретение откосится к вычислительной технике и может быть использовано в полупостоянных запоминающих устройствах с электрической перезаписью информации. Известен программируемый элемент памяти, содержащий два МДГ1-транзистора и один запоминающий МНОП-транзистор 1. В этом элементе памяти используется шина выборки в качестве программирующего входа в режиме записи и в качестве адресного входа в режиме считывания, что усложняет управление элементом памяти . Известен другой программируемый элемент памяти, также содержащий два МДПтранзистора и один МНОП-транзистор 2. Однако данный элемент памяти имеет невысокую избирательность записи информации из-за потери порогового напряжения в нагрузочных транзисторах, что приводит к уменьшению напряжения в невыбранных эле ментах памяти. Увеличение питающего напряжения в режиме записи для улучшения избирательности приводит к повышению потребляемой мощности, а заземление шины питания в режиме стирания не обеспечивает передачунулевого потенциала на стоки запоминающих МНОП-транзисторов, что снижает надежность из-за перенапряжений-в переходах затвор-сток при передаче положительных импульсов. Наиболее близким техническим решением к изобретению является программируемый элемент памяти, содержащий МНОП-транзиотор, исток которого соединен со стоком первого МДП-транзистора, исток которого подключен к разрядной шине, затвор МНОП-транзистора подключен к шине записи, а сток его соединен со стоком второго МДП-транзистора, исток которого подключен к шине считывания, а затвор - к шине выборки и к затво)у первого МДП-транзистора, причем МДП-транзисторы выполнены с индуцированным каналом, при записи применяется режим прямого туннелирования, а при стирании - лавинная инжекция 3. Однако этот элемент памяти имеет сложную систему адресации и управления, так как в режиме записи необходимо коммутировать высоковольтные сигналы, а в режиме считывания - низковольтные. Следствием этого является увеличение мощности, потребляемой элеме-нтом памяти в режиме записи, и усложнение управляющей электроники. Целью -изобретения является уменьшение мощности, потребляемой элементом памяти/ что ведет к улучшению избирательности записи информации. Это достигается тем, что в программируемый элемент памяти введен третий МДП-транзистор со встроенным каналом и шина питания, подключенная к стоку третьего МДП-транзистора со встроенным каналом, затвор и исток которого соединены со стоком МНОП-транзистора. На чертеже представлена электрическая схема программируе Мого элемента памяти. Элемент памяти содержит МНОП-транзистор 1 (запоминаюш.ий), первый 2 и второй 3 МДП-транзисторы и третий 4 МДП-транзистор со встроенным каналом, а также разрядную 5, считывания 6, выборки 7, записи 8 и питания 9 шины. Элемент памяти работает следующим образом. При стирании на шину питания 9 подают нулевой потенциал, а на шину записи 8 - положительный импульс напряжения Утирания до 30 В, что переводит МНОП-транзистор 1 в нулевое состояние с пороговым напряжением до минус 2 В. При записи на.шину питания 9 подают напряжение до минус 15 В, на шину выборки 7 - сигнал выборки, на разрядную шину 5 - значение записываемого числа, а на шину записи 8 - импульс напряжения записи до минус 30 В, что переводит МНОПтранзистор 1 при логическом нуле на разрядной шине 5 в единичное состояние с пороговым напряжением до минус 10 В. При считывании на шину питания 9 подают 41апряжение питания до минус 9 В, на шину записи 8 - напряжение считывания до минус 6 В, на разрядную шину 5 - нулевой потенциал, на шину выборки 7 - напряжение выборки, что приводит к передаче записанного значения напряжения на шину считывания 6. Если в элементе памяти записана логическая единица, го транзистор 1 не отпирается, к шина считывания заряжается через транзисторы 3 и 4 до потенциала логической единицы. Если в элементе памяти записан логический нуль, то в результате протекания тока через открытые транзисторы 1 и 2 на стоке транзистора 1 устанавливается напряжение логического нуля, которое передается через открытый транзистор 3 на шину считывания 6. Введение третьего МДП-транзистора со встроенным каналом, представляющего собой генератор тока, величина которого практически не зависит от напряжения на стоке, обеспечивает уменьшение мощности, потребляемой элементом памяти за счет эффекта встроенного канала и токостабилизирующего соединения затвора с истоком. Формула изобретения Программируе.мый элемент памяти, содержащий МНОП-транзистор, исток которого соединен со стоком первого МДП-транзистора, исток которого подключен к разрядной шине, затвор МНОП-транзистора подключен к шине записи, а сток его соединен со стоком второго МДП-транзистора, исток которого подключен к шине считывания, а затвор - к шине выборки и к затвору первого МДП-транзистора, отличающийся тем, что, с целью уменьшения мощности, потребляемой элементом памяти, в него введен третий МДП-транзистор со встроенным каналом и шина питания, подключенная к стоку третьего МДП-транзистора со встроенным каналом, затвор и исток которого соединены со стоком МНОП-транзистора. Источники информации, принятые во вни.мание при экспертизе 1.Патент США № 3774177, кл. 340-173, 1973. 2.Авторское свидетельство СССР № 458036, кл. G 11 С 11/403.«IEEE G. of Solid State Circuits, V. , 1975, № 5, p. 288-293.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1308063C |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Элемент памяти | 1984 |

|

SU1163356A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

Авторы

Даты

1979-02-25—Публикация

1977-10-20—Подача