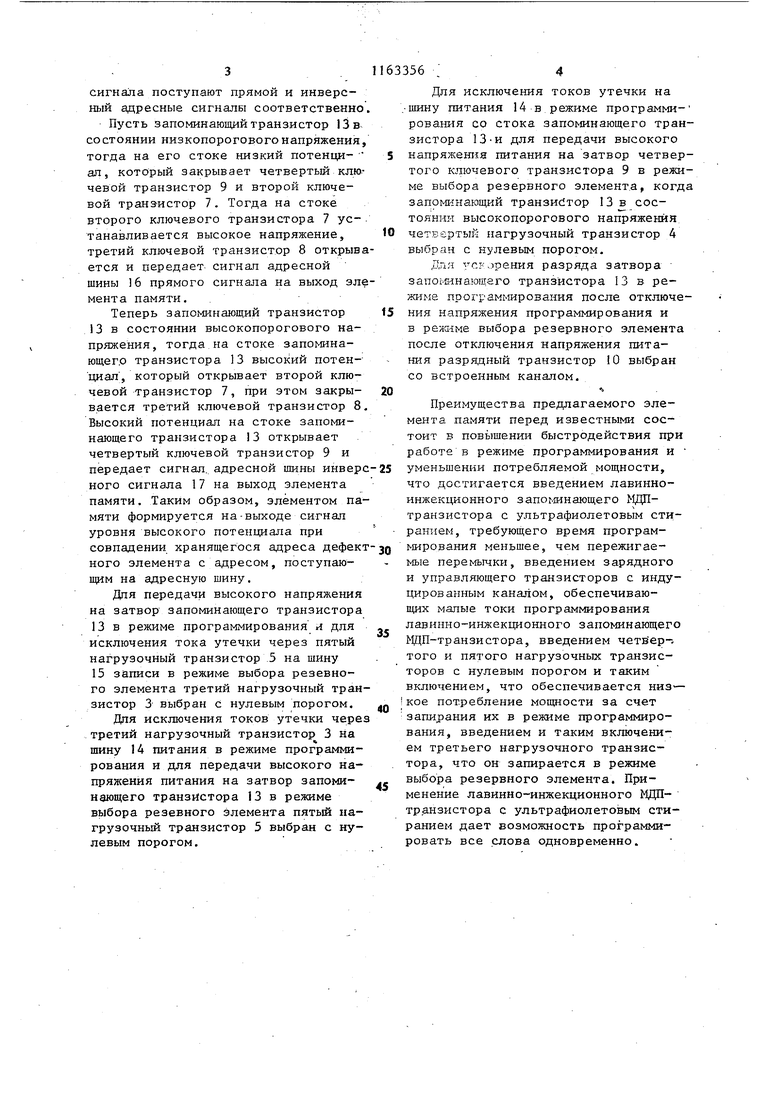

Изобретение относится к автоматике и вычислительной технике и мо жет быть использовано для хранения адреса дефектного элемента в запоминающих устройствах на основе МДП структур с резервированием. Цель изобретения - повышение бы стродействия элемента и уменьшение пот р е бля емой мощно с ти, На чертеже приведена схема пред лагаемого элемента памяти. Элемент памяти содержит первый и второй 2 нагрузочные транзисторы встроенным каналом, третий 3, четвертьй 4 и пятый 5 Harpy304iibie тран зисторы с нулевым порогом, первый б и второй 7 ключевые транзисторы с индуцированным каналом, третий 8 и четвертый 9 ключевые транзисторы с нулевым порогом, разрядный транзистор 10 со встроенным каналом, зарядный транзистор 11 с индуцированным каналом, управляющий транзистор 12 с индуцированным каналом запоминающий лавинно-инжекционньм транзистор 13 с ультрафиолетовым стиранием, шина 14 питания, шина 5 записи, адресная шина 16 прямого сигнала, адресная шина 17 инверсного сигнала, шина 8 нулевого потенциала. Элемент памяти работает в двух режимах: программирования и выбора резервного элемента. Режим программирования. Запоминающий транзистор 13 находится в исходном состоянии, которое соответствует -низкому пороговому напряжению. На. шину 14 питания подается напряжение I ят На ишну 15записи подается от внешнего источника питания напряжение програм мирования 22 В. ,На адресную шину 16прямого сигнала может подаваться либо истинный, либо ложный сигнал . Пусть на адресную шину 36 прямого сигнала поступает истинный сигна т.е. потенциал Лог; 1 ;-Тшс как на шину 15 записи подается напряжение программирования, то первый ключевой транзистор 6 открывается и на его стоке устанавливается низкий потенциал, который поддерживает управляющий транзистор 12 в закрытом состоянии. На затворе запоминающего транзистора 13 через открытый тре1ТИЙ нагрузочный транзистор 3 и раз62рядный транзистор о поддерживается напряжение порядка 20 В, и так как управляющий транзистор 12 закрыт, то на стоке запоминающего транзистора 13 поддерживается напряжение, близкое к и пкт ., через открытый четвертый нагрузочный тран- зистор 4 и, таким образом, запоминающий транзистор 13 остается в исходном состоянии, т.е. в состоянии низкопорогового напряжения, что соответствует хранению истинного сигнала. При этом пятый нагрузочный транзистор 5 закрыт, так как на его истоке высокий потенциал . Теперь на адресную шину 16 прямого сигнала поступает ложный сигнал, т.е.. потенциал Лог. О. Так как ,на шину 15 записи подается напряжение программирования, то первый ключевой транзистор 6 закрывается и на его стоке устанавливается высокий потенциал, который, поступая на затвор управляющего транзистора 12, открывает его и через открытые зарядный транзистор 1 1 , управляющей транзистор 12 протекает ток записи запоминающего транзистора, так как на затворе запоминающего транзистора 13 по-прежнему через открытый третий нагрузочный транзистор 3 и разрядный транзистор 10 поддерживаетс51 напряжение порядка 20 В и запоминаю1 Ц1Й транзистор 13 .переходит в состояние высокопорогового напряжения. При этом четвертый 4 и пятый 5 нагрузочные транзисторы закрыты из-за высокого потенциала на истоке. Режим выбора резервного элемента. В этом режиме на шине 15 записи нулевой потенциал, в закрытом состояни.и первый 1 и третий 3 нагрузочные транзисторы, зарядный транзистоЕ Я, разрядный транзистор 10. На шину 4 питания подается напряжение питания UpHT затвор запоминающего транзистора 13 через делитель, образованный пятым нагрузочным транзистором 5 и разрядным транзистором 10, подается напряжение, выбранное. из условия, что в состоянии низкопорогового напряжения запоминающий транзистор 13 открыг и в состоянии высокопорогового напряжения запоминающий транзистор 13 закрыт. На адресную шину 16 прямого сигнала и адресную шину 17 инверсного

сигнала поступают прямой и инверсный адресные сигналы соответственно

Пусть запоминающий транзистор 13в состоянии низкопорогового напряжения, тогда на его стоке низкий потенциап, который закрывает четвертый ключевой транзистор 9 и второй ключевой транзистор 7. Тогда на стоке второго ключевого транзистора 7 устанавливается высокое напряжение, третий ключевой транзистор 8 открывается и передает сигнал адресной шины 16 прямого сигнала на выход элемента памяти. . ,

Теперь запоминающий транзистор 13 в состоянии высокопорогового напряжения, тогда на стоке запоминающег.о транзистора 13 высокий потенциал, который открывает второй ключевой транзистор 7, при этом закрывается третий ключевой транзистор 8 Высокий потенциал на стоке запоминающего транзистора 13 открывает четвертый ключевой транзистор 9 и передает сигнал, адресной шины инверсного сигнала 17 на выход элемента памяти. Таким образом, элементом памяти формируется на-выходе сигнал уровня высокого потенциала при совпадении хранящегося адреса дефектного элемента с адресом, поступающим на адресную шину.

Дпя передачи высокого напряжения на затвор запоминающего транзистора 13 в режиме программирования и для исключения тока утечки через пятый нагрузочный транзистор 5 на шину 15 записи в режиме выбора резевного элемента третий нагрузочный транзистор 3 выбран с нулевым порогом.

Дпя исключения токов утечки через третий нагрузочный транзистор 3 на шину 14 питания в режиме программирования и для передачи высокого напряжения питания на затвор запоминающего транзистора 13 в режиме выбора резевного элемента пятый нагрузочный транзистор 5 выбран с нулевым порогом.

Для исключения токов утечки на ,-шину питания 14 в режиме программирования со стока запоминающего транзистора 13-и для передачи высокого 5 напряжения питания на затвор четвертого ключевого транзистора 9 в режиме выбора резервного элемента, когда запоминающий транзистор 13 в состоянии высокопорогового напряжения,

0 четвертый нагрузочный транзистор 4 выбран с нулевым порогом.

Дпя срорения разряда затвора запоминающего транзистора 13 в режиме программирования после отключе5 НИН напряжения программирования и в реяиме выбора резервного элемента после отключения напряжения питания разрядный транзистор 10 выбран со встроенным каналом.

0

Преимущества предлагаемого элемента памяти перед известными состоит в повышении быстродействия при работе в режиме программирования и

5 уменьшении потребляемой мощности, что достигается введением лавинноинжекционного запогданающего МДПтранзистора с ультрафиолетовым сти раннем, требующего время програм иpoвaния меньшее, чем пережигаемые перемычки, введением зарядного и управляющего транзисторов с индуцированным каналом, обеспечивающих малые токи программирования лавинно-инжекционного запоминающего МДП-транзистора, введением четвер- того и пятого нагрузочных транзисторов с нулевым порогом и таким включением, что обеспечивается низ- кое потребление мощности за счет запирания их в режиме программирования, введением и таким включением третьего нагрузочного транзистора, что он запирается в режиме выбора резервного элемента. Применение лавинно-инжекционного МДПтранзистора с ультрафиолетовым стиранием дает возможность программировать все слова одновременно.

fg.

.re

fi

f2

il

1

, /V .

о

a

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь напряжения записи | 1989 |

|

SU1681334A1 |

ЭЛЕМЕНТ ПАМЯТИ, содержащий первый нагрузочный транзистор, сток которого соединен с шиной записи, затвор и исток соединены со стоком первого ключевого транзистора, исток которого соединен с шиной нулевого потенциала, затвор - с адресной шиной прямых сигналов, второй нагрузочный транзистор, сток которого соединен с шиной питания, затвор и исток подключены к .стоку второго ключевого транзистора, исток которого соединен с шиной нулевого потенциала, третий ключевой транзистор, затвор которого соединен со стоком -второго ключевого транзистора, сток третьего ключевого транзистора соединен с адресной шиной прямка сигналов, четвертый ключевой транзистор, сток которого соединен с адресной шиной инверсных сигналов, исток - с истоком третьего ключевого транзистора и с выходом элемента памяти, отличающийбыстродействия элемента и ум.еньшенйя потребляемой мощности, в него введены третий нагрузочный транзистор, сток и затвор которого соединены с шиной записи, разрядный транзистор, сток которого соединен с истоком третьего нагрузочного транзистора, исток и. затвор которого соединены с шиной нулевого потенциала, зарядный транзистор, сток и затвор которого соединены с шиной записи, управл5пощий транзистор, сток которого соединен с истоком зарядного транзистора, затвор управляющего транзистора соединен со стоком первого С/) ключевого транзистора, запоминаюс: щий лавинно-инжекционный транзистор с ультра олетовьм стиранием, сток которого соединен с истоком управляющего транзистора, затвор- со стоком разрядного транзистора, исток - с шиной нулевого потенциала, четвертый нагрузочный транОд зистор, сток и затвор которого САЭ СО соединеш) с: шиной питания, исток с затвором четвертого ключевого оп транзистора и стоком запоминающего а транзистора, пятый нагрузочный транзистор, сток и затвор которого соединены с шиной питания, исток с затвором запоьшнающего транзистора, затвор второго ключевого транзистора соединен с затвором четвертого ключевого транзистора.

Пft

| .Патент США № 4288528, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Заявка ФРГ № 3138363, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1985-06-23—Публикация

1984-05-11—Подача