1

Изобретение отноеится к вычислительной и электронной технике, в частности к иолупроводниковым интегральным запоминающим устройствам (ЗУ).

Известны ЗУ с перезаписью информации, построенные как на основе запоминающих МИОИ-транзисторов (Me-51зЫ4-SiO2-Si) 1, так и запоминающих МАОП-транзисторов (Me-АЬОз-SiO2-Si) 2, содержащие накопитель и блоки управления, обеспечивающие Перезапись и считывание информации. Напряжение иитания подключается в этих устройствах к нагрузочным щинам накопителя с помощью МНОП (МАОП)-транзисторов в диодном включении.

Недостаток названных устройств - низкая избирательность записи информации, связанная с неиолной передачей напряжения питания на нагрузочные щины накопителя, вследствие потери порогового напряжения в МДП (МНОЙ, МАОН)-транзисторах при диодном включении.

Наиболее близким техническим рещениемк изобретению является ЗУ с перезаписью информации, содержащее накопитель, блок выборки столбцов и блок зправления перезанисью; разрядные щпны накопителя соединены с выходом блока выборки, а нагрузочные шины накопителя - с выходом блока управления перезаписью 3.

При приложении импульса записи к адресной шине накопителя нанряжение, экранирующее этот импульс в канала. невыбранных заиоминаюи 1,пх МДП-транзисторов, подключенных затворами к адресной шине, меньше напряжения иитания на величину порогового напряжения. Поэтому при амн.титуде иглпульса записи более -35 В и напряжении питания менее - 24 В имеет место иаразитное встраивание заряда, искажающее информацию в иевыбраиных транзисторах накоиителя, так как разность амплитуды импульса заиисп и экранирующего иаиряжения превышает граничное напряжение записи МДП-структуры. В связи с этим амплитуда импульса записи в схемах большой информационной емкостн не иревышает - 30 В, что приводит к иизкому быстродействию в режиме записи информации.

Недостатки данного устройства состоят в малом быстродействии н низкой избирательиости заииси информации.

Цель изобретения - повышеиие быстродействия и избирательпоети записи информации.

Это достигается тем, что в устройство введены блоки заирета записи, вход каждого из когорых соединен е соответствующим входом блока выборки столбцов, а выход подключеи к нагрузочной шине накопителя данного столбца.

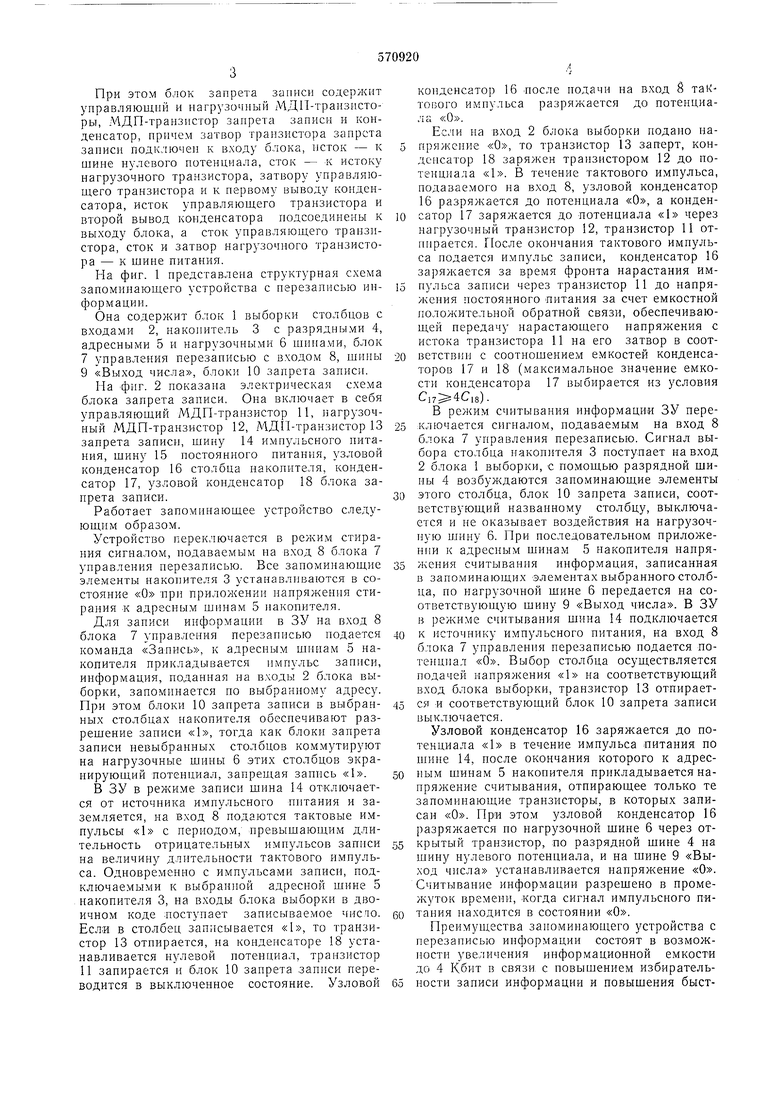

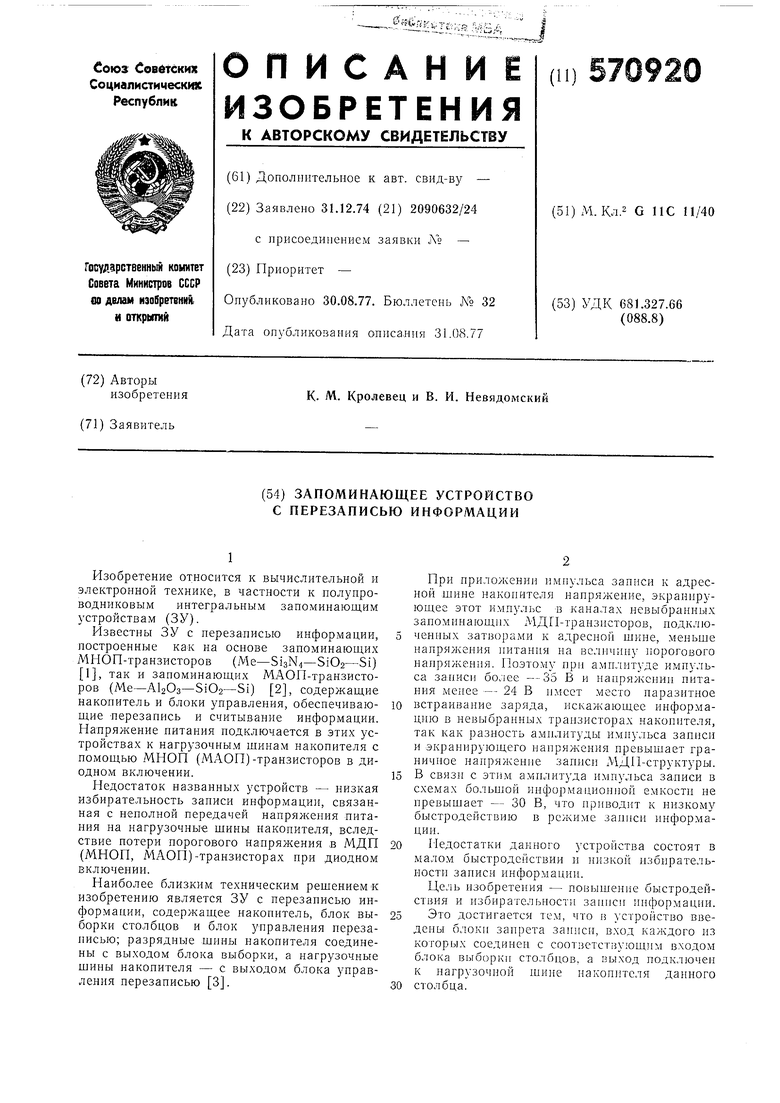

При этом блок запрета записи содержпт управляющий и нагрузочный МДП-транзисторы, МДП-транзпстор запрета записи и кондеисатор, причем затвор транзистора запрета записи подключеи к входу блока, исток - к шине пулевого потенциала, сток - к истоку нагрузочного транзистора, затвору управляющего транзистора и к первому выводу конденсатора, исток управляющего транзистора и второй вывод конденсатора подсоединены к выходу блока, а сток управляющего транзистора, сток и затвор нагрузочного транзистора - к шине питания.

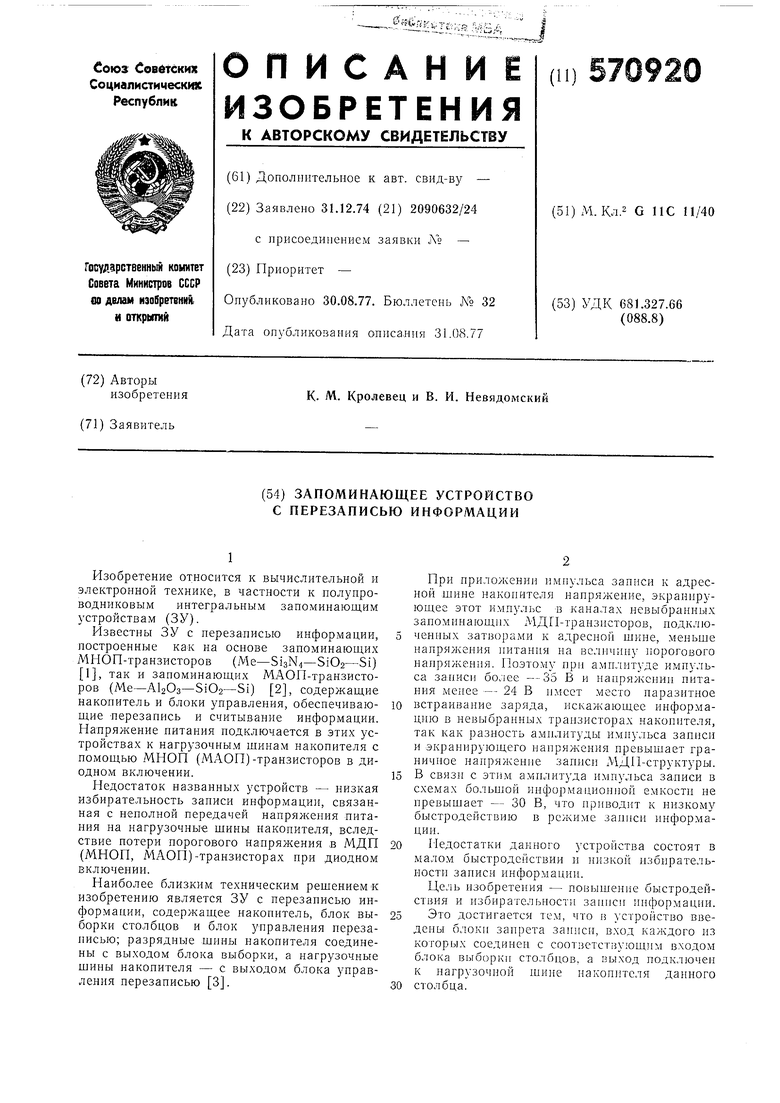

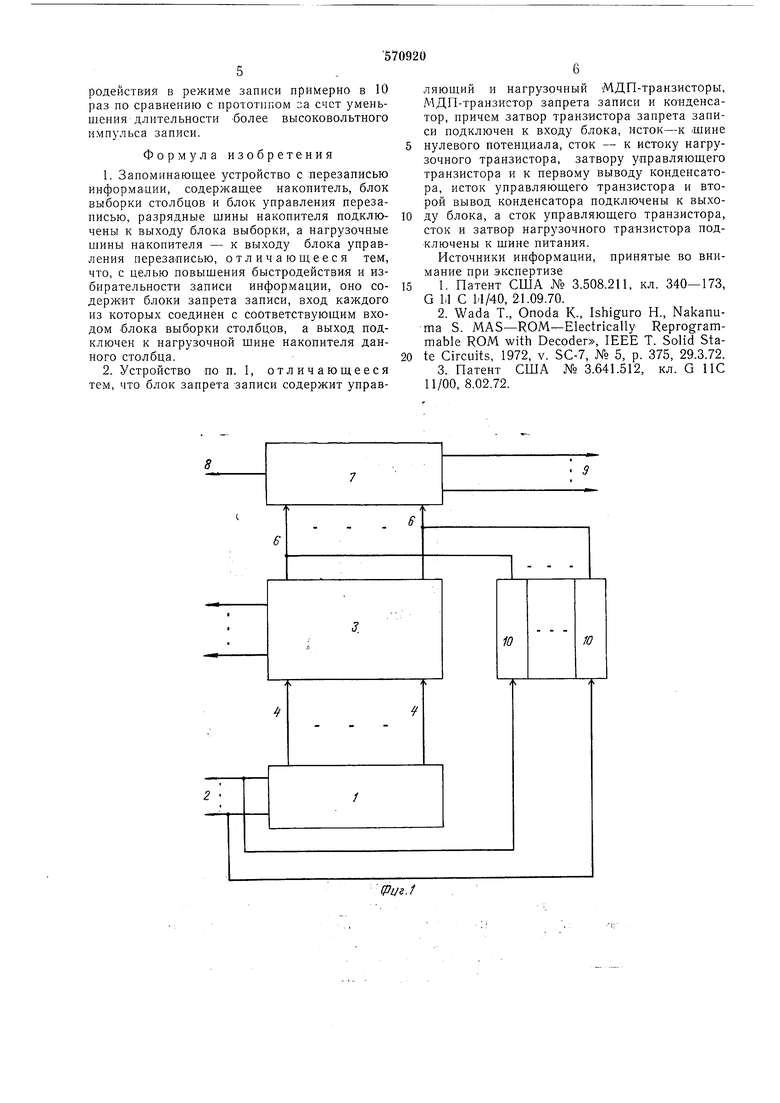

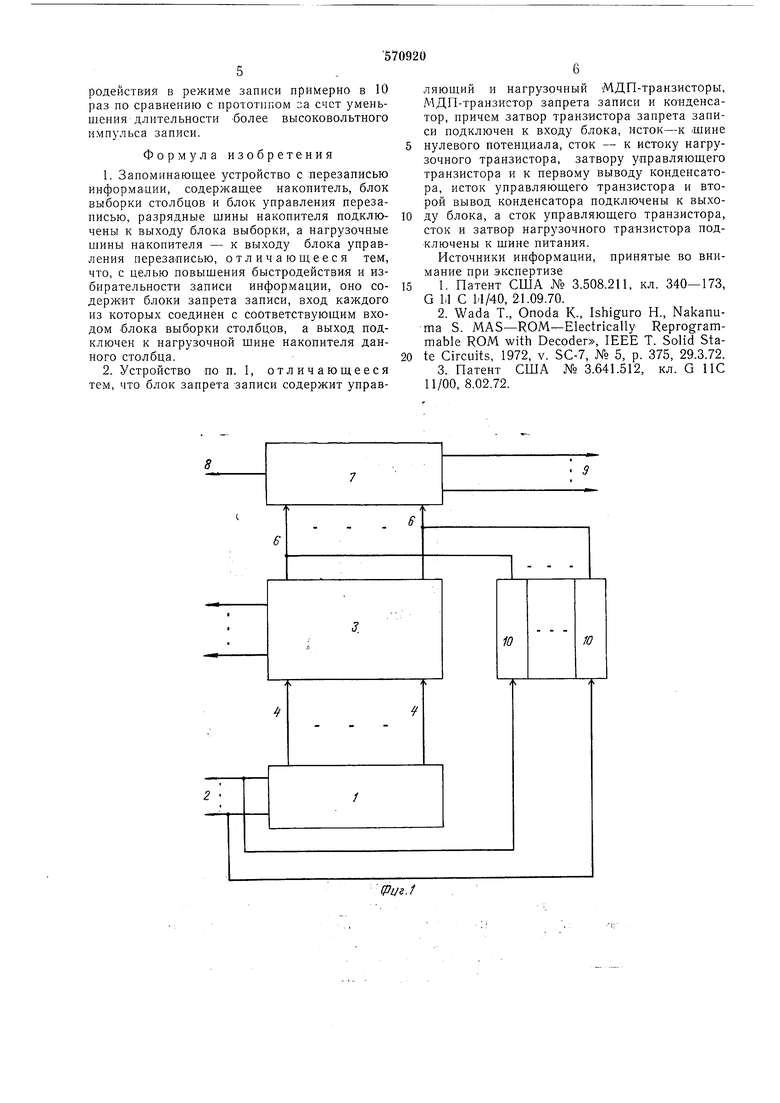

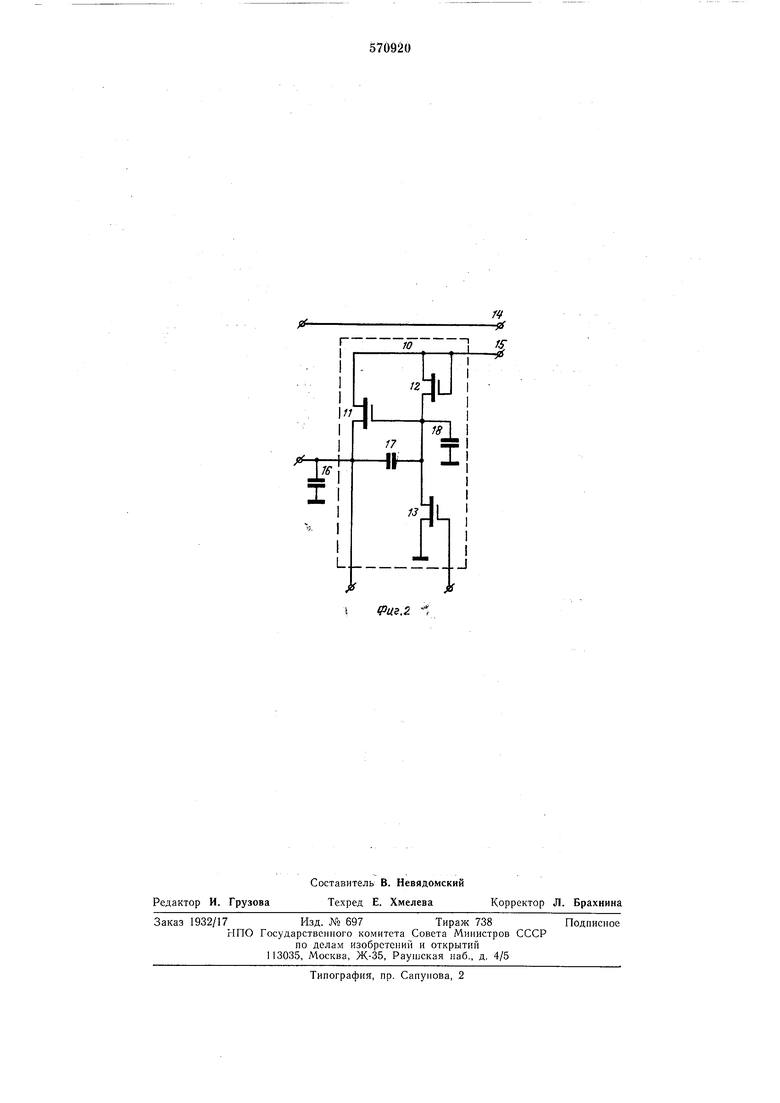

На фпг. 1 представлена структурная схема запоминающего устройства с нерезаиисью информации.

Она содержит блок 1 выборки столбцов с входами 2, накопитель 3 с разрядными 4, адресными 5 и нагрузочными 6 шипами, блок 7 управления перезаписью с входом 8, шины 9 «Выход числа, блоки 10 запрета записи.

На фиг. 2 иоказана электрическая схема блока запрета записи. Она включает в себя управляющий МДП-транзистор 11, нагрузочный МДП-транзистор 12, МД11-транзистор 13 запрета записи, шину 14 импульсного питания, шину 15 постоянного питания, узловой конденсатор 16 столбца накопителя, конденсатор 17, узловой конденсатор 18 блока запрета записи.

Работает запомннающее устройство следующим образом.

Устройство переключается в режим стирания сигналом, подаваемым на вход 8 блока 7 управления перезаписью. Все запоминающие элементы накопителя 3 устанавливаются в состояние «О при приложении иапряжения стирания к адресным щинам 5 накопителя.

Для записи информации в ЗУ на вход 8 блока 7 управления перезаписью подается команда «Запись, к адресным шинам 5 накопителя прикладывается импульс записи, информация, поданная на входы 2 блока выборки, запоминается по выбранному адресу. При этом блоки 10 запрета записи в выбрапных столбцах накопителя обеспечивают разрешение записи «1, тогда как блоки запрета записи невыбранных столбцов коммутируют на нагрузочные шины 6 этих столбцов экранирующий потенциал, запрещая запись «1.

В ЗУ в режиме записи щина 14 отключается от источника импульсного питания и заземляется, на вход 8 подаются тактовые импульсы «1 с периодом, превышающим длительность отрицательных импульсов записи на величину длительности тактового импульса. Одновременно с импульсами записи, подключаемыми к выбранной адресной шине 5 накопителя 3, на входы блока выборки в двоичном коде поступает записываемое число. Если в сто.лбец записывается «1, то транзистор 13 отпирается, на конденсаторе 18 устанавливается нулевой потенциал, транзистор И запирается и блок 10 запрета записи переводится в выключенное состояние. Узловой

конденсатор 16 лосле подачи на вход 8 тактового импульса разряжается до потенциала «О.

Если на вход 2 блока выборки подано напряжение «О, то транзистор 13 зап-ерт, конденсатор 18 заряжен транзистором 12 до потенциала «1. В течение тактового импульса, подаваемого на вход 8, узловой конденсатор 16 разряжается до потенциала «О, а конденсатор 17 заряжается до потенциала «1 через нагрузочный транзистор 12, транзистор И отинрается. После окончания тактового импульса подается импульс записи, конденсатор 16 заряжается за время фронта нарастания импульса записи через транзистор 11 до напряжения постоянного питания за счет емкостной положительной обратной связи, обеспечивающей передачу нарастающего напряжения с истока трапзистора И на его затвор в соответствии с соотношением емкостей конденсаторов 17 и 18 (максимальное значение емкости конденсатора 17 выбирается из условия

).

В режим считывания информации ЗУ переключается сигналом, подаваемым на вход 8 блока 7 управления перезаписью. Сигнал выбора столбца накопителя 3 поступает на вход 2 блока 1 выборки, с помощью разрядной шииы 4 возбуждаются запоминающие элементы этого столбца, блок 10 запрета записи, соответствующий названному столбцу, выключается и не оказывает воздействия на нагрузочную щииу 6. При последовательном приложении к адресным щинам 5 накопителя напряжения считывания информация, записанная в запоминающих элементах выбранного столбца, но нагрузочной шине 6 передается на соответствуюпхую шипу 9 «Выход числа. В ЗУ в режиме считывания шина 14 подключается к источнику импульсного питания, на вход 8 блока 7 уиравления перезаписью подается потенциал «О. Выбор столбца осуществляется подачей напряжения «1 на соответствующий вход блока выборки, транзистор 13 отпирается и соответствующий блок 10 запрета записи выключается.

Узловой конденсатор 16 заряжается до потенциала «1 в течение импульса питания по типе 14, после окончания которого к адресным щинам 5 накопителя прикладывается напряжение считывания, отпирающее только те запоминающие транзисторы, в которых записан «О. Нри этом узловой конденсатор 16 разряжается по нагрузочной щине 6 через открытый транзистор, по разрядной щине 4 на щину нулевого потенциала, и на шине 9 «Выход числа устанавливается напряжение «О. Считывание информации разрешено в промежуток времени, когда сигнал импульсного питания находится в состоянии «О.

Преимущества запоминающего устройства с перезаписью информации состоят в возможности увеличения информационной емкости до 4 Кбит в связи с повышением избирательности записи информации и повышения быстродействия в режиме записи примерно в 10 раз по сравнению с прототипом а счет уменьи1ения длительности -более высоковольтного импульса записи.

Формула изобретения

1.Запоминающее устройство с перезаписью информа-ции, содержащее накопитель, блох выборки столбцов и блок управления перезаписью, разрядные щины накопителя подключены к выходу блока выборки, а нагрузочные шины накопителя - к выходу блока управления перезаписью, отличающееся тем, что, с целью повышения быстродействия и избирательности записи информации, оно содержит блоки запрета записи, вход каждого из которых соединен с соответствующим входом -блока выборки столбцов, а выход подключен к нагрузочной шине накопителя данного столбца.

2.Устройство по п. 1, отличающееся тем, что блок запрета записи содержит управляющий и Нагрузочный МДП-транзисторы, ЛЩП-транзистор запрета записи и конденсатор, причем затвор транзистора запрета записи подключен к входу блока, исток-к шине нулевого потенциала, сток - к истоку нагрузочного транзистора, затвору управляющего транзистора и к первому выводу конденсатора, исток управляющего транзистора и второй вывод конденсатора подключены к выходу блока, а сток управляющего транзистора, сток и затвор нагрузочного транзистора подключены к щине питания.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3.508.211, кл. 340-173, G 1.1 С М/40, 21.09.70.

2.Wada Т., Onoda К., Ishiguro Н., Nakanuma S. MAS-ROM-Electrically Reprogrammable ROM with Decoder, IEEE T. Solid State Circuits, 1972, v. SC-7, № 5, p. 375, 29.3.72.

3.Патент США № 3.641.512, кл. G IIC 11/00, 8.02.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

Ю

10

Авторы

Даты

1977-08-30—Публикация

1974-12-31—Подача