Изобретение относится к вычислительной технике, в частности к электрически перепрограммируемым постоянным запоми- нающим устройствам (ЭППЗ), сохраняющим информацию при отключении источников питания.

Известен матричный накопитель для ЭППЗ, содержащий полупроводниковую подложку, первые и вторые разрядные шины, шины стирания и запоминающие элементы.

Запоминающие элементы выполнены в виде n-канальных запоминающих МДП-транзисторов с плавающими и управляющими затворами с туннелированием заряда через подзатворный диэлектрик n-канальных МДП-транзисторов на полупроводниковой подложке р-типа проводимости. Истоки запоминающих МДП-транзисторов соединены с вторыми разрядными шинами, управляющие затворы - со стирающими шинами, истоки МДП-транзисторов - с первыми разрядными шинами, их затворы - с адресными шинами, их подложки - с полупроводниковой подложкой.

Наличие ключевых МДП-транзисторов обеспечивает работоспособность при наличии отрицательных пороговых напряжений запоминающих МДП-транзисторов после стирания информации.

Основными недостатками этого матричного накопителя является большая площадь, занимаемая запоминающими и ключевыми МДП-транзистрами, использование диэлектрических слоев малой толщины (200 А), расположенных над легированными областями полупроводниковой подложки, что снижает выход годных микросхем, необходимость использования дешифрированных стирающих шин, что усложняет схему обрамления и увеличивает размер кристалла.

Наиболее близким техническим решением к данному является накопитель, содержащий запоминающие МДП-транзисто- ры, стоки которых соединены с одними разрядными шинами, истоки - с другими разрядными шинами, управляющие затворы - с соответствующими адресными шинами, стирающие затворы - с соответствующими шинами стирания, соединенными с общей шиной стирания, а подложки - с общей подложкой.

Недостатком матричного накопителя-прототипа является отсутствие построчного стирания информации из-за одновременной подачи напряжения на все шины стирания через общую шину стирания и низкое быстродействие при перепрограммировании.

Целью изобретения является повышение быстродействия и расширения функциональных возможностй путем построчного стирания накопителя.

Эта цель достигается благодаря тому, что известный матричный накопитель для постоянного запоминающего устройства содержит дополнительную общую шину стирания, одни и другие дополнительные МДП-транзисторы, при этом стоки одних дополнительных МДП-транзисторов соединены с общей шиной стирания, а затворы и истоки - соответственно с адресными шинами и шинами стирания соответствующих строк накопителя, подложки - с общей подложкой, а стоки других дополнительных МДП-транзисторов соединены с общей шиной стирания, истоки - с шинами стирания двух соответствующих строк накопителя, затворы - с дополнительной общей шиной стирания, а подложки - с общей подложкой.

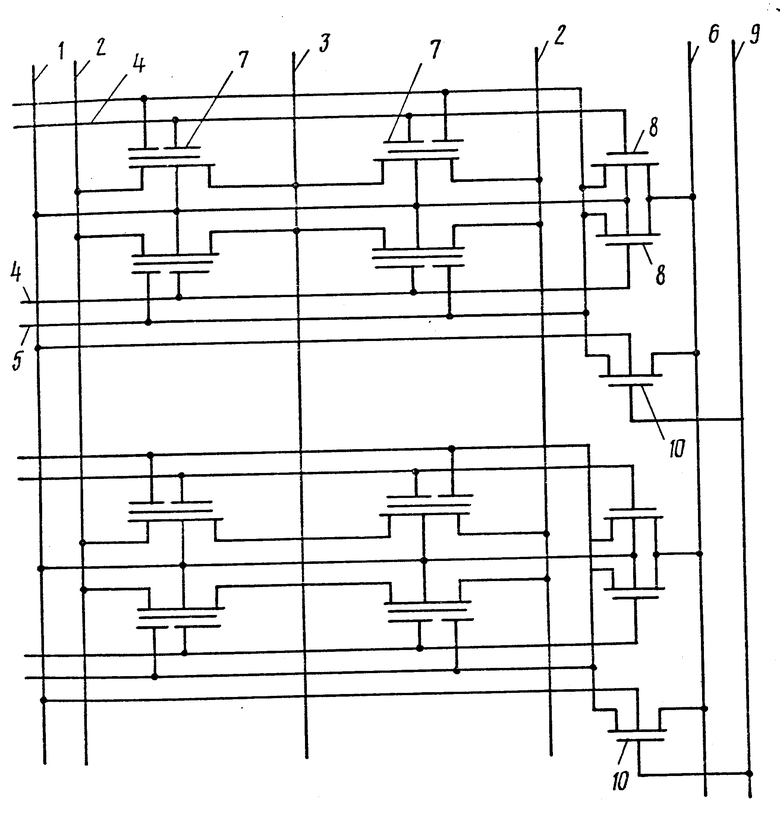

На чертеже изображен матричный накопитель.

Накопитель содержит общую подложку 1, одни 2 и другие 3 разрядные шины, адресные шины 4, шины стирания 5, общую шину стирания 6, запоминающие МДП-транзисторы 7, одни дополнительные МДП-транзисторы 8, дополнительную общую шину стирания 9, другие дополнительные МДП-транзисторы 10.

Матричный накопитель работает следующим образом. В режиме электрического программирования происходит изменение состояний с единичного (проводящего) в нулевое (непроводящее) только в заданные запоминающие МДП-транзисторы 7. Состояние остальных запоминающих МДП-транзисторов 7 остается без изменения. В этом режиме на общую шину стирания 6 и дополнительную общую шину стирания 9 подается низкое положительное напряжение (+5 В), в результате чего это напряжение передается через одни и другие дополнительные МДП-транзисторы 8 и 10 на все шины стирания 5 для уменьшения напряжения между выбранными адресными 4 и стирающими 5 шинами во время програм- мирования.

Для программирования нулевого состояния запоминающего МДП-транзистора 7 на его адресную шину 4 подают высокое положительное напряжение (+25 В), на одну разрядную шину 2 - напряжение (+15 В), на другую разрядную шину 3 - нулевое напряжение на время программирования (100 мс). За счет инжекции "горячих" электронов из канала выбранного запоминающего МДП-транзистора 7 электроны захватываются поликремниевым электродом, увеличивая его пороговое напряжение. При программировании изменения порогового напряжения у невыбранных запоминающих МДП-транзисторов 7 не происходит, так как на стоки или управляющие затворы подается нулевое напряжение или не заземлены их истоки.

В режиме построчного стирания на все разрядные шины 2 и 3 подают нулевое (или низкое положительное) напряжение.

На выбранную адресную шину 4 подают высокое положительное напряжение (+25 В), на остальные - нулевое. На общую шину стирания 6 подают высокое положительное напряжение (+25 В) малой длительности (10 мс).

Высокое напряжение на выбранной адресной шине 4 передается за затвор одного из дополнительных МДП-транзисторов 8; высокое напряжение с общей шины стирания 6 через открытый МДП-транзистор 8 передается на шину стирания 5. Под действием высокого напряжения на шине стирания 5 (+25 В) и нулевого напряжения на невыбранной адресной шине 4 с торцов плавающих затворов, находящихся под этой адресной шиной, инжектируются электроны, которые удаляются через шину стирания 5. В результате воздействия стирающего напряжения пороговое напряжение запоминающего МДП-транзистора 7 становится низким, что эквивалентно единичному состоянию. Стирания информации не происходит в запоминающих МДП-транзисторах 7, на адресные шины которых подано высокое положительное напряжение (+25 В), так как с управляющего затвора на плавающий затвор передается часть положительного напряжения, что приводит к уменьшению разности потенциалов между стирающим и плавающим затворами, к отсутствию инжекции электронов с плавающих затворов.

Таким образом, для стирания строки N необходимо выбрать N + 1 строку, если N нечетное число, N - 1 строку, если N - четное число.

Для одновременного стирания информации в матричных накопителях на все адресные 4 и разрядные шины 2 и 3 подают нулевое (или небольшое положительное) напряжение. На общую шину стирания 6 и дополнительную общую шину стирания 9 подают высокое импульсное положительное напряжение (+25 В) кратковременной длительности (10 мс). Высокое положительное напряжение с общей шины стирания 6 через открытые дополнительные МДП-транзисторы 10 передается на все шины стирания 5 одновременно, происходит удаление избыточных электронов с плавающих затворов. В результате этого у всех запоминающих МДП-транзисторов 7 устанавливаются низкие пороговые напряжения, что эквивалентно единичному состоянию.

Так как при построчном стирании время стирания информации из всего матричного накопителя составляет менее 5% от времени программирования, режим общего стирания рекомендуется использовть при разбраковке микросхемы на пластинах, так как все схемы перед проверкой их функционирования должны быть подвергнуты операции стирания для удаления заряда электронов с плавающих затворов после завершения высокотемпературных операций, которым были подвергнуты пластины со структурами в процессе изготовления.

В режиме считывания информации на общую шину стирания 6 и дополнительную шину стирания 9 подают нулевое напряжение, в результате чего на всех шинах стирания 5 через все открытые дополнительные МДП-транзисторы 8 передается нулевое напряжение. На выбранную адресную шину 4 подают низкое положительное напряжение, на другую разрядную шину 3 - нулевое напряжение. Если напряжение на адресной шине превышает пороговое напряжение запоминающего МДП-транзистора 7, что через него протекает ток, что эквивалентно единичному состоянию запоминающего МДП-транзистора 7.

Матричные накопители без ключевых МДП-транзисторов проще по конструкции и технологии их изготовления, но для обеспечения положительного порогового напряжения запоминающих МДА-транзисторов после стирания информации требуется использовать более сложную схему обрамления.

Матричные накопители с ключевыми МДП-транзисторами могут работать с отрицательными пороговыми напряжениями запоминающих МДП-транзисторов после стирания информации, что упрощает схему обрамления за счет усложнения конструкции и технологии изготовления матричного накопителя.

Предложенное техническое решение может быть использовано в матричных накопителях разнообразных конструкций без ключевых МДП-транзисторов в запоминающих элементах, с ключевыми МДП-транзисторами в запоминающих элементах с двухслойной или трехслойной поликремниевой разводкой, с высоковольтным или низковольтным считывающими напряжениями, для однобитных и двухбитных запоминающих элементов с постоянно заземленными или виртуально заземленными разрядными шинами.

Затворы МДП-транзисторов 8 и 10 с обеднением могут быть выполнены из первого, второго, третьего слоев поликремния.

Основным преимуществом предлагаемого матричного накопителя является обеспечение построчного стирания инфор- мации. Это позволяет в N раз (где N - число строк) сократить время перепрограммирования информации в любой строке матричного накопителя. Например, при организации матричного накопителя 128х128 бит время перепрограммирования строки матричного накопителя сокращается примерно в 128 раз. Возможность оперативного перепрограммирования матричного накопителя позволяет уменьшить требуемое число циклов перепрограммирования всего матричного накопителя.

МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий запоминающие МДП-транзисторы, стоки которых соединены с одними разрядными шинами, истоки - с другими разрядными шинами, управляющие затворы - с соответствующими адресными шинами, стирающие затворы - с соответствующими шинами стирания, соединенными с общей шиной стирания, а подложки - с общей подложкой, отличающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем построчного стирания накопителя, он содержит дополнительную общую шину стирания, одни и другие дополнительные МДП-транзисторы, при этом стоки одних дополнительных МДП-транзисторов соединены с общей шиной стирания, а затворы и истоки - соответственно с адресными шинами и шинами стирания соответствующих строк накопителя, подложка - с общей подложкой, а стоки других дополнительных МДП-транзисторов соединены с общей шиной стирания, истоки - с шинами стирания двух соответствующих строк накопителя, затворы - с дополнительной общей шиной стирания, а подложки - с общей подложкой.

| Патент США N 4203158, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1994-12-30—Публикация

1981-06-19—Подача