Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и устройствах обработки цифровой ин(})ормации.

Цель изобретения - расширение области применения.

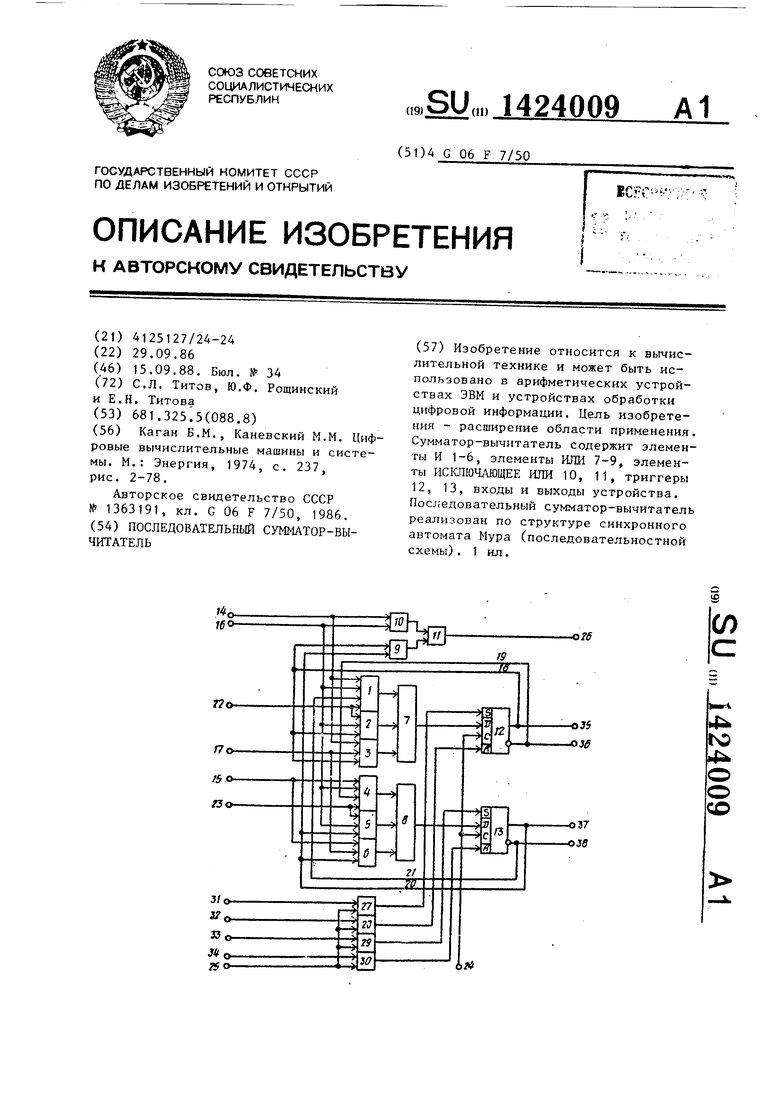

Па чертеже изображена схема последовательного сумматора-вычитателя

Последовательный сумматор-вычита- тель содержит первый - шестой элементы И 1-6, первьш - третий элементы lUM 7-9, первый 10 и второй 11 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 12 и второй 13 триггеры, прямой 14 и ин версный 15 входы первого операнда, прямой 16 и инверсный 17 входы второго операнда, прямой 18 и инверсный 19 оходы переноса из предыдущего разряда, прямой 20 и инверсный 21 входы заема из предыдущего разряда, управляющий вход 22 сложения, управ- ЛЯ115ЩИИ вход 23 вычитания, рход 24 тактирования, вход 25 установки, вы- ход 26 сумматора-вычитателя, седь- Moii - десятый элементы И 27-30, прямо 3 HHBcpcHbii i 32 входы переноса и П11 2дьщу1цего устройства, прямой 33 и инверсный 34 пходы з.1ема из предыду- 1це:. о устройства, прямо; 35 и инверс- ны 36 выходы переноса в следующее ycTpofici Bo, прямой 37 и инверсный 38 иьгкоды 5асма в следующее ус Г ройство.

Последоватольньи сумматор-вычита- тель реализован по структуре синхронного авто;- ата Мура (последователь- ностной схемы), Первьй - шестой элементы И 1 6, перв1лй 7 и второй 8 э:;ементы ЯШ1 образуют комбинационную схему, которая формирует текущую 4) нкцию возбуж 1ения для элементов памяти, которыми являются первьй 12 и BTopoii 13 триггер1л, определяющих текущее внутреннее состояние после- довательностной схемы. Первый 10 и второй 1 1 элементы ИСКЛЮЧАЮЩЕЕ ШШ и трети элемент ИЛИ 9 образуют комбинационную схему, формирующую текущее значение выходного бита в зави- симости от значений текущих бит первого и второго операндов, поступающих на прямые и инверсные входы первого 14, 15 и второго 16,17 операндов соответственно и текущего внут- реннего состояния схемы, определяемого первым 12 и вторым 13 триггерами. Седьмой-десятый элементы И 27- 30 служат для формирования в начале

каждого цикла вычисления стимулирующих сигналов для принудительной предустановки триггеров 12,13 в зависимости от состояния сигналов переноса и заема из предыдущего каскада (предыдущего сумматора-вычитателя).

Последовательный сумматор-вычита- тель работает следующим образом.

В начале каждого цикла вычисления на вход 25 установки поступает единичный импульс. В зависимости от состояния сигналов переноса и заема, которые поступают из предыдущего каскада соответственно на пары входов 31, 32 и 33, 34 (причем присутствие единичного потенциала сразу на двух прямых входах переноса и заема является запрещенной комбинацией), триггеры 12 и 13 устанавливаются в соответствующее (нулевое или единичное) состояние,

Затем по прямому 14 и инверсному

15входам первого операнда и прямому

16и инверсному 17 входам второго операнда начинают последовательно поступать биты чисел соответственно первого (уменьшаемого) и второго (вычитаемого) слагаемых. Поступление каждого бита операндов сопровождается тактовыми сигналами, поступающими по входу 24 тактирования, при этом число тактовых импульсов, поступающих по входу 24 тактирования, равняется разрядности операндов.

Для наглядности описания положим, что в начале цикла вычисления выполняется операция сложения. В этом случае по управляющему входу 22 сложения поступает единичн|,1Й потенциал, а по управляющему входу 23 вычитания - нулевой потенциал. После прихода очередных бит операндов в зависимости от их значения и значения сигнала на прямом входе 18 переноса, который Поступает с прямого выхода первого триггера 12, на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 формируется выходной бит суммы. Комбинационная схема, образованная первым - третьим элементами И 1-3 и первым элементом Ш1И 7, формирует функцию возбуждения (сигнал лог. О или лог. 1) для первого триггера 12. С приходом тактового импульса по входу 24 тактирования значение сигнала с выхода первого элемента ИЛИ 7 переписывается в первый триггер 12. Им будет определяться внутреннее состояние устройства в следующем такте

вычисления. На гныходе нторся о элемента Ш1Н 8 на все премя выполнения операции сложения будет присутствовать сиг нал лог, О, так как четвертый 4 и пятый 5 элементы блокируются сигналом лог. О с управляющего входа 23 вычитания, а шестой элемент И 6 закрыт нулевым потенциалом с прямого выхода второго триггера 13.

После смены выполняемой операции, что определяется появлением сигнала лог. О на управляющем входе 22 сложения и сигнала лог. 1 на управляющем входе 23 вычитания, на выходе первого элемента ИЛИ 7 генерируется сигнал лог. 1 функции возбуждения первого триггера 12 до тех пор, пока по прямому входу 14 первого операнда Поступают единичные биты уменьшаемого, а пбрвьп г-триггер 12 находится в единичном состоянии. Если же хотя бы одно из указанных вьпле условий не выи шестого элементов И, прямш вхсщ второго операнда сумматора--вычитате- ля подключен к вторым входам первого элемента ИС1чЛЮЧЛЮЩЕЕ НИИ и первого, второго, четвертог о и мятого тов И, инверсный вход второго операнда сумматора-вычитателя соединен с вторыми входами третьего и шестого элементов И, прямой выход первого триггера соединен с первым входом третьего элемента ИЛИ и третьими входами второго и третьего элементов И, инверсный выход первого триггера подключен к третьему входу четвертого элемента 11, прямой выход второго триггера соединен с вторым входом третьего элемента ИЛИ и третьими входами пятого и шестого элементов И, инверсный выход второго триггера подключен к третьему входу первого элемента И, управляющиГт вход сложения сумматора-в1 1читателя подключен к четвертому входу первого элемента

полняется или поступает единичный бит вычитаемого по прямому входу 16 И и первому входу второго элемента второго операнда, то на выходе пер- И, управляюпц й вход вычитания сумма- вого элемента ИЛИ 7 до конца цикла вычисления будет генерироваться сигнал Лог.О. На выходе второго элемента ИЛИ 8 сигнал функции возбуждения второго триггера 13 первый раз примет единичное значение в случае единично го бита на прямом входе 16 второго операнда при нулевых значениях на

30

прямом входе 14 первого операнда и прямом выходе первого тригг-ера 12. . После этого цикл вычисления продолжается с генерацией сигналов на входе 20 эаема.

Формула изобре

Последовательный сумматор-вычита- тель, содержащий шесть элементов И, три элемента ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и два триггера, D-входы

тора-вычитателя подключен к четвертому входу четвертого элемента И и первому входу пятого элемента И, входы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами первого элемента ИСКЛЮЧА ОШЕЕ Ш1И и третьего элемента ИЛИ, а вькод является выходом результата сумматора-вычитате- ля, тактовыГ) вход которого соединен 35 с тактовыми входами триггеров, о т- л и ч а ю щ и и с я тем, что, с целью расширения области применения, в него введены седьмой, восьмой, девятый и десятый элементы И, первые тения 40 входы которых подключены к входу установки сумматора-вычитателя, а вторые йходы подключены соответственно к прямому и инверсному входам переноса и пpямo fy и инверсному вхо

и шестого элементов И, прямш вхсщ второго операнда сумматора--вычитате- ля подключен к вторым входам первого элемента ИС1чЛЮЧЛЮЩЕЕ НИИ и первого, второго, четвертог о и мятого тов И, инверсный вход второго операнда сумматора-вычитателя соединен с вторыми входами третьего и шестого элементов И, прямой выход первого триггера соединен с первым входом третьего элемента ИЛИ и третьими входами второго и третьего элементов И, инверсный выход первого триггера подключен к третьему входу четвертого элемента 11, прямой выход второго триггера соединен с вторым входом третьего элемента ИЛИ и третьими входами пятого и шестого элементов И, инверсный выход второго триггера подключен к третьему входу первого элемента И, управляющиГт вход сложения сумматора-в1 1читателя подключен к четвертому входу первого элемента

И и первому входу второго элемента И, управляюпц й вход вычитания сумма-

30

35 40

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор-вычитатель | 1986 |

|

SU1363191A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Устройство для выполнения базовой операции быстрого преобразования Хартли-Фурье вещественных последовательностей | 1990 |

|

SU1718229A1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 2005 |

|

RU2295147C1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и устройствах обработки цифровой информации. Цель изобретения - расширение области применения. Сумматор-вычитатель содержит элементы И 1-6, элементы ШШ 7-9, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ Ю, 11, триггеры 12, 13, входы и выходы устройства. Пос;;едовательный сумматор-вычитатель реализован по структуре синхронного автомата Мура (последовательностной схемы). 1 ил.

которых подключены к выходам соответ- 45 дам заема сумматора-вычитателя, выственно первого и второго элементов ИЛИ, входы первого элемента ИЛИ соединены с выходами первого, второго и третьего элементов И, входы второго элемента ИЛИ соединены с выходами 50 соответственно прям1)1м и инверсным вычетвертого, пятого и шестого элементов И, прямой нход первого операнда сумматора-вычитателя подключен к первым входам первого элемента ИСКЛЮХО.1Ы седьмого и восьмого элементов И подключены соответственно к S- и R-входам первого триггера, прямой и инверсный выходы которого являются

ходами переноса сумматора-вычитателя, а выходы девятого и десятого элементов И подключены соответственно к S- и R-входам второго триггера, пря

| Каган Б.М., Каневский М.М | |||

| Цифровые вычислительные машины и системы | |||

| М.: Энергия, 1974, с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Последовательный сумматор-вычитатель | 1986 |

|

SU1363191A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1986-09-29—Подача