оэ со

4. О

316

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано в системах с преобразованием произвольных Р-ичных кодов, а также в устройствах автоматики для контроля и слежения за различными параметрами

Цепь изобретения - расширение функциональных возможностей за счет преобразования произвольного Р-ичног о кода с любым основанием в каждом разряде в произвольный код с другим основанием в каждом разряде.

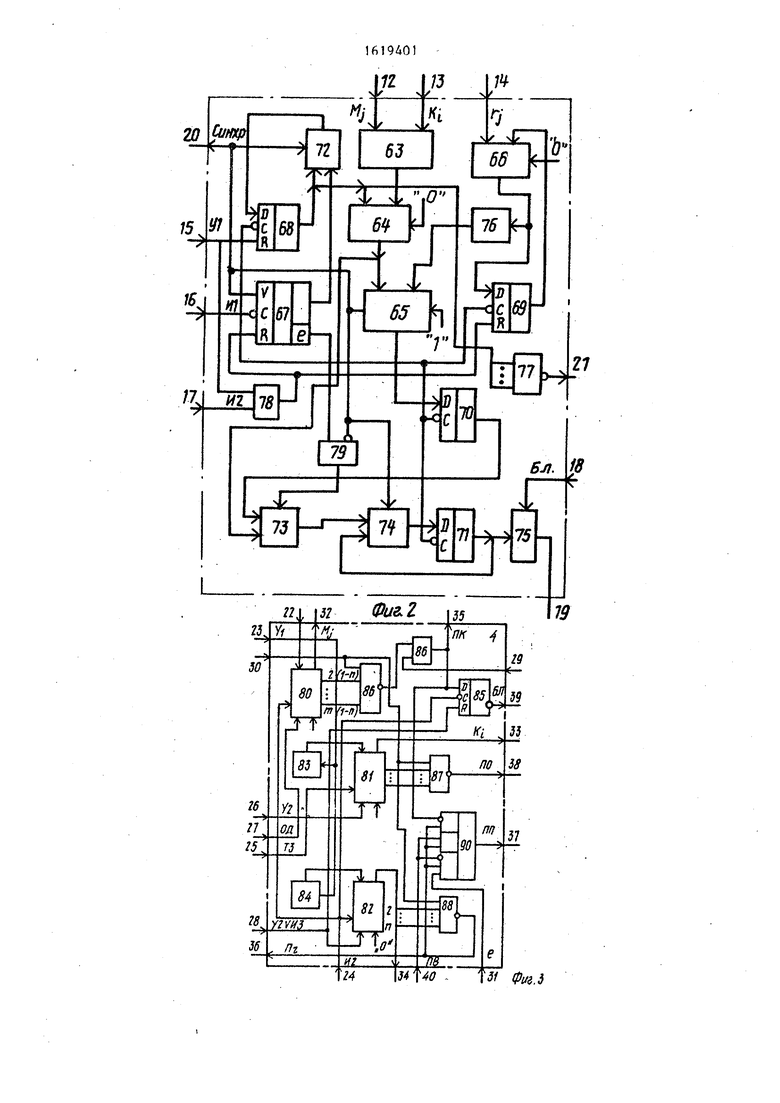

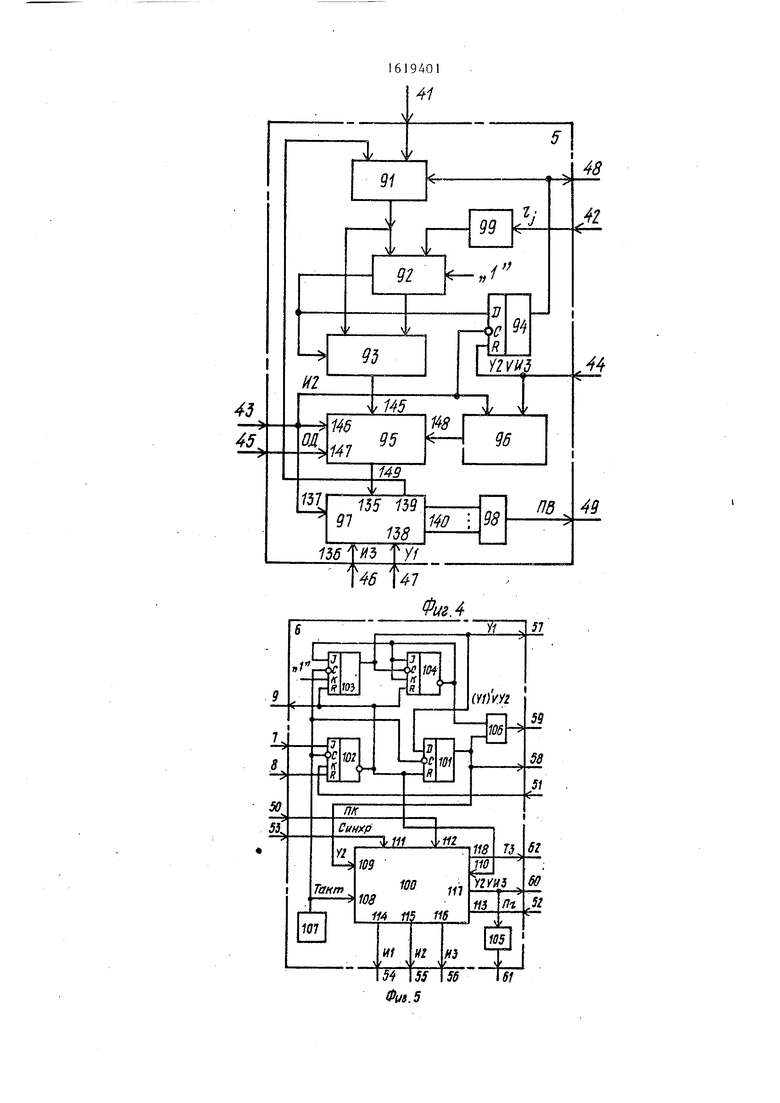

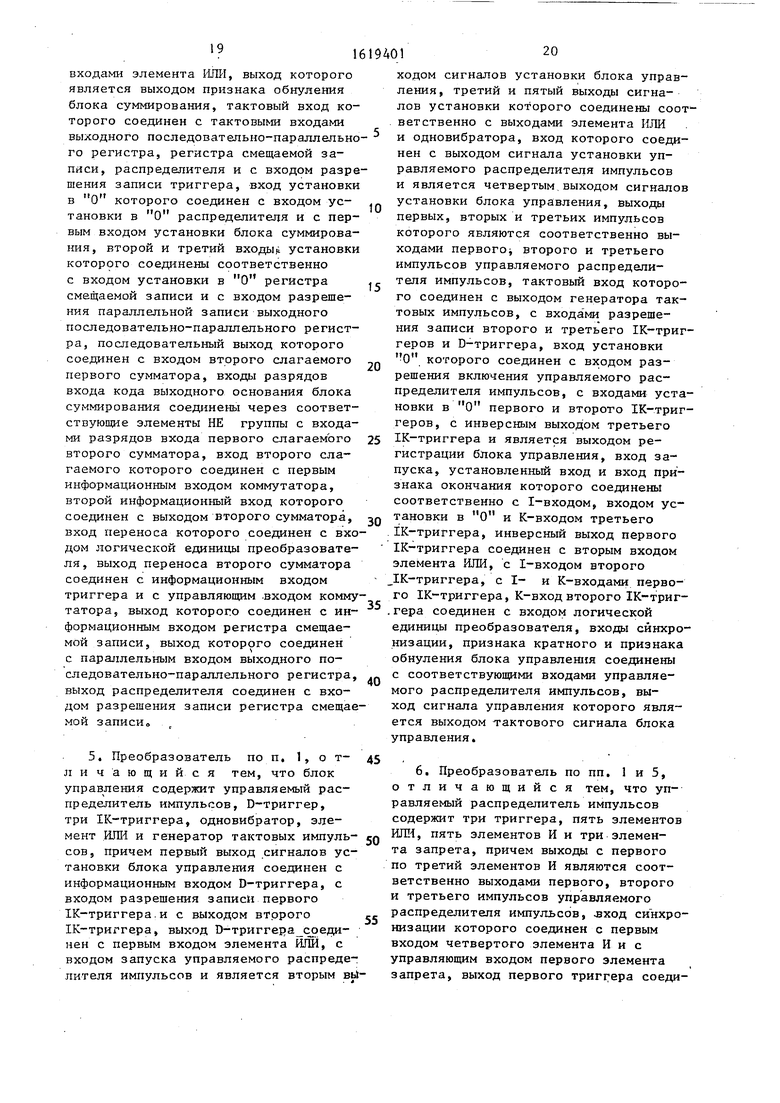

На фиг. 1 изображена схема преоб- разрвателя кода; на фиг.2 - функциональная схема блока формирования кратных; на фиг 3 - функциональная схема блока формирования признаков; на фиг. 4 - функциональная схема бло- ка суммирования; на фиг. 5 - функциональная схема блока управления; на фиг.6 - схема управляемого распределителя импульсов; на фиг. 7 - схема последовательно-параллельного регист- ра; на фиг 8 - схема регистра смещаемой записи« ч

Преобразователь кода фиг.1 со-, содержит блок 1 постоянной памяти, счетчик 2 адреса, блок 3 формирования кратных, блок 4 формирования признаков, блок 5 суммирования, блок 6 управления, вход 7 запуска преобразователя, вход 8 установки преобразователя, выход 9 регистрации преобразователя, вход 10 адреса преобразователя, выход 11 признака переполнения преобразователя, выход 12 первого операнда блока 3 формирователя кратных, вход 13 второго операнда блока 3 формирования кратных, вход 14 выходного основания блока 3 формирования кратных, вход 15 установки блока 3 формирования кратных,, вход 16 первых импульсов-блока 3 формирования кратных, вход 17 вторых импульсов блока 3 формирования кратных, вход 18 блокировки блока 3 формирования кратных, выход 19 кратного блока 3 формирования кратных, выход 20 синхронизации блока 3 формирования кратных, выход 21 обнуления блока 3 формирования кратных, вход 22 меры блока 4 формирования признаков, первый, второй и третий тактовые входы 23-25 блока 4 формирования признаков, первый, второй и третий входы 26-28 установки блока 4 формирования признаков, вход 29 обнуления

5 0 5

5

0

5

0

5

блока 4 формирования признаков, вход 30 блокировки блока 4 формирования признаков, вход 31 переноса блока 4 формирования признаков, последовательный выход 32 меры блока 4 формирования признаков, последовательный выход 33 преобразуемого кода блока 4 формирования признаков, последователь ний выход 34 выходного основания блока 4 формирования признаков, выход 35 признака кратного блока 4 формирования признаков,выход 36 признака обнуления блока 4 формирования признаков,выход 37 признака переполнения блока 4 формирова- -ния признаков, выход 38 признака окончания преобразования, блока 4 формирования признаков, выход 39 блокировки блока 4 формирования признаков, вход) 40 признака обнуления блока 4 формирования признаков, вход 41 операнда блока 5 суммирования, вход 42 кода выходного основания блока 5 суммирования, тактовый вход 43 блока 5 суммирования, первый, второй, третий и четвертый входы 44-47 установки блока. 5 суммирования, выход 48 переноса блока 5 суммирования, выход 49 при- ; знака обнуления блока 5 суммирования, вход 50 признака кратного блока 6 управления, вход 51 признака окончания блока 6 управления, вход 52 признака обнуления.блока 6 управления, вход 53 синхронизации блока 6 управления, выход 54 первых импульсов блока 6 управления, выход 55 вторых импульсов блока 6 управления, выход 56 третьих импульсов блока 6 управления, первый, второй, третий, четвертый и пятый выходы 57-61 сигналов установки блока 6 управления и выход 62 тактового сигнала блока 6 управления

Блок 3 формирования кратных (фиг.2) содержит умножитель 63, три сумматора 64-66, счетчик 67 импульсов, четыре группы элементов 68-71 памяти, три коммутатора 72-74, группу элементов 75 запрета, группу элементов НЕ 76, элемент ИЛИ-НЕ 77, элемент ИЛИ 78 и элемент 79 запрета.

Блок 4 формирования признаков фиг.З) содержит три последовательно-параллельных регистра 8Q-82, два статических регистра 83 и 84, триггер 85, три элемента ИЛИ-НЕ 86-88, элемент И 89, элемент И-ИЛИ 90.. Блок 5 суммирования (фиг«4) содержит два сумматора 91 и 92, коммутатор 93,

51

триггер 94, регистр 95 смещаемой записи, распределитель 96, выходной последовательно-параллельный регистр 97, элемент ИЛИ 98 и группу элементов НЕ 99.

Блок 6 управления (фиг.5) содержит управляемый распределитель 100 импульсов, D-триггер 101, три IK- триггера 102-104, одновибратор 105, элемент ИЛИ 106, генератор 107 тактовых импульсов, тактовый вход 108 управляемого распределителя 100 им- ггульсов, вход 109 запуска, вход ПО разрешения включения, вход 111 синхронизации управляемого распределителя 100 импульсов, вход 112 признака кратнрго управляемого распределителя 100 импульсов, вход 113 признак обнуления управляемого распределителя 100 импульсов, выход 114 первого управляемого распределителя 100 импульсов, выход 115 второго импульса, выход 116 третьего импульса управляемого распределителя 100 импульсов выход 1 1 7 сигнала установки и выход 118 сигнала управления управляемого распределителя 100 импульсов.

Управляемый распределитель 100 импульсов (фиг.6) содержит три триггера 119-121, пять элементов ИЛИ 122- 126, четыре элемента И 127-130, первый элемент 131 запрета, пятый элемент И 132, второй и третий элементы 133 и 134 запретао

Последовательно-параллельный регистр 80 (81,82,97) (фиг.) имее- параллельный вход 135, вход 136 разрешения параллельной записи, тактовый вход 137, вход 138 установки в О, последовательный выход 139 и параллельный выход 140 последовательно-параллельного регистра и содержит в каждом из m разрядов.(т - количество r-ичных разрядов) п двоичных разрядов, а в каждом двоичном разряде триггер 141, элемент ИЛИ 142, элемент И 143 и элемент 144 запрета.

Регистр 95 смещаемой записи (фиг.8) имеет информационный вход 145, тактовый вход 146, вход 147 установки в О,, вход 148 разрешения записи и выход 149 о Регистр 95 смещаемой записи содержит в каждом r-ичном разряде п триггеров 150 и п элементов И-ИЛИ 151,,

Преобразователь кода работает, следующим образом.

4016

Преобразователь кода может осуществлять преобразование любого произвольного Р-ичного кода с любым натуральным значением основания каждого из разрядов в любой произвольный г-ичный код с любым натуральным значением каждого разряда0 Преобразование осуществляется по следующей меЮ тодике,, Для каждого Р-пчного разряда преобразуемого кода определяется величина единицы данного Р-нчного разряда, выраженная величинами разрядов выходного r-ичного кода, т„е,

15 мера данного разряда Полученные меры записываются в блок постоянной памяти. Затем каждая мера умножается на величину соответствующего ей Р-ичного разряда преобразуемого кода В ре20 зультате умножения для каждого Р-ич- ного разряда образуются соответствующие кратные. Полученные кратные последовательно суммируются Сумма кратных является результатом преобразова25 ния, выраженным в r-ичном выходном коде.

В исходном состоянии триггер 102 (фиг.5) находится в 0м. На вход 7 подается сигнал запуска, на входы уста30 новки статических регистров 83 и 84 (фиг.З) подаются соответственно значения преобразуемого кода и оснований разрядов выходного кода (входы установки статических регистров 83 и 84

25 не показаны), На вход 10 подается код начального адреса, определяющий адрес первой меры в блоке 1 памяти. Первым после подачи сигнала Запуск отрицательным фронтом тактового им40 пульса включается в 1 триггер 102, на выходе 9 появляется сигнал О, разрешающий преобразование;, Отрицательным фронтом следующего тактового , импульса включается в 1 триггер 103

45 и на выходе 57 блока 6 управления появляется первый импульс установки (У1), по которому в счетчик 2 записывается код начального адреса, в регистры 83 и 84 записываются преобразуе50 мый код и основания разрядов выходного кода соответственно, в блоке 3 формирования кратных (фиг,2) устанавливается в О счетчик 67, элементы 68 и 69 памяти, в блоке 5 сумми55 рования (фиг.4) устанавливаются в

О выходной регистр 97. Преобразователь подготовлен к началу преобразования. Отрицательным фронтом второго тактового импульса отключается первый

716

импульс установки (У1), а на выходе 58 блока 6 управления появляется второй импульс установки (У2). В блоке 4 формирования признаков (фиг.З) по второму импульсу установки в ре- гистр 81 записывается преобразуемый код из статического регистра 83, в регистр 82 записываются основания разрядов выходного кода из статичес- кого регистра 84, устанавливается в О триггер 85. В блоке 5 суммирования по второму импульсу установки устанавливаются в О распределитель 96, триггер 94,

Регистр 95 смещаемой записи устанавливается в О импульсом с выхода 61 блока 6 управления, на котором вырабатывается импульс после прохождения отрицательного фронта второго импульса установки У2 и третьего импульса (ИЗ)„ Импульсом с выхода од- новибратора 105 производится также запись значения меры в регистр 80 блока 4 формирования признаков с вы- хода блока 1 памяти„ Второй импульс установки У2) подается также на вход 109 управляемого распределителя 100 импульсов.. Отрицательным фронтом тактового импульса, которым отключается второй импульс установки (У2), включается в единицу триггер 119 (Т1), управляемого распределителя 100 импульсов (фиг.6). В этот момент признак кратного (ПК) на выходе 35 блока 4, признак выходного основания (Иг) на выходе 36 блока 4, признак окончания (ПО) на выходе 38 блока 4 и признак переполнения (ПП) на выходе 37 блока 4 отсутствуют и равны нулю. На вход, сумматора 66 блока 3 формирования кратных подается основание первого разряда выходного кода с выхода регистра 82 блока 4

На входы 12 и 13 блока 3 подают- ся соответственно первый разряд меры с выхода 32 блока 4 и первый разряд преобразуемого кода с выхода 33 блока 4„ На выходе умножителя 63 блока (фиг.2) образуется произведение количества двоичных единиц первого разряда меры на количество двоичных единиц первого разряда преобразуемого кода, выраженное в двоичном коде. Полученное произведение подается на вход сумматора 64, на другой вход ко- торого подается значение переносов предыдущего цикла с выходов элементов 68 памяти группы, в данном слу

8

5 Q

, 5

0

0

чае нули. Полученная сумма с выхода сумматора 64 подается на один вход сумматора 65, на второй вход которого подается инверсное значение основания первого разряда выходного кода, на вход переноса сумматора 65 подается Лог.1. На выходе сумматора 65 образуется разность между значением кода с выхода сумматора 64 и основанием первого разряда выходного кода. Если эта разность больше или равна нулю, то на выходе переноса сумматора 65 единица и сигнал СИНХР на выходе блока 20, блока 3 равен единице. Если эта разность меньше нуля, то на выходе переноса сумматора 65 нуль и сигнал СИНХР на выходе 20, блока 3 равен нулю. Сигнал СИНХР подается на вход 53 блока 6 управления и при значении равном единице, поддерживает триггер 119 (фиго6) во включенном состоянии. Если сигнал СИНХР становится равным нулю, то следующим тактом триггер 119 (Т1) отключается, а включается триггер 120 (Т2). При включенном триггере 119 (XI) на выходе 54 блока 6 управления образуются первые импульсы (И1), которые подаются на вход 16 блока 3. Если сигнал СИНХР равен единице, то каждым импульсом (И1) счетчик 67 увеличивает свое значение на единицу, а элементы 68 и 71 памяти группы находятся в состоянии предыдущего значения.

В элементах 69 памяти группы накапливается с каждым импульсом И1 сумма основания данного разряда выходного кода. В элементы 70 памяти группы каждым импульсом (И1) записывается значение с выхода сумматора 65, Как только на выходе переноса сумматора 65 появляется нуль, то значит сумма количества оснований данного разряда выходного кода превысила сумму произведения с выхода умножителя 63 и переносов предыдущего цикла, получаемую на выходе сумматора 64. В счетчике 67 в этот момент записано количество единиц, равное количеству оснований данного разряда, выходного кода, содержащихся в сумме произведения с выхода умножителя 63 и переносов предыдущего цикла с выхода элементов памяти 68, В элементах 70 памяти группы записана разность этих значений, полученная в предыдущем такте на выходе сумматора 65. Сигнал СИНХР равный нулю, подается на входы элементов И 130 и запрета 131 (фиг. 6) управляемого, распределителя импульсов. На входе 16 блока 3 образуется последний импульс (И1) данного цикла. По этому импульсу счетчик 67 будет в состоянии хранения, в элементы 68 памяти группы переписывается количество переносов в следующий разряд из счетчика 67. В элементы 71 из элементов 70 памяти группы переписывается значение полученного остатка данного разряда.

Одновременно с этим отключается триггер 119 (Т1) и включается триггер 120 (Т2) управляемого распределителя 100. На выходе 19 блока 3 появляется значение данного разряда получаемого кратного, которое подается на вход 41 блока 5 суммирования (фиг.4). Полученное значение данного r-ичного разряда суммируется на сумматоре 91 со значением этого же по номеру разряда, хранящегося в выходном регистре 97. На сумматоре 92 из полученной суммы производится вычитание основания данного разряда выходного кода, а на коммутаторе 93 выбирается значение с выхода сумматора 91 , если сумма меньше основания, или значение с выхода сумматора 92, если сумма больше или равна основанию. Полученное значение данного r-ичного разряда подается с выхода коммутатора 9 на вход регистра 95 смещаемой записи В момент появления следующего тактового импульса на выходе 55 блока 6 управления появляется второй импульс (И2), который подается на вход 17 блока 3, вход 24 блока 4 и вход 43 блока 5. По второму импульсу (И2) в блоке 3 устанавливаются в О счетчик 67, элементы 69 памяти группы, в блоке 4 отрицательным фронтом второго импульса производится сдвиг содержимого в регистрах 80 и 82 (меры и выходных оснований}, в триггер 85 записывается значение ПК„ В блоке 5 суммирования по отрицательному фронт второго импульса происходит запись в первый разряд регистра 95 смещаемой записи кода с выхода коммутатора 93, сдвиг на один разряд распределителя 96, который разрешает запись в следующий разряд регистра 95 смещаемой записи, сдвиг на один разряд в сторону младших разрядов содержимого выходного регистра 97 и запись значения переноса с выхода пере

5

0

5

0

5

0

5

0

5

носа сумматора 92 в триггер 94. Таким образом серия первых импульсов (И1) формирует один разряд кратного.

Последним импульсом серии значение этого разряда передается на вход блока 5 суммирования. По второму импульсу (И2) в блоке 5 производится суммирование этого разряда с соответствующим разрядом полученной в предыдущем цикле суммы и запись полученного значения в регистр 95 смещаемой записи, в котором формируется новая сумма. После второго импульса на вход 12 блока 3 подается следующий разряд меры, а на вход 14 подается следующий разряд основания выходного кода. Если после отрицательного фронта второго импульса (И2) предыдущего цикла на выходе 35 блока 4 не возникает ПК9 означающий окончание получения одного кратного, то О с выхода 35 блока 4 подается на вход элемента 133 запрета управляемого распределителя 100 (фиг.6) и разрешает включение следующим тактом триггера 119 (Т) и отключение триггера 120 (Т2). Начинается цикл образования следующего разряда получаемого кратного

Аналогично предыдущему циклу подается серия первых импульсов (И1), продолжающаяся до появления сигнала СННХР, равного нулю, на выходе переноса сумматора 65. Если сигнал СИНХР, равный нулю, появляется до подачи первых импульсов, то на вход элементов 71 памяти группы подключается через коммутаторы 73 и 74 выход сумматора 64, так как на выходе переноса счетчика 67 будет единица, означающая наличие всех нулей в счетчике 67. В этом случае первым по счету импульсом (И1) полученный код данного выходного разряда записывается в элементы 71 памяти группы и подается на вход 41 блока 5. Триггер 119 (Т1) отключается в О, триггер 120 (Т2) включается в 1. Вырабатывается второй импульс (И2), по которому производятся действия аналогично предыдущему циклу о ,

Если по отрицательному фронту второго импульса предыдущего цикла ПК на выходе 35 блока 4 равен нулю, то снова появляется серия первых импульсов (И1)о Если на выходе 35 блока 4 появляется ПК, равный единице, то это

означает, что во всех разрядах регистра 80 бпока 4, кроме младшего, будут нули. В элементах 68 памяти группы будут также все нули Для этого выходы 2(l-n)...m(l-n) регистра 80 соединены с выходами элемента ИЛИ- НЕ 86 (фиг.З). В зависимости от соотношения величин разрядов преобразуемого кода и выходных оснований ПК может появляться сразу либо дважды, В случае двойного появления после первого появления ПК по отрицательному фронту второго импульса(И2) снова включается триггер 119 (Tl) и отключается триггер 120 (Т2), появляется серия первых импульсов (И1) на выходе 54 блока 6 управления При обработке последнего разряда меры по последнему импульсу серии первых импульсов (И1) в элементы 68 памяти группы могут быть записаны переносы в следующий разряде В этом случае ПК на выходе 35 блока 4 снова будет равен нулю при возникновении второго импульса (К2} на выходе 55 блока 6 управления.

Чередование первых (И1) и вторых (И2) импульсов будет до тех пор, пока в элементах 68 памяти группы по последнему импульсу серии первых импульсов (Ш) не будут записаны все нули. Тогда вторично появляется ПК на выходе 35 блока 4 и по отрицательному фронту второго импульса (И2) включается триггер 85 блока 4, блокирующий выход 19 блока 3 после получения очередного кратного, и могут возникнуть два случая. В первом случае, когда Пг на выходе 36 блока 4 равен нулю, триггер 120 (Т2) распределителя 100 - в состоянии 1, продолжается выдача серии вторых импульсов (И2) по выходу 55 блока 6 управления и формирование очередной суммы кратных в регистре 95 смещаемой записи о Во втором случае, когда Пг становится равен единице, следующим тактом включается триггер 121 (ТЗ), а триггер (И2) отключается о Появляется третий импульс (ИЗ) на выходе 56 блока 6 управления.

По включению триггера 121 (ТЗ) производится счет в счетчике 2 адреса, по отключению триггера 121 (ТЗ) - сдвиг преобразуемого кода в регистре 81 на один Р-ичный разряд. По третьему импульсу (ИЗ) в регистр 82 из статического регистра 84 записываются

0

5

0

5

0

5

0

5

0

5

основания выходного кода, устанавливается в О триггер 85 блокировки, который включается в 1 импульсом (И2 при наличии ПК„ В блоке 5 суммирования в выходной регистр 97 записы- вывается код новой суммы кратных из регистра 95 смещаемой записи, устанавливаются в О распределитель 96 и триггер 94. По импульсу одновиб- ратора 105 блока 6, вырабатываемому после отрицательного фронта третьего импульса, в регистр 80 блока 4 записывается значение следующей меры из блока 1 памяти, в блоке 5 устанавливается в О11 регистр 95 смещаемой записи. Преобразователь подготовлен к обработке следующего кратного-.

При включенном триггере 121 ТЗ) отрицательным фронтом очередного такта включается триггер 119 (Т1) и отключается триггер 121 (ТЗ). Начинается цикл обработки следующего кратного, который аналогичен предыдущему. После цикла обработки последнего разряда преобразуемого кода по отрицательному фронту третьего импульса производится сдвиг преобразуемого кода в регистре 8J. В регистре 81 будут все нули и на выходе элемента ИЛИ-НЕ 87 появляется ПО, который подается на К-вход триггера 102 блока 6 управления. Отрицательным фронтом следующего такта триггер 102 отключается, в выходной регистр 97 по третьему импульсу (ИЗ) записывается преобразованный код с выходов регистра 95 смещаемой записи. Преобразование оконченоо

Для правильного преобразования должно соблюдаться соответствие масштабов преобразуемого и выходного кодов. В случае, если масштабы не соблюдены, на выходе 37 блока 4 появляется ПП.

Такая ситуация может возникнуть в следующих случаях. На выходе регистра 82 блока 4 появляется код оснований О или 1 при отсутствии ПК на выходе 35 блока 4„ Анализ на отсутствие кодов О или 1, т.е. наличие Пг, осуществляется с помощью элемента ИЛИ-НЕ 88. Расматриваемая ситуация означает, что есть несоответствие масштабов и мера превышает величину выходного кода, либо в коде выходных оснований есть коды разрядов, содержащие О или 1. ПЕ появляется на выходе элемента ИЛИ-НЕ 88 в тот

момент, когда выходной регистр 97 не является обнуленным после очередного второго импульса (И2). Данная ситуация означает, что очередная сумма кратных не укладывается в масштаб оснований выходного кода,. Обнуление выходного регистра 97 определяется с помощью элемента ИЛИ 98, на выходе которого в этом случае образуется признак выходного регистра (ПВ)с fir появляется в тот момент, когда выходной регистр 97 обнулен и есть перенос (е) в следующий разряд, запоминаемый в триггере 94 блока 5. Данный перенос подается на вход 3 блока 4. В рассмотренных случаях на выходе 37 блока 4 появляется ПП,

Регистр 95 смещаемой записи (фиг.8) содержит в каждом r-ичном разряде триггер 150 и элемент И-ИЛИ 151. Регистр 95 позволяет производить выборочную запись в соответствующий разряд по сигналам разрешения с выходов распределителя 96 блока 5, подаваемых на входы 148. При отсутствии данного сигнала соответствующие разряды регистра 95 находятся в состоянии хранения. Запись производится отрицательным фронтом второго импульса (И2) по входу 146, а установка в О - импульсом одновибратора 105 по входу 147. Параллельная запись в регистры 80г-82 и 97 (фиг.7) по входам 135 производится сигналом разрешения записи на входе 136. Сдвиг информации в регистрах производится отрицательным фронтом второго импульса (И2) по входу 137. Обнуление регистров производится сигнапом установки по входу 138о

Формула изобретения

1. Преобразователь кода, содержащий блок постоянной памяти, счетчик адреса, блок суммирования и блок управления, причем вход запуска п ре- образователя соединен с входом за10

15

20

25

30

35

40

45

разряде в произвольный код с другим основанием в каждом разряде,он содержит блок формирования кратных и блок формирования признаков, причем вход адреса преобразователя соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом блока постоянной памяти, выход которого соединен с входом меры блока формирования признаков, последовательный выход меры и последовательный выход преобразуемого кода которого соединены соответственно с входами первого и второго операндов блока формирования кратных, выход кратного которого соединен с входом операнда блока суммирования, выходы переноса и признака обнуления которого соединены соответственно с входами переноса и признака обнуления блока формирования признаков, выход признака переполнения которого является выходок признака переполнения преобразователя, вход установки которого соединен с установленным , входом блока управления, первый выход сигналов установки которого соединен с входом разрешения записи счетчика адреса, с первым тактовым входом блока формирования признаков, с входом установи блока формирования кратных, выход синхронизации которого соединен с входом синхронизации блока управления, второй и третий выходы сигналов установки коюрого соединены соответственно с первым входом установки и с входом блокировки блока формирования признаков, выходы признака кратного, признака окончания преобразования и признака обнуления выходного основания которого соединены соответственно с входами признака кратного, признака окончания и признака обнуления блока управления, четвертый выход сигналов установки которого соединен с первым входом установки блока суммирования, второй вход установки которого соедипуска блока управления, выход регист- 50 нен с вторым входом установки блока

формирования признаков и с пятым вы- - ходом сигналов установки блока управления, выходы первых, вторых и трерации которого является выходом регистрации преобразователя, выход тактового сигнала блока управления соединен со счетным входом счетчика адреса, о тличающий ся тем, что, с целью расширения функциональных возможностей за счет преобразования произвольного Р-ичного кода с любым основанием в каждом

55

тьих импульсов которого соединены соответственно с входом первых импульсов блока формирования кратных, с объединенными вторым тактовым входом блока формирования признаков, входом вторых импульсов блока формирования

5

0

5

0

5

разряде в произвольный код с другим основанием в каждом разряде,он содержит блок формирования кратных и блок формирования признаков, причем вход адреса преобразователя соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом блока постоянной памяти, выход которого соединен с входом меры блока формирования признаков, последовательный выход меры и последовательный выход преобразуемого кода которого соединены соответственно с входами первого и второго операндов блока формирования кратных, выход кратного которого соединен с входом операнда блока суммирования, выходы переноса и признака обнуления которого соединены соответственно с входами переноса и признака обнуления блока формирования признаков, выход признака переполнения которого является выходок признака переполнения преобразователя, вход установки которого соединен с установленным , входом блока управления, первый выход сигналов установки которого соединен с входом разрешения записи счетчика адреса, с первым тактовым входом блока формирования признаков, с входом установи блока формирования кратных, выход синхронизации которого соединен с входом синхронизации блока управления, второй и третий выходы сигналов установки коюрого соединены соответственно с первым входом установки и с входом блокировки блока формирования признаков, выходы признака кратного, признака окончания преобразования и признака обнуления выходного основания которого соединены соответственно с входами признака кратного, признака окончания и признака обнуления блока управления, четвертый выход сигналов установки которого соединен с первым входом установки блока суммирования, второй вход установки которого соеди

тьих импульсов которого соединены соответственно с входом первых импульсов блока формирования кратных, с объединенными вторым тактовым входом блока формирования признаков, входом вторых импульсов блока формирования

кратных и тактовым входом блока суммирования , с третьим входом установки блока суммирования, четвертый вход установки которого соединен с первым выходом сигналов установки блока управления, выход тактового сигнала и четвертый выход сигналов установки которого соединены соответственно с третьим тактовым вхо- дом и с третьим входом установки блока формирования признаков, вход обнуления которого соединен с выходом обнуления блока формирования кратных, вход блокировки и вход выходного основания: которого соединены соот- вественно с выходом блокировки блока формирования признаков и с объединенными входами кода выходного основания блока суммирования и последова- тельным выходом выходного основания блока формирования признаков..

2. Преобразователь по п. отличающийся тем, что блок формирования кратных содержит умножи- тель, три сумматора, счетчик импульсов, четыре группы элементов памяти, три коммутатора, группу элементов запрета, группу элементов НЕ, элемент ИЛИ-НЕ, элемент ИЛИ и элемент запрета, причем входы первого и второго операндов блока формирования кратных соединены с входами первого и второго сомножителей умножителя, выход которого соединен с входом пер- вого слагаемого третьего сумматора, входы разрядов входа второго слагаемого которого соединены с соответствующими входами элемента ИЛИ-НЕ, с выходами элементов памяти первой группы и с входами разрядов первого информационного входа первого коммутатора, BTOpqu информационный вход которого соединен с разрядным выходом счетчика импульсов, вход установ- ки в О которого соединен с выходом элемента ИЛИ и с входами установки в / 0 элементов памяти второй группы, вход выполненного основания блока формирования кратных и выходы эле- ментов памяти второй группы соединены соответственно с входом первого слагаемого и входами разрядов входа второго слагаемого первого сумматора, выходы разрядов выхода которого сое- динены с входами соответствующих элементов НЕ группы и с информационными входами элементов памяти второй группы, выходы элементов НЕ группы соединены с входами разрядов входа первого слагаемого второго сумматора, вход переноса соединен с входом логической единицы преобразователя, входы переносов первого и третьего сумматоров соединены с входом логического нуля преобразователя, выходы разрядов первого коммутатора соединены с информационными входами соответствующих элементов памяти первой группы, выхода разрядов выхода второго сумматора соединены с информационными входами соответствующих элементов памяти третьей группы, выходы которых соединены с входами разрядов первого информационного входа третьего коммутатора, второй информационный вход которого соединен с входом второго слагаемого второго сумматора и с выходом третьего сумматора, выход переноса счетчика импульсов соединен с информационным входом элемента запрета, выход которого соединен с управляющим входом третьего коммутатора, выход которого соединен с первым информационным входом второго коммутатора, выходы разрядов выхода которого соединены с информационными входами соответствующих элементов памяти четвертой группы, выходы которых соединены с входами разрядов второго информационного входа второго коммутатора и с информационными входами соответствующих элементов запрета группы, управляющие входы которых соединены с входом блокировки блока формирования кратных, а выходы являются выходами разрядов выхода кратного блока формирования кратных, выход синхронизации блока формирования кратных соединен с входом разрешения счетчика импульсов, с управляющим входом элемента запрета, с управляющими входами первого и второго коммутаторов и с выходом переноса второго сумматора, вход установки блока формирования кратных соединен с входами установки в О элементов памяти первой группы и с первым входом элемента ИЛИ, второй вход которого соединен с входом вторых импульсов блока формирования кратных, вход первых импульсов которого соединен с тактовыми входами элементов памяти с первой по четвертую групп и со счетным входом счетчика импульсов, выход элемента ИЛИ-НЕ является выходом обнуления блока формирования кратных.

1716

3. Преобразователь по п. 1, о т - личающийся тем, что блок формирования признаков содержит три последовательно-параллельных регисг- ра4 два статических регистра, триггер, три элемента ИЛИ-НЕ, элемент И и элемент И-ИЛИ, причем первый тактовый вход блока формирования признаков соединен с входами разрешения записи первого и второго статических регистров, третий тактовый вход блока формирования признаков соединен с тактовым входом первого последова- ,- тельно-параллельного регистра, вход меры блока формирования признаков соединен с параллельным входом второго последовательно-параллельного регистра, тактовый вход которого соединен с тактовым входом третьего последовательно-параллельного регистра, с входом разрешения записи триггера и с вторым тактовым входом блока формирования признаков, выход первого статического регистра соединен с параллельным входом первого последова- тепьно-параллельного регистра, выход второго статического регистра соеди- нен с параллельным входом третьего последовательно-параллельного регистра, входы разрешения записи первого и второго последовательно-параллель- ных регистров соединены соответственно с первым и вторым входами установки блока формирования признаков, третий вход установки которого соединен с входом разрешения записи третьего последовательно-параллельного регистра и с входом установки в О триггера, входы установки в О с первого по третий последовательно-параллельных регистров соединены с входом логического нуля преобразователя, последовательные выходы первого и второго последовательно-параллельных регистров являются последовательными выходами соответственно преобразуемого кода и меры блока формирования признаков, вход блокировки которого соединен с первыми входами первого, второго и третьего элементов ИЛИ-НЕ, выходы разрядов параллельного выхода первого последовательно-параллельного регистра соединены соответственно с входами, кроме первого, первого элемента ИЛИ-НЕ, выход которого является выходом признака окончания преобразования блока формирования признаков, выходы r-ичных разрядов, крс40118

МР первого параллельного выхода, второго последовательно-параллельного регистра соединены с соответствующими входами второго элемента ИЛИ-НЕ, выход которого и вход обнуления блока формирования признаков соединены соответственно с входами элемента И, выход которого соединен с информационQ ным входом триггера и является выходом признака кратного блока формирования признаков, последовательный выход выходного основания которого соединен с последовательным выходом третьего

последовательно-параллельного регистра, выходы с второго по n-й двоичных разрядов/г - основание выходного кода, п - количество двоичных разрядов, необходимых для представления г ичноQ го разряда последовательного выхода которого соединены с соответствующими входами третьего элемента ИЛИ-НЕ, выход которого является выходом признака обнуления выходного основания б ю5 ка (Ъормирования признаков, выход блокировки которого соединен с инверсным выходом триггера, информационный вход которого соединен с первым инверсным входом первой группы элемента И-ИЛИ,

Q выход которого является выходом признака переполнения блока формирования признаков, вход признака обнуления которого соединен с первым входом второй группы и с первым инверсным входом третьей группы элемента И-ИЛИ, вторые входы первой, второй и третьей групп которого соединены с выходом третьего элемента ИЛИ-НЕ, третий вход третьей группы элемента

« И-ИЛИ соединен с входом переноса блока формирования признаков

4. Преобразователь по п. отличающийся тем, что блок суммирования содержит два сумматора,

коммутатор, триггер, регистр смещаемой записи, распределитель, выходной последовательно-параллельный регистр, элемент ИЛИ и группу элементов НЕ, причем вход операнда блока суммирования соединен с входом первого слагаемого первого сумматора, вход переноса которого соединен с выходом триггера и является выходом переноса блока суммирования четвертый вход установки которого соединен с входом установки в О выходного последовательно-параллельного регистра, выходы разрядов параллельного выхода которого соединены с соответствующими

5

19

входами элемента ИЛИ, выход которого является выходом признака обнуления блока суммирования, тактовый вход которого соединен с тактовыми входами выходного последовательно-параллельного регистра, регистра смещаемой записи, распределителя и с входом разрешения записи триггера, вход установки в О которого соединен с входом установки в О распределителя и с первым входом установки блока суммирования, второй и третий входы установки которого соединены соответственно с входом установки в О регистра смещаемой записи и с входом разрешения параллельной записи выходного последовательно-параллельного регистра, последовательный выход которого соединен с входом второго слагаемого первого сумматора, входы разрядов входа кода выходного основания блока суммирования соединены через соответствующие элементы НЕ группы с входами разрядов входа первого слагаемого второго сумматора, вход второго слагаемого которого соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом второго сумматора, вход переноса которого соединен с входом логической единицы преобразователя, выход переноса второго сумматора соединен с информационным входом триггера и с управляющим входом коммутатора, выход которого соединен с информационным входом регистра смещаемой записи, выход которого соединен с параллельным входом выходного последовательно-параллельного регистра, выход распределителя соединен с входом разрешения записи регистра смещаемой записи,

5. Преобразователь по п. отличающийся тем, что блок управления содержит управляемый распределитель импульсов, D-триггер, три IK-триггера, одновибратор, элемент ИЛИ и генератор тактовых импульсов, причем первый выход сигналов установки блока управления соединен с информационным входом D-триггера, с входом разрешения записи первого IK-триггера и с выходом второго IK-триггера, выход В-триггера соеди- нен с первым входом элемента ИЛИ, с входом запуска управляемого распределителя импульсов и является вторым вь

1940120

ходом сигналов установки блока управления, третий и пятый выходы сигналов установки которого соединены соответственно с выходами элемента ИЛИ и одновибратора, вход которого соединен с выходом сигнала установки управляемого распределителя импульсов и является четвертым выходом сигналов установки блока управления, выходы первых, вторых и третьих импульсов которого являются соответственно выходами первого, второго и третьего импульсов управляемого распредели10

теля импульсов, тактовый вход которого соединен с выходом генератора тактовых импульсов, с входами разрешения записи второго и третьего 1К-триг- геров и D-триггера, вход установки

О которого соединен с входом разрешения включения управляемого распределителя импульсов, с входами установки в О первого и второго 1К-триг- геров, с инверсным выходом третьего

IK-триггера и является выходом регистрации блока управления, вход запуска, установленный вход и вход признака окончания которого соединены соответственно с I-входом, входом установки в О и К-входом третьего IK-триггера, инверсный выход первого IK-триггера соединен с вторым входом элемента ИЛИ, с I-входом второго 1К-триггера, с I- и К-входами первого IK-триггера, К-вход второго 1К-триг.гера соединен с входом логической

единицы преобразователя, входы синхронизации, признака кратного и признака обнуления блока управления соединены с соответствующими входами управляемого распределителя импульсов, выход сигнала управления которого является выходом тактового сигнала блока управления.

6. Преобразователь по пп. 1 и 5, отличающийся тем, что управляемый распределитель импульсов содержит три триггера, пять элементов ИЛИ, пять элементов И и три элемента запрета, причем выходы с первого по третий элементов И являются соответственно выходами первого, второго и третьего импульсов управляемого распределителя импульсов, -вход синхронизации которого соединен с первым входом четвертого элемента И и с управляющим входом первого элемента запрета, выход первого триггера соеди21161

нен с вторым входом четвертого эпе- мента И, с информационным входом первого элемента запрета и с первым входом первого элемента И, выход четвертого элемента И соединен с первым уходом первого элемента ИЛИ, выход которого соединен с информационным входом первого триггера, вход установки в 0|Т которого соединен с входами установки в О второго и третьего триггеров и является входом разрешения включения управляемого распределителя импульсов, выход первого элемента запрета соединен с первым входом второго элемента ИЛИ, вьрсод которого соединен с информационным входом второго триггера, выход которого соединен с первыми входами пятого и второго элементов И, с информационным входом второго элемента запрета и с первым информационным входом третьего элемента запрета, выход которого соединен с вторым входом второго элемента ИЛИ, вход признака кратного управляемого распределителя импульсов соединен с вторым входом пятого элемента И, с управляющим входом второго элемента запрета и с вторым информационным входом третьего элемента запрета, управляющий вход которого соединен с входом признака обнуления управляемого распределителя импульсов и с третьим входом пятого эле- мента И, выход которого соединен с информационным входом третьего триггера, выход которого соединен с первыми входами третьего элемента И и четвертого элемента ИЛИ и является вы ходом сигнала управления управляемого распределителя импульсов, тактовый вход которого соединен с входами разрешения записи с первого по третий триггеров и с вторыми входами с первого по третий элементов И, вход за20

40122

пуска управляемого распределителя импульсов соединен с первым входом пятого элемента РЫИ и с первым входом третьего элемента ИЛИ, выход которого - соединен с вторым входом первого элемента ИЛИ, выход второго элемента запрета соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом третьего элемента ИЛИ, выход третьего элемента И соединен с вторым входом пятого элемента ИЛИ, выход которого является выходам сигнала установки управляемо- . г го распределителя импульсов.

7, Преобразователь по пп. 1 и 4, отличающийся тем, что регистр смещаемой записи содержит в каждом r-ичном разряде п триггеров и п элементов И-ИЛИ, причем входы разрядов информационного входа регистра смещаемой записи соединены соответственно с первыми входами первых групп элементов И-ИЛИ разрядов регистра смещаемой записи, выходы которых соединены с информационными входами триг- геров соответствующих разрядов регистра смещаемой записи, выходы которых является выходами разрядов выхода

30 регистра смещаемой записи и соединены с первыми входами вторых групп элементов И-ИЛИ соответствующих разрядов регистра смещаемой записи, вторые входы первых групп и вторые инверсные

35 входы вторых групп элементов И-ИЛИ г-ичных разрядов регистра смещаемой записи объединены и подключены к входам соответствующих разрядов входа разрешения записи регистра смещаемой

40 записи, тактовый вход и вход установки в О которого соединены соответственно с входами разрешения записи и с входами установки в О триггеров разрядов регистра смещаемой записи.

5

Or

7

ч

f -if

См

--a

S - OQ «J4

bo

tv

to

QO

Т

«57

/

Фиг. 8

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Устройство для определения заданной ординаты корреляционной функции | 1990 |

|

SU1777152A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

Преобразователь кода относится к информационно-измерительной технике. Целью изобретения является pjc- ширение функциональных возможностей за счет преобразования произвольного Р-ичного кода с любым основанием в каждом разряде в произвольный код : другим основанием в каждом разряде, Преобразоватеть кода содержит блок 1 постоянной памяти, счетчик 2 адреса, блок 3 формирования кратных, блок 4 формирования признаков, блок 5 суммирования и блок 6 управления с соответствующими связями о В блоке постоянной памяти записаны меры для каждого Р-ичного разряда преобразуемого кода, выраженные в значениях выходного кода0 Для каждого разряда преобразуемого кода находится его отображение в значениях выходного кода путем умножения соответствующей меры на значение данного разряда. Полученные после умножения кратные суммируются, а результат суммирования /шляется искомым выходным кодом. 6 з. п, ф-ль:, 8 ил Ј (Л

| Преобразователь кодов | 1986 |

|

SU1381717A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-07—Публикация

1989-02-15—Подача