Изобретение относится к вычислительной технике и может быть использовано в ЭВМ, системах обработки информации инструментальных системах разработки.

Цель изобретения - расширение области применения путем расширения области адресации.

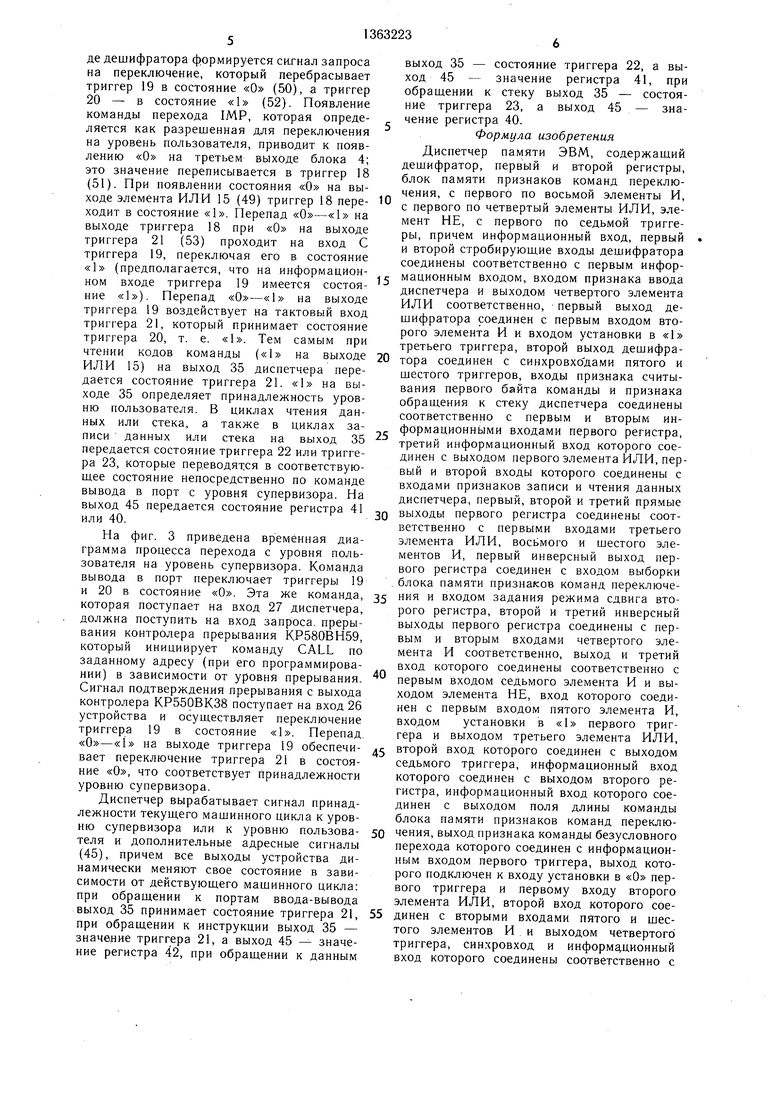

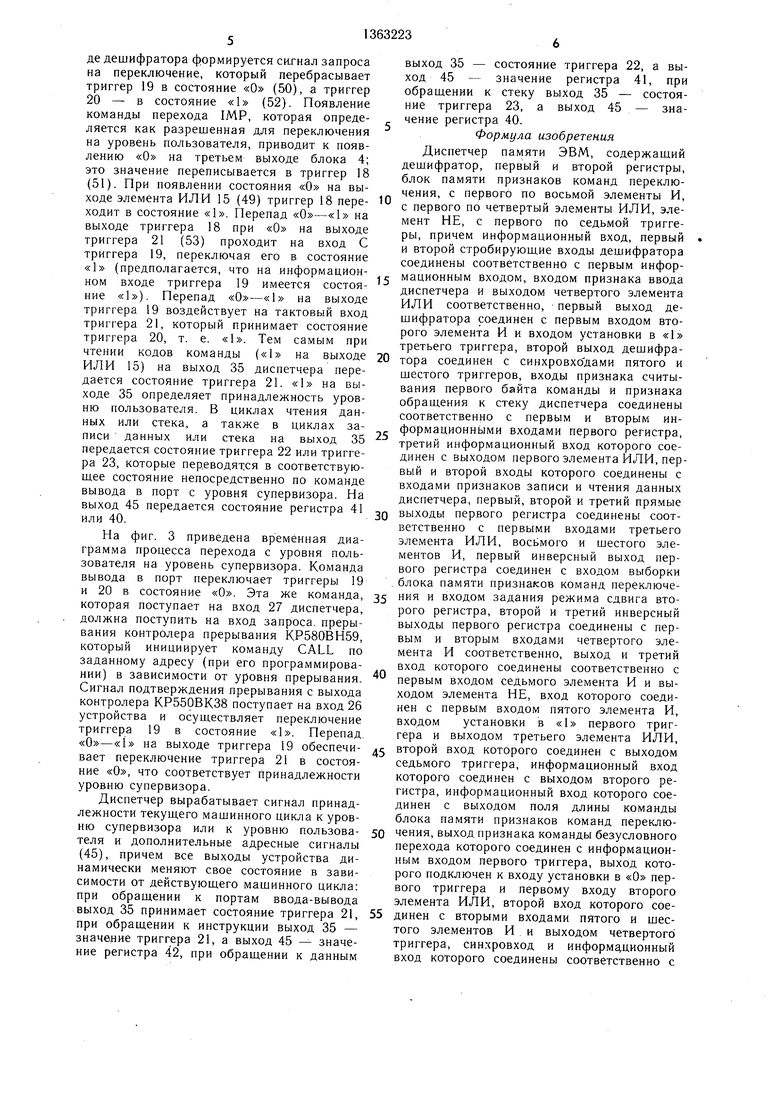

На фиг. 1 изображена блок-схема устройства; на фиг. 2 и 3 - временные диаграммы работы устройства.

Устройство содержит дешифратор 1, первый 2 и второй 3 регистры, блок 4 памяти признаков команд переключения уровней памяти, первый 5, второй 6, третий 7, четвертый 8, пятый 9, шестой 10, седьмой 11 и восьмой 12 элементы, первый 13, второй 14, третий 15 и четвертый 16 элементы ИЛИ, элемент НЕ 17, первый 18, второй 19 третий 20, четвертый 21, пятый 22, шестой 23 и седьмой 24 триггеры, вход 25 строби- рования данных диспетчера, вход 26 подтверждения прерывания диспетчера, первый вход 27 запроса переключения, вход 28 сброса, вход 29 признака ввода, первые информационные входы 30 диспетчера, вход 31 статуса диспетчера, вход 32 стробирования статуса, вход 33 синхронизации, вторые информационные входы 34 диспетчера, выход 35 уровня памяти, восьмой 36 триггер, девятый 37, десятый 38 и одиннадцатый 39 элементы И, первый 40, второй 41 и третий 42 буферные регистры, второй вход 43 запроса переключения, вход 44 блокировки диспетчера, информационные выходы 45 диспетчера, первый выход 46 регистра 2, выход 47 регистра 3, выход 48 триггера 24, выход 49 элемента ИЛИ 15, выход 50 триггера 19, выход 51 триггера 18, выход 52 триггера 20 и выход 53 триггера 21.

Третий разряд блока 4 определяет множество команд перехода,которое используется для инициирования перехода на уровень пользователя, в частности IMP, PCHL, CALL, RET. Однако этот набор команд можно расширить, изменив содержимое блока 4 памяти (определяется нулем В третьем разряде ПЗУ, записанным по адресу, соот- ветствуюш.ему коду команды).

Диспетчер предназначен для работы в составе микроЭВМ. При использовании микропроцессора КР580ИК80А для построения микроэвм диспетчер подключается следующим образом.

Вход 25 принимает инвертированный сигнал DBIN с выхода микропроцессора, вход 26 - сигнал INTA с выхода контролера КР580ВК38, вход 29 подключается к выходу 1OW контролера КР80ВК38, входы 30 - к адресным линиям процессора, вход 31 - к выводам данных микропроцессора, первый вход регистра 2 - к линии D5, второй - к линии D 2, первый вход элемента ИЛИ 13 - к линии D 4, а второй - к линии D6, вход 32 - к выводу STSTB тактового генератора

КР580ГФ24, вывод 33 - к выходу SYNC микропроцессора, вход 34 - к линиям DBO--DB7 контролера КР580ВК38, вход 27 к дешифратору выбора устройств вводавывода пользователя. Сигнал, поступающий на вход 27, подключается одновременно на вход запроса прерывания контролера прерываний КР580ВН59 непосредственно или через дешифратор, информационные

входы которого подключаются к информационным линиям процессора. Это одновременно обеспечивает запрос на переключение с уровня пользователя на уровень супервизора и инициирует прерывание, которое обеспечивает переход на уровень супервизора по требуемому адресу, определяемому уровнем прерывания. Сигнал подтверждения прерывания поступает на вход 26 диспетчера, обеспечивая переключение на уровень супервизора. Вход 28 подключается к инвертированному сигналу RES с выхода

0 тактового генератора КР580ГФ24. Вход 44 запрета можно подключить к потенциалу «1, если режим прямого доступа к памяти не используется. В противном случае этот сигнал вырабатывается контролером прямого

5 доступа к памяти. Дополнительный вход 43 запроса переключения может быть подключен, например, к схеме обнаружения точек останова, которая вырабатывает импульс, инициирующий запрос на переключение. Этот же сигнал должен одновременно выраба0 тывать запрос прерывания, по которому осуществляется переход на уровень супервизора. Вывод 45 является добавлением к адресным выходам процессора, позволяя расширить адресное пространство. Вывод 35 определяет уровень памяти (уровень супер5 визора или уровень пользователя), к которому производится обращение, а также уровень устройств ввода-вывода. Сигнал с вывода 35 диспетчера должен подводиться ко всем дешифраторам выбора устройства вво,, да-вывода и ЗУ, обеспечивая в одном и том же адресном пространстве процессора наличие удвоенного количества портов ввода-вывода и удвоенного объема памяти на уровне супервизора и на уровне пользователя. «О на выходе 35 диспетчера опре5 деляет обращение к памяти или устройствам ввода-вывода супервизора, а «1 - к памяти или устройствам ввода-вывода пользователя.

Дешифратор 1 обеспечивает возможность записи в буферные регистры 40-42 адреса

0 сегмента памяти стека, данных и инструкции соответственно. Кроме того, дешифратор 1 формирует сигналы запроса на переключение на уровень пользователя (первый выход) и загрузки триггеров 22 и 23, определяющих принадлежность памяти дан5 ных и стека. Регистр 2 фиксирует состояние статуса, которое изменяется в каждом машинном цикле. Первый разряд регистра определяет цикл чтения первого байта команды, второй - цикл обращения к стеку, третий - обращение к портам ввода- вывода. На выходе элемента И 8 формируется сигнал, определяющий цикл обращения к данным. Вследствие отсутствия информации о циклах чтения инструкции (имеется только информация о цикле чтения первого байта команды, которая может быть двухбайтной и трехбайтной) комбинация блока 4, регистра 3 и триггера 24

ции (на выход передается состояние регистра 42), обращение к памяти данных (состояние регистра 41), обращение к памяти стека (состояние регистра 40). Если на входе 44 устройства присутствует нуле- вой потенциал, то регистры 40-42 находятся в состоянии запрета выхода.

Триггер 36 обеспечивает постоянный сброс регистра 2 перед началом каждой команды, т. е. выполняет функцию разграниопределяет циклы чтения второго или третье- 10 чения команд, которая необходима для обес15

печения возможности использования в качестве команд, инициирующих переход на уровень пользователя, команд, включающих только цикл чтения инструкции, например команд PCHL, IMP.

После сброса диспетчера определяется полная принадлежность уровню супервизора. Процесс переключения на уровень пользователя начинается посылкой команды вывода в порт, которую дещифрирует дешифратор 1

го байта команды. На выходе элемента ИЛИ 15 формируется сигнал, определяющий циклы чтения инструкции. Первые два разряда блока 4 определяют длину команды: «00 - однобайтная команда, «10 - двухбайтная команда, «11 - трехбайтная команда. Эта информация записывается в регистр 3 в цикле Ml, т. е. в цикле чтения первого байта команды. В этом цикле вход разрещения загрузки регистра 3 находится в состоянии, разрещающем загруз-20 и вырабатывает сигнал запроса переклюку в регистр информации с выхода бло-чения, поступающий на вход установки в «1 ка 4, который в цикле Ml также на-триггера 20 и через элемент 6 на вход ходится в выбранном состоянии. В последую-сброса триггера 19. Далее может следовать щие циклы осуществляется сдвиг информа-произвольное число команд на исключением ции в регистре. Выход 47 является выхо-команд из заданного множества, опреде- дом второго разряда регистра 3. Сигналом 33 ленного третьим разрядом блока 4. Коман- информация с выхода регистра 3 перепи-да из данного множества завершает процесс сывается в триггер 24 с выхода которогопереключения на уровень пользователя, снимается сигнал, определяющий чтение вто-Запрос на переключение с уровня рого и третьего байтов команды.пользователя на уровень супервизора ини- Триггер 20 осуществляет запрос на пе-,Q циирует либо команда вывода в порт с реключение: при запросе на переключениеуровня пользователя (по входу 27 уст- на уровень пользователя он переключаетсяройства), либо какой-либо аппаратный источ- в состояние «1, а при запросе на пе-ник переключения (по входу 43 устройства). реключение на уровень супервизора - в сое-Эти же сигналы должны инициировать тояние «О. Триггер 21 определяет принад-прерывание процессора. Переключение на лежность памяти инструкций и портов вво- с уровень супервизора происходит по появле- да-вывода. При переключении от принимаетнию сигнала подтверждения прерывания по

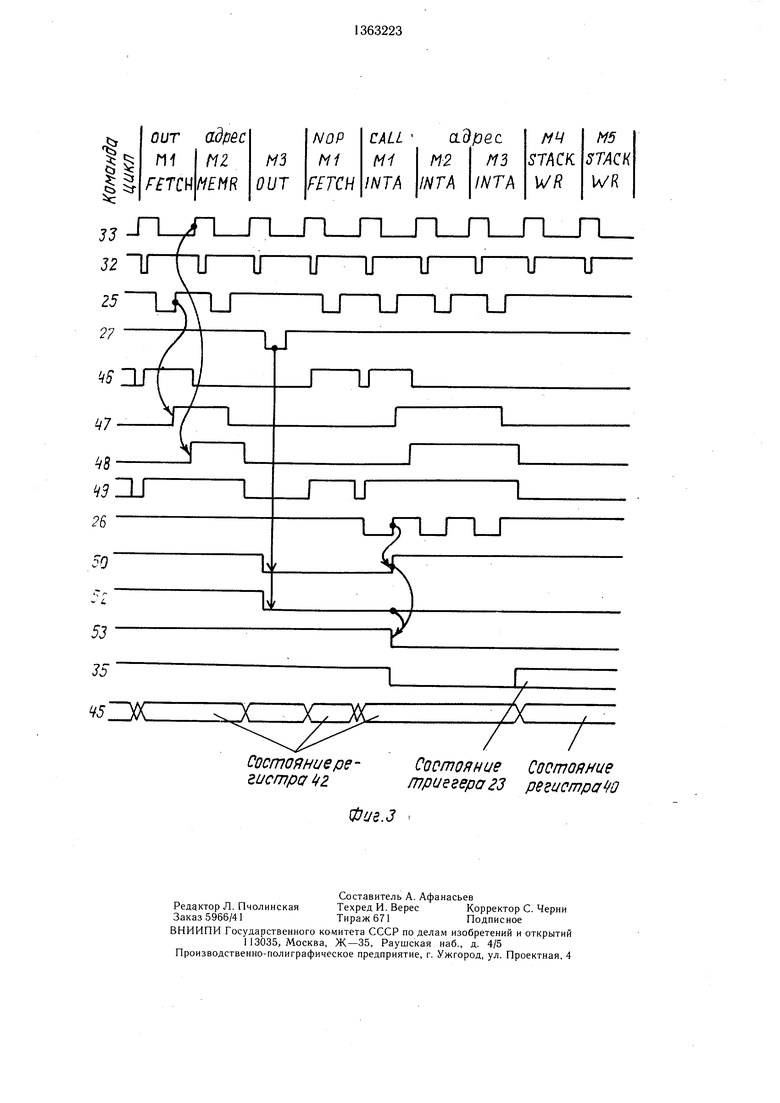

входу 26 диспетчера. Адрес перехода, т. е. точку входа на уровень супервизора, определяет контролер прерываний, который может быть запрограммирован с уровня супер- данного в третьем разряде блока 4 мно-40 визора. Диспетчер предоставляет возмож- жества (Команд, разрещенных для иниции-ность реализации защищенной системы с рас- рования переключения на уровень пользова-щиренной областью адресации, теля. Триггер 19 инициирует процесс пе-На фиг. 2 приведена временная диа- реключения, воздействуя на тактовый входграмма процесса перехода с уровня супертриггера 21. Любой запрос на переклю-визора на уровень пользователя. На этом чение переключает триггер в состояние «О, примере показаны действия блоков диспетзначение триггера 20. Триггер 22 - триггер принадлежности памяти данных, а триггер 23 - памяти стека. Триггер 18 фиксирует момент чтения команды из заперепад по входу 26 устройства и перепадО -«I,поступающий через

элементы 14 и 5 с выхода триггера 18, переключает его в «1.

Элементы И 9-12 и ИЛИ 16 обеспечивают мультиплексацию сигналов с триггеров 21-23, определяющих установленную принадлежность памяти инструкции, портов ввода-вывода, памяти данных и стека, на выход 35 устройства в зависимости от те50

чера от момента запроса на переключение до момента переключения на уровен пользователя. В верхней строке показаны команды микропроцессора КР580ИК80А. Команда вывода в порт является двухбайтной, поэтому из блока 4 в цикле М 1 счи - тывается код «110. Два .младщих разряда в этом цикле записываются в регистр 3. По сигналу 33 состояние второго разряда регистра записывается в триггер 24. В циккущего мащинного цикла. Элементы 55 ле М2 происходит сдвиг состояния регист- И 37-39 также обеспечивают мультиплек-ра 3 и следующим импульсом 33 в триггер 24

записывается «О. На выходе ИЛИ 15 (точка 49) получают состояние «1 в циклах Ml и М2. По импульсу на входе 29 на выхосацию состояния регистров 40-42 на выход 45 устройства в зависимости от текущего машинного цикла: чтение памяти инструкции (на выход передается состояние регистра 42), обращение к памяти данных (состояние регистра 41), обращение к памяти стека (состояние регистра 40). Если на входе 44 устройства присутствует нуле- вой потенциал, то регистры 40-42 находятся в состоянии запрета выхода.

Триггер 36 обеспечивает постоянный сброс регистра 2 перед началом каждой команды, т. е. выполняет функцию разграни5

печения возможности использования в качестве команд, инициирующих переход на уровень пользователя, команд, включающих только цикл чтения инструкции, например команд PCHL, IMP.

После сброса диспетчера определяется полная принадлежность уровню супервизора. Процесс переключения на уровень пользователя начинается посылкой команды вывода в порт, которую дещифрирует дешифратор 1

0 и вырабатывает сигнал запроса переключения, поступающий на вход установки в «1 триггера 20 и через элемент 6 на вход сброса триггера 19. Далее может следовать произвольное число команд на исключением команд из заданного множества, опреде- ленного третьим разрядом блока 4. Коман- да из данного множества завершает процесс переключения на уровень пользователя, Запрос на переключение с уровня пользователя на уровень супервизора ини- Q циирует либо команда вывода в порт с уровня пользователя (по входу 27 уст- ройства), либо какой-либо аппаратный источ- ник переключения (по входу 43 устройства). Эти же сигналы должны инициировать прерывание процессора. Переключение на с уровень супервизора происходит по появле- нию сигнала подтверждения прерывания по

чера от момента запроса на переключение до момента переключения на уровен пользователя. В верхней строке показаны команды микропроцессора КР580ИК80А. Команда вывода в порт является двухбайтной, поэтому из блока 4 в цикле М 1 счи - тывается код «110. Два .младщих разряда в этом цикле записываются в регистр 3. По сигналу 33 состояние второго разряда регистра записывается в триггер 24. В цикле М2 происходит сдвиг состояния регист- ра 3 и следующим импульсом 33 в триггер 24

де дешифратора формируется curnaj запроса на переключение, который перебрасывает триггер 19 в состояние «О (50), а триггер 20 - в состояние «1 (52). Появление команды перехода IMP, которая определяется как разрешенная для переключения на уровень пользователя, приводит к появлению «О на третьем выходе блока 4; это значение переписывается в триггер 18 (51). При появлении состояния «О на вывыход 35 - состояние триггера 22, а выход 45 - значение регистра 41, при обраш,ении к стеку выход 35 - состояние триггера 23, а выход 45 - значение регистра 40.

Формула изобретения Диспетчер памяти ЭВМ, содержащий дешифратор, первый и второй регистры, блок памяти признаков команд переключения, с первого по восьмой элементы И,

ходе элемента ИЛИ 15 (49) триггер 18 пере-Ю „ервого по четвертый элементы ИЛИ, элеходит в состояние «1. Перепад , , с первого по седьмой триггевыходе триггера 18 при «О на выходеpy „ричем информационный вход, первый

триггера 21 (53) проходит на вход С второй стробируюшие входы дешифратора

триггера 19, переключая его в состояниесоединены соответственно с первым инфор«1 (предполагается, что на информацион-мационным входом, входом признака ввода

lavrsno TniJT riiinQ 1 Q ылллотг а гтчг тпа-

25

диспетчера и выходом четвертого элемента ИЛИ соответственно, первый выход дешифратора соединен с первым входом второго элемента И и входом установки в «1 третьего триггера, второй выход дешифравания первого байта команды и признака обращения к стеку диспетчера соединены соответственно с первым и вторым ин- фОрмационнь1ми входами первого регистра, третий информационный вход которого соединен с выходом первого элемента ИЛИ, первый и второй входы которого соединены с входами признаков записи и чтения данных диспетчера, первый, второй и третий прямые

ном входе триггера 19 имеется состояние «1). Перепад на выходе триггера 19 воздействует на тактовый вход триггера 21, который принимает состояние триггера 20, т. е. «1. Тем самым при

чтении кодов команды («1 на выходе 20 тора соединен с синхровходами пятого и ИЛИ 15) на выход 35 диспетчера пере-шестого триггеров, входы признака считыдается состояние триггера 21. «1 на выходе 35 определяет принадлежность уровню пользователя. В циклах чтения данных или стека, а также в циклах записи данных или стека на выход 35 передается состояние триггера 22 или триггера 23, которые пер.еводятся в соответствующее состояние непосредственно по команде вывода в порт с уровня супервизора. На

выход 45 передается состояние регистра 41 выходы первого регистра соединены соот- 40.ветственно с первыми входами третьего

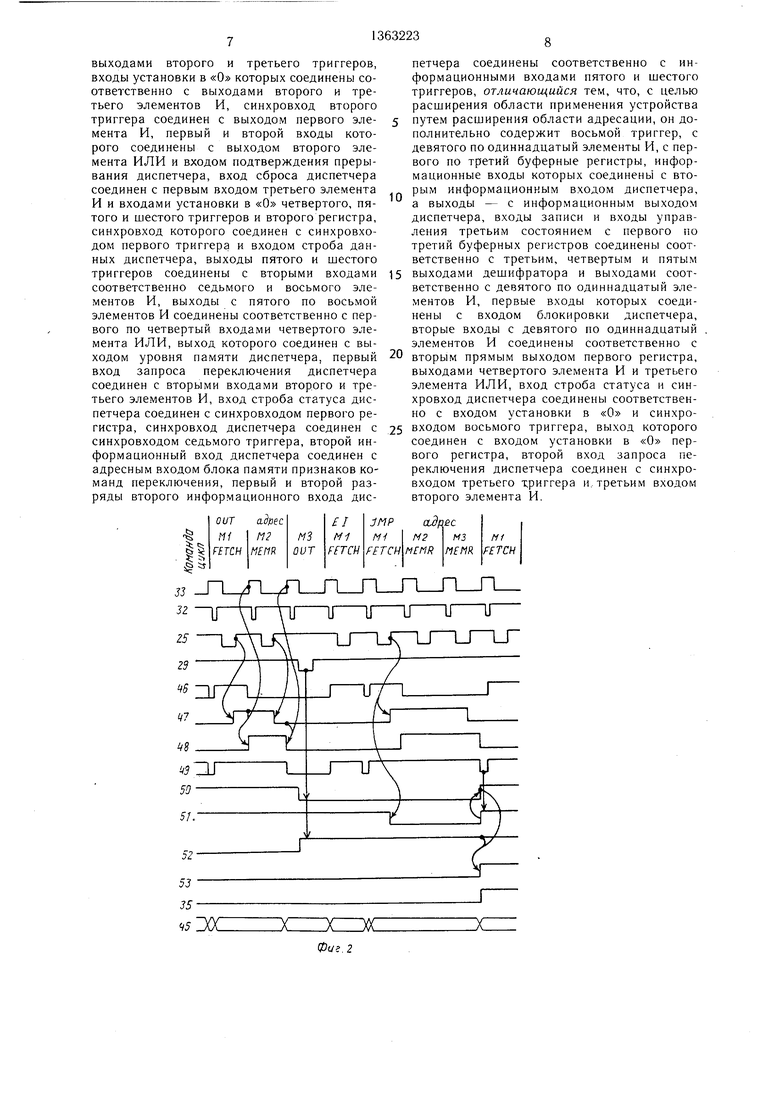

На фиг. 3 приведена временная диа- элемента ИЛИ, восьмого и шестого эле- грамма процесса перехода с уровня поль-ментов И, первый инверсный выход перзователя на уровень супервизора. Командавого регистра соединен с входом выборки

вывода в порт переключает триггеры 19 .блока памяти признаков команд переключе- и 20 в состояние «О. Эта же команда, 35 входом задания режима сдвига вто- которая поступает на вход 27 диспетчера, рого регистра, второй и третий инверсный должна поступить на вход запроса, преры-выходы первого регистра соединены с первания контролера прерывания КР580ВН59,вым и вторым входами четвертого элекоторый инициирует команду CALL помента И соответственно, выход и третий

заданному адресу (при его программирова-вход которого соединены соответственно с

НИИ) в зависимости от уровня прерывания. первым входом седьмого элемента И и вы- Сигнал подтверждения прерывания с выходаходом элемента НЕ, вход которого соедиконтролера КР550ВК38 поступает на вход 26иен с первым входом пятого элемента И,

устройства и осуществляет переключениевходом установки в «1 первого тригтриггера 19 в состояние «1. Перепад. гера и выходом третьего элемента ИЛИ, на выходе триггера 19 обеспечи- д второй вход которого соединен с выходом

вает переключение триггера 21 в состоя-

ние «О, что соответствует принадлежности уровню супервизора.

Диспетчер вырабатывает сигнал принадлежности текущего машинного цикла к уровню супервизора или к уровню пользова- 50 чения, выход признака команды безусловного теля и дополнительные адресные сигналыперехода которого соединен с информационным входом первого триггера, выход которого подключен к входу установки в «О первого триггера и первому входу второго элемента ИЛИ, второй вход которого соевыход 35 принимает состояние триггера 21, 55 динен с вторыми входами пятого и шес- при обращении к инструкции выход 35 -того элементов И и выходом четвертого

триггера, синхровход и информационный вход которого соединены соответственно с

седьмого триггера, информационный вход которого соединен с выходом второго регистра, информационный вход которого соединен с выходом поля длины команды блока памяти признаков команд переклю(45), причем все выходы устройства динамически меняют свое состояние в зависимости от действующего машинного цикла: при обращении к портам ввода-вывода

значение триггера 21, а выход 45 - значение регистра 42, при обращении к данным

выход 35 - состояние триггера 22, а выход 45 - значение регистра 41, при обраш,ении к стеку выход 35 - состояние триггера 23, а выход 45 - значение регистра 40.

Формула изобретения Диспетчер памяти ЭВМ, содержащий дешифратор, первый и второй регистры, блок памяти признаков команд переключения, с первого по восьмой элементы И,

диспетчера и выходом четвертого элемента ИЛИ соответственно, первый выход дешифратора соединен с первым входом второго элемента И и входом установки в «1 третьего триггера, второй выход дешифратора соединен с синхровходами пятого и шестого триггеров, входы признака считы

вания первого байта команды и признака обращения к стеку диспетчера соединены соответственно с первым и вторым ин- фОрмационнь1ми входами первого регистра, третий информационный вход которого соединен с выходом первого элемента ИЛИ, первый и второй входы которого соединены с входами признаков записи и чтения данных диспетчера, первый, второй и третий прямые

тора соединен с синхровходами пятого и шестого триггеров, входы признака считывыходы первого регистра соединены соот- ветственно с первыми входами третьего

гера и выходом третьего элемента ИЛИ, второй вход которого соединен с выходом

чения, выход признака команды безусловного перехода которого соединен с информационседьмого триггера, информационный вход которого соединен с выходом второго регистра, информационный вход которого соединен с выходом поля длины команды блока памяти признаков команд переклювыходами второго и третьего триггеров, входы установки в «О которых соединены соответственно с выходами второго и третьего элементов И, синхровход второго триггера соединен с выходом первого элемента И, первый и второй входы которого соединены с выходом второго элемента ИЛИ и входом подтверждения прерывания диспетчера, вход сброса диспетчера соединен с первым входом третьего элемента И и входами установки в «О четвертого, пятого и шестого триггеров и второго регистра, синхровход которого соединен с синхровхо- дом первого триггера и входом строба данных диспетчера, выходы пятого и шестого триггеров соединены с вторыми входами соответственно седьмого и восьмого элементов И, выходы с пятого по восьмой элементов И соединены соответственно с первого по четвертый входами четвертого элемента ИЛИ, выход которого соединен с выходом уровня памяти диспетчера, первый вход запроса переключения диспетчера соединен с вторыми входами второго и третьего элементов И, вход строба статуса диспетчера соединен с синхровходом первого регистра, синхровход диспетчера соединен с синхровходом седьмого триггера, второй информационный вход диспетчера соединен с адресным входом блока памяти признаков команд переключения, первый и второй разряды второго информационного входа диспетчера соединены соответственно с информационными входами пятого и шестого триггеров, отличающийся тем, что, с целью расширения области применения устройства путем расширения области адресации, он дополнительно содержит восьмой триггер, с девятого по одиннадцатый элементы И, с первого по третий буферные регистры, информационные входы которых соединены с вторым информационным входом диспетчера, а выходы - с информационным выходом диспетчера, входы записи и входы управления третьим состоянием с первого но третий буферных регистров соединены соответственно с третьим, четвертым и пятым

5 выходами дешифратора и выходами соответственно с девятого по одиннадцатый элементов И, первые входы которых соединены с входом блокировки диспетчера, вторые входы с девятого по одиннадцатый элементов И соединены соответственно с вторым прямым выходом первого регистра, выходами четвертого элемента И и третьего элемента ИЛИ, вход строба статуса и синхровход диспетчера соединены соответственно с входом установки в «О и синхро5 входом восьмого триггера, выход которого соединен с входом установки в «О первого регистра, второй вход запроса переключения диспетчера соединен с синхровходом третьего триггера и,третьим входом второго элемента И.

0

мз

/if FETCH

53 35 /5DOC

NOP

Н1

адрес

M2 IN Г A

/13 I NT A

fi4

SUCK WR

M5

STACK WR

53

35 V5ZX

z

zx

7 /

Состояние регистра 2

Состояние Состояние триегерагз ре и страхи

Фие.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Диспетчер памяти ЭВМ | 1990 |

|

SU1718225A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1817096A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для расширения адресного пространства. Цель изобретения - расширение области применения за счет расширения области адресации ЭВМ. Диспетчер памяти ЭВМ содержит дешифратор 1, первый 2 и второй 3 регистры, блок 4 памяти признаков команд переключения уровней памяти, первый 5, второй 6, третий 7, четвертый 8, пятый 9, шестой 10, седьмой 11 и восьмой 12 элементы И, первый 13, второй 14, третий 15 и четвертый 16 элементы ИЛИ, элемент 17 НЕ, первый 18, второй 19, третий 20, четвертый 21, пятый 22, шестой 23 и седьмой 24 триггеры, вход 25 строба данных, вход 26 подтверждения прерываний, первый вход 27 запроса переключений, вход 28 сброса, вход 29 признака ввода, первый информационный вход 30, входы 31 статуса, вход 32 строба статуса, синхровход 33, второй информационный вход 34, выход 35 уровня памяти, восьмой триггер 36, девятый 37, десятый 38 и одиннадцатый 39 элементы И, первый 40, второй 41 и третий 42 буферные регистры, второй вход 43 запроса переключения, вход 44 блокировки и информационный выход 45. 3 ил. с сл 25 00 Oi со 1чЭ to СО

| Electronic, 1982, № 6, с | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Авторское свидетельство СССР № 1246772, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-01-20—Подача