Ийобретение относится к автоматике и вычислительной технике и предназначено для использования в системах экспресс-обработки измерительной информации.

Целью изобретения является ,расширение функциональных возможностей путем обработки порядковы5 статистик.

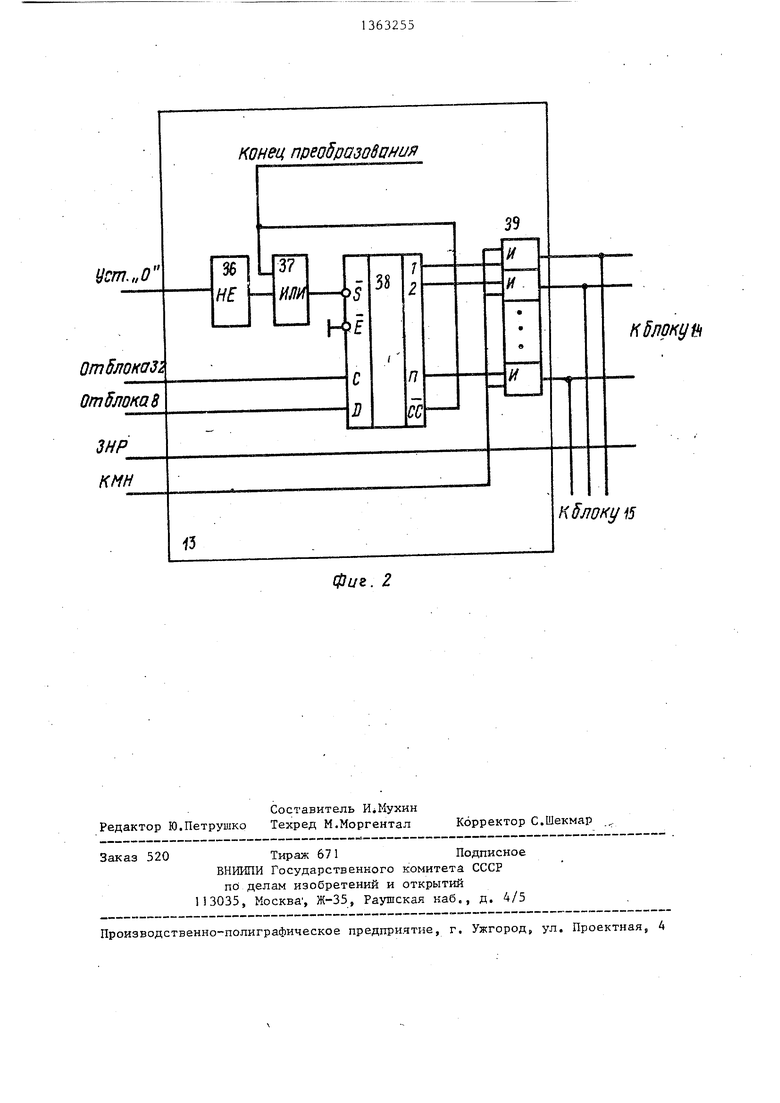

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - блок-схема блока управления.

Устройство содержит группу цифро- аналоговых преобразователей 1, группу сумматоров 2, группу цифроаналого- 5 порядковой статистики.

вых преобразователей 3, группу компараторов 4, группу элементов И-НЕ 5,группу триггеров 6, группу элемента ИЛИ 7, блок 8 сравнения, содержащий делитель 9 напряжения, цифроана- логовый преобразователь 10 и компаратор 11; блок 2 уравновещивания, содержащий блок 13 управления и циф- роаналоговый преобразователь 14. Кроме того, устройство содержит сумматор 15, цифроаналоговьй преобразовав тель 16, регистры 17-19, триггер 20, . мультиплексор 2, распределитель 22 - импульсов 5 счетчики 23 и 24j элементы И 25-27, блоки 28 и 29 памяти, регистр 30, мультиплексор 31, делитель 32 частоты, генератор 33 им пульсов у выходы 34 и 35 устройства. Блок J 3 содар-яит элемент НЕ 36,, элемент ИЛИ 37, регистр 38 и группу элементов И 39;

Устройство работает следующим образом.

Перед началом работы блоки устройства находятся в следующем состоянии :

распределитель 22 импульсов содержит программу своей работы в течение одного ци7ша5

ка Q-выходе триггера 20 - потен- ци.ал логической единицы;

ячейки блока 29 памяти обнулены; блоки 28 и 29 находятся в режиме считывания информации;

на выходе блока 28 - код, соот- ветств ующий единичному коэффициенту передачи умножающих цифроаналоговых преобразователей 1;

выходной код регистра 17, определяющий единичный коэффициент переда-, чи умножак щих цифроаналоговых преобразователей 3, установлен на выходе мультиплексора 21 ;

выходные коды счетчика 23 импуль сов и регистра 17 одинаковы;

30

Устройство начинает с запуска генератора 33 I период. В первом ц периода измеряется теку

2Q г-й порядковой статисти В конце первого цикл Конец преобразования ет на Q-выходе триггера логической единицы. При

25 Де мультиплексора 21 ус выходной код счетчика 2 соответствующий единичн енту передачи цифроанал образователей 3 блок 2 реводится в режим запис с выхода сумматора 13 п ределяемому потенциалом триггера 20.

По заднему фронту им преобразования изменяе

35 цу содержимое счетчика го изменяется потенциал гического элемента И 27 прохождение импульсов с гического элемента 25 н

40 новки режима блока 28 п рый устанавливается в р . вания информации. На ци цифроаналоговых преобра установлен код значения

45 вой статистики Zf,(t). фронту импульса Конец ния с некоторой зад,ерж ствляется запись данных блока 29 в регистр 18.

50 на выходе цифроаналогов зователя б равно нулю.

На Q-выходе триггера ал логической единицы с в течение k циклов перв

55 Блок 28 находится в теч

циклов в режиме считыва После прекращения де са Конец преобразовани второй цикл.

счетчик 24 импульсов обнулен;

на выходе логического элемента И 27 установлен уровень логического нуля;

на цифровом выходе 35 устройства и выходе регистра 18 установлен код, соответствующий нулевому напряжению на аналоговом выходе 34 устройства;

на выходе мультиплексора 31 установлен код, соответствующий выходному коду регистра 30, определяющему номер г-й порядковой статистики. В регистр 19 занесен номер ранга 1-й

порядковой статистики.

Устройство начинает свою работу с запуска генератора 33 импульсов. I период. В первом цикле этого периода измеряется текущее значение

г-й порядковой статистики 7,(. В конце первого цикла импульс Конец преобразования устанавливает на Q-выходе триггера 20 потенциал логической единицы. При этом на выхоДе мультиплексора 21 устанавливается выходной код счетчика 23 импульсов, соответствующий единичному коэффициенту передачи цифроаналоговых преобразователей 3 блок 28 памяти переводится в режим записи информации с выхода сумматора 13 по адресу, определяемому потенциалом Q-выхода триггера 20.

По заднему фронту импульса Конец преобразования изменяется ка единицу содержимое счетчика 24. После этого изменяется потенциал на выходе логического элемента И 27, запрещающий прохождение импульсов с выхода.логического элемента 25 на вход установки режима блока 28 памяти, который устанавливается в режим считы- вания информации. На цифровых входах цифроаналоговых преобразователей 1 установлен код значения г-й порядковой статистики Zf,(t). По заднему фронту импульса Конец преобразования с некоторой зад,ержкой осуществляется запись данных (У,0) из блока 29 в регистр 18. Напряжение

на выходе цифроаналогового преобразователя б равно нулю.

На Q-выходе триггера 20 потенци ал логической единицы сохраняется в течение k циклов первого периода.

Блок 28 находится в течение этих

циклов в режиме считывания информации. После прекращения действия импульса Конец преобразования начинается второй цикл.

В пюбом последующем цикле к цифровому входу блока 8 сравнения подключается код номера 1-й порядковой статистики.

II период. Так как на цифровых входах цифроаналоговых преобразователей 3 и 1 установлены коды, соответствующие единичному коэффициенту передачи, то в первом цикле второго периода измеряется значение г-й порядковой статистики (в остальных циклах 1-й) L(t. При появлении импульса Конец преобразования на Q-выходе триггера 20 устанавливает- ся потенциал единицы. Блок 28 памяти переводится в режим записи информации с выхода сумматора 15 в ячейки с адресом 2. На выходе мулвтиплексо- ра 21 устанавливается код,соответст- вующий состоянию счетчика 23, соот- ветствухяций коэффициенту передачи преобразователей 3 (). Это значение поддерживается неизменным в течение периода. По заднему фронту импульса Конец преобразования изменяется на единицу содержимое счетчика 24 импульсов. После этого на выходе элемента И 27 появляется потенциал, запрещающий прохождение импульсов с выхода элемента И 25 на вход установки режима блока 28. Блок 28 -устанавливается в режим считывания информации из ячеек с адресом 2. По заднему фронту импульса Конец преобразования с задержкой осущест- вляется запись данных (1,) из. ячеек блока 29 с номером адреса i в регист 18. На выходе преобразователя 16уст- танавливается выходное напряжение., значение которого соответствует Y ,

В конце k+1-го цикла L-ro периода в ячейках ОЗУ 29 содержатся коды оценок k значений корреляционной функци между г-й и 1-й порядковыми статистиками - в ячейках с номером 1;

Y4Y J- l+(2(tJz(tp+€) ) k2 в ячейках с номером kt , - -b(Z,(taZe(t,+kT)-Y; -Vk,,

где Zp(tL),ZE(ti,+kr) - значения г-й

и 1-й порядковых статисти соответственно в L-M периоде в первом и k+1-м циклах (k,-l/L).

Формула изобретения

Устройство для определения корреляционной функции, содержащее распре

j Q 5 5

5

50

55

0

делитель кмпудьсов, триггер, регистры, о т л и ч а ю Di е е с я тем, что, с целью расширения функциональных возможностей путем обработки порядковых статистик, в него введены генератор импульсов группы из N сумматоров, две группы из N цифроанало- говых преобразователей, группа из N компараторов, группа из ; -риггеров, группы из N элементов И-НЕ и ИЛИ, блоки памяти, делитель частоты, делитель напряжения, сумматор, мультиплексоры, счетчики,цифроаналоговые преобразователи, блок управления, содержащий регистр, группу элементов И, элемент ИЛИ, элемент НЕ, вход которого подключен к первому выходу распределителя импульсов, выход элемента НЕ соединен с первым входом элемента ИЛИ блока управления, выход которого подключен к входу установки в О регистра блока управления, выход i-ro разряда которого () соединен с первым входом i-ro элемента И группы, вторые входы элементов И группы объединены и подключены к второму выходу распределителя импульсов, (N+l)-l выход регистра блока управления соединен с вторым входом элементов ИЛИ блока управления и входом Пуск .распределителя импульсов, D-вход и вход синхронизации регистра блока управления подключены соответственно к выходу компаратора и к выходу делителя частоты, выход i-ro элемента И группы соединен с входом i-ro разряда первого цифроаналогово- го преобразователя, знаковый вход которого подключен к третьему выходу распределителя импульсов, вход синхронизации которого объединен с входом делителя частоты и соединен с выходом генератора импульсов, вход Стоп которого подключен к выходу переполнения первого счетчика, ин- формационный выход которого соединен с первым входом мультиплексора, второй вход которого подключен к выходу I

первого регистра, информационные входы устройства подключены к соответствующим цифровым входам цифроанало- говых преобразователей первой группы, аналоговые входы которых объединены

и соединены с выходом первого блока памяти, информационный вход которого объединен с информационным входом второго блока памяти и подключен к выходу сумматора, первый вход которого

объединен с входом второго цифроана- логового преобразователя и соединен с выходом второго регистра, информационный вход которого подключен,к выходу второго блока памяти, адресный вход которого соединен с выходом второго счетчика, подключенным к первому входу первого элемента, второй вход которого подключен к инверсному входу второго элемента И и к первому входу третьего элемента И, выход которого подключен к входу считывания первого блока памяти, вход записи которого объединен с управляющими ; входами первого и второго мультиплексоров и с D-входом триггера и подключен к инверсному выходу триггера, прямой выход которого соединен с BTqpHM входом третьего элемента И, третий вход которого объединен с входом установки в О триггера, счетным входом второго счетчика, вторым входом второго элемента И, входом записи второго регистра и под- ключей к выходу {N+1)-го разряда регистра блока управления, счетный вход первого счетчика соединен с выходом второго счетчика, выход i-ro .цифроаналогового преобразователя первой группы подключен к первому входу i-ro сумматора группы, вторые входы с- /мматоров объединены и соединены с выходом второго цифроанало- гового нреобрэзователя, выход i-ro сумматора группы подключен к информационному -входу цифроаналогово го преобразозателя второй группы, входы за,цания коэф(3.шциента переда-т чи цифроаналоговых преобразователей

5

0

5

0

5

второй группы объединены и соединены с выходом первого мультиплексора, выход i-ro цифроаналогового преобразователя второй группы подключен к информационному входу i-ro компаратора группы, входы задания порогов компараторов группы объединены и соединены с выходом первого цифроаналогового преобразователя, выход i-ro компаратора подключен к первым входам i-ro элемента ИЛИ группы и i-ro элемента И-НЕ,группы, вторые входы элементов И-НЕ группы объединены и соединены с четвертым выходом распределителя импульсов, пятый выход которого подключен к входам установки в О триггеров группы, выход i-ro элемента И-НЕ группы соединен с входом установки в О i-ro триггера группы, прямой выход которого подключен к второму входу i-ro элемента ИЛИ группы, выход которого соединен с i-м входом делителя напряжения, выход которого подключен к информационному входу компаратора, вход задания которого соединен с выходом третьего цифроаналогового преобразователя, вход которого подключен к выходу второго мультиплексора, информационные входы которого соединены с выходами третьего и четвертого регистров соответственно, выход компаратора соединен с входом начальной установки распределителя импульса, выход элементов И группы подключен к первому входу сумматора, выход второго элемента И соединен с входом записи второго блока памяти.

конец прео5разо8пния

36 Я5

37

Ш

- 5

i4f

От5локаз /.

От5лока8

13

7г/г. г

Составитель И Мухин Редактор Ю.Петрушке Техред М.Моргентал

Заказ 520Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва , Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

;/

38

и

5лрну1

п со

и

} 5лок1/ 5

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения автокорреляционной функции | 1984 |

|

SU1363254A1 |

| Устройство для определения среднего значения выборочного размаха | 1984 |

|

SU1363252A1 |

| Устройство для определения функций плотности вероятностей | 1984 |

|

SU1363253A1 |

| Устройство для определения текущей оценки среднего значения | 1984 |

|

SU1363251A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Цифровой фильтр | 1990 |

|

SU1780089A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

Изобретение относится ксистемам экспресс-обработки измерительной информации. Целью изо ретения является расширение функциональных возможностей путем обработки порядковых статистик. Цель достигается за счет упорядочивания ансамбля входных величин и реализации рекурсивных алгоритмов и за счет того, что в устройство введены цифроаналоговые преобразователи 1, 3, компараторы 2, 4, элементы И-НЕ 5, триггеры 6, блок сравнения 8, элементы ИЛИ 7, блок уравновешивания 12, сумматор 15, регистры 17-19, триггер 20, мультиплексор 21, распределитель импульсов 22, счетчики 23, 24, элементы И 25- 27, блоки памяти 28-29, регистр 30, мультиплексор 31, делитель частоты 32, генератор импульсов 33. 2 ил. с (Л со оэ со ГС ел СП

| 0 |

|

SU326557A1 | |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР | 0 |

|

SU337784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1984-10-29—Подача