113635

Изобретение относится к радиосвязи и может использоваться в станциях цифровой радиорелейной связи с частотной манипуляцией.

Цель изобретения - обеспечение приема многоуровневых сигналов.

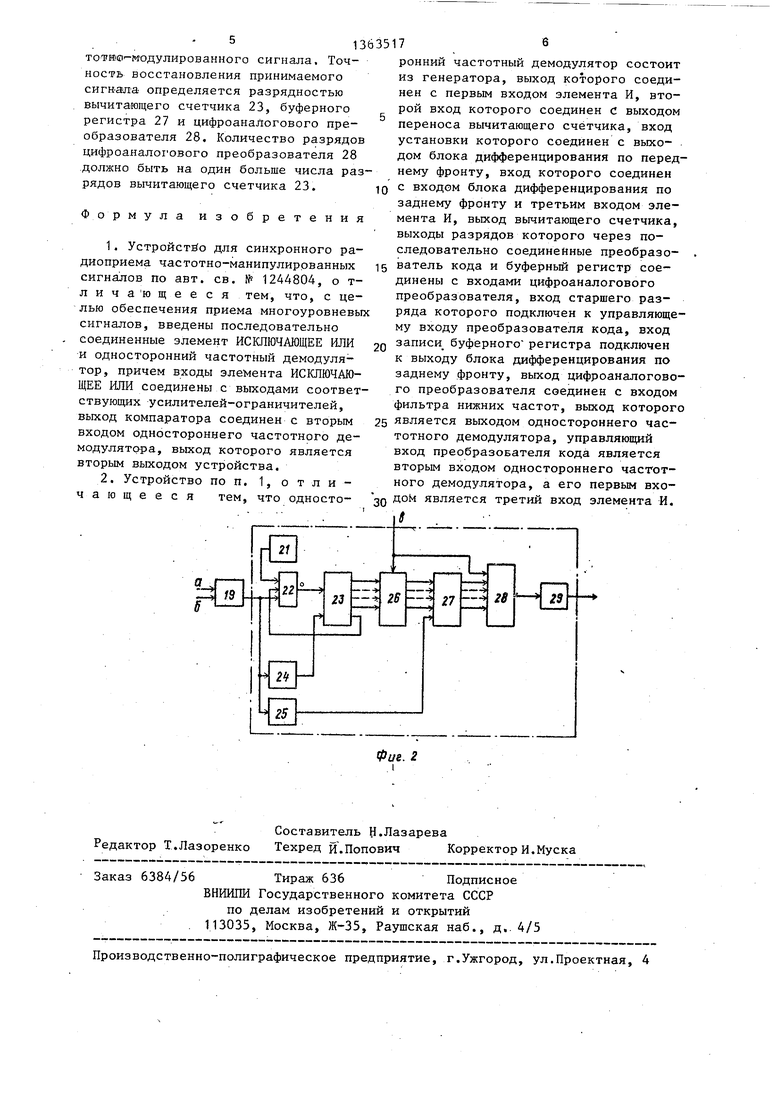

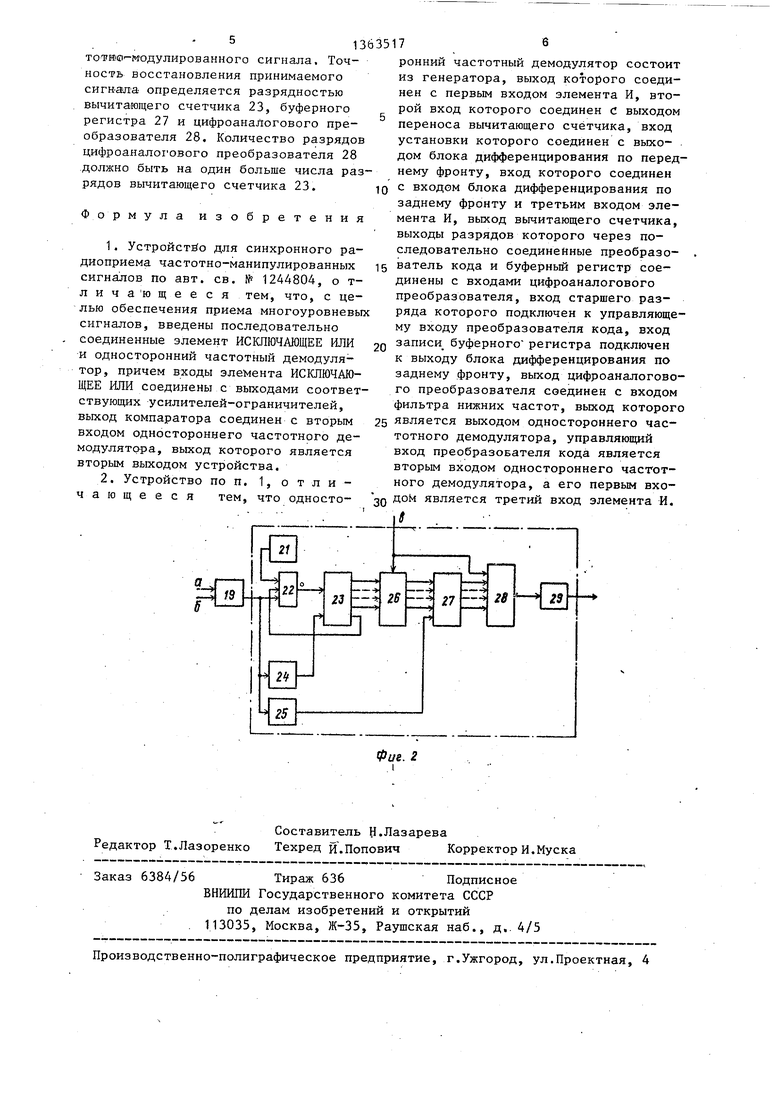

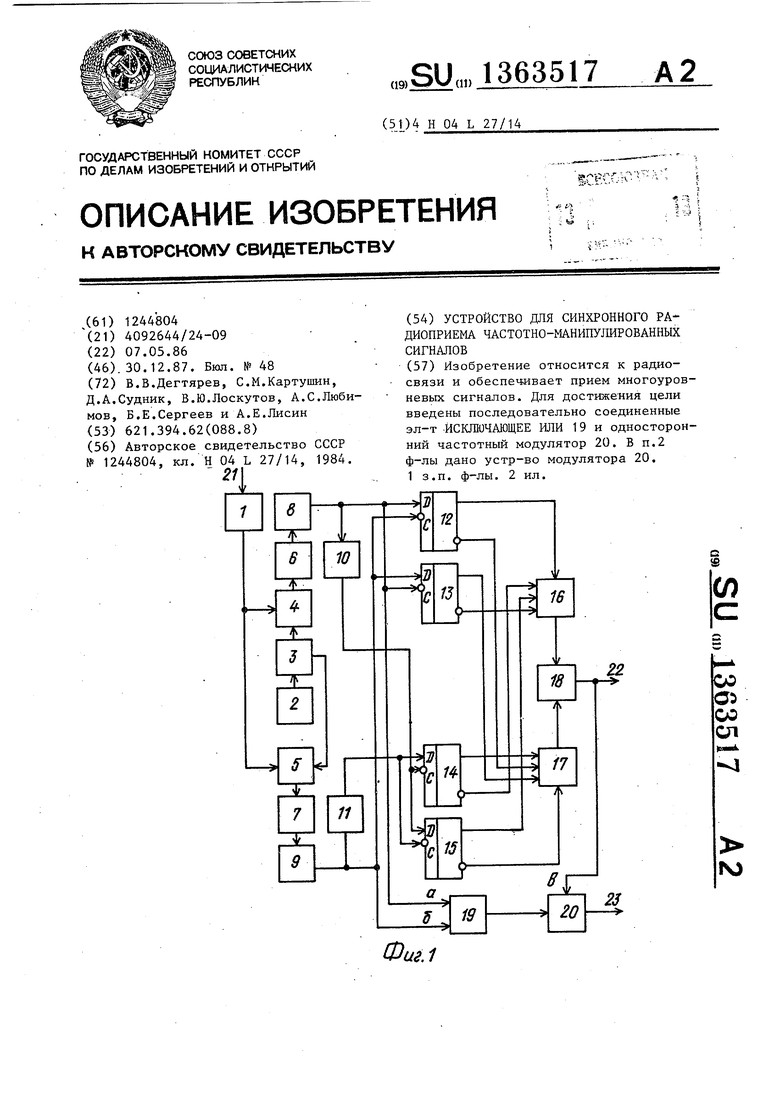

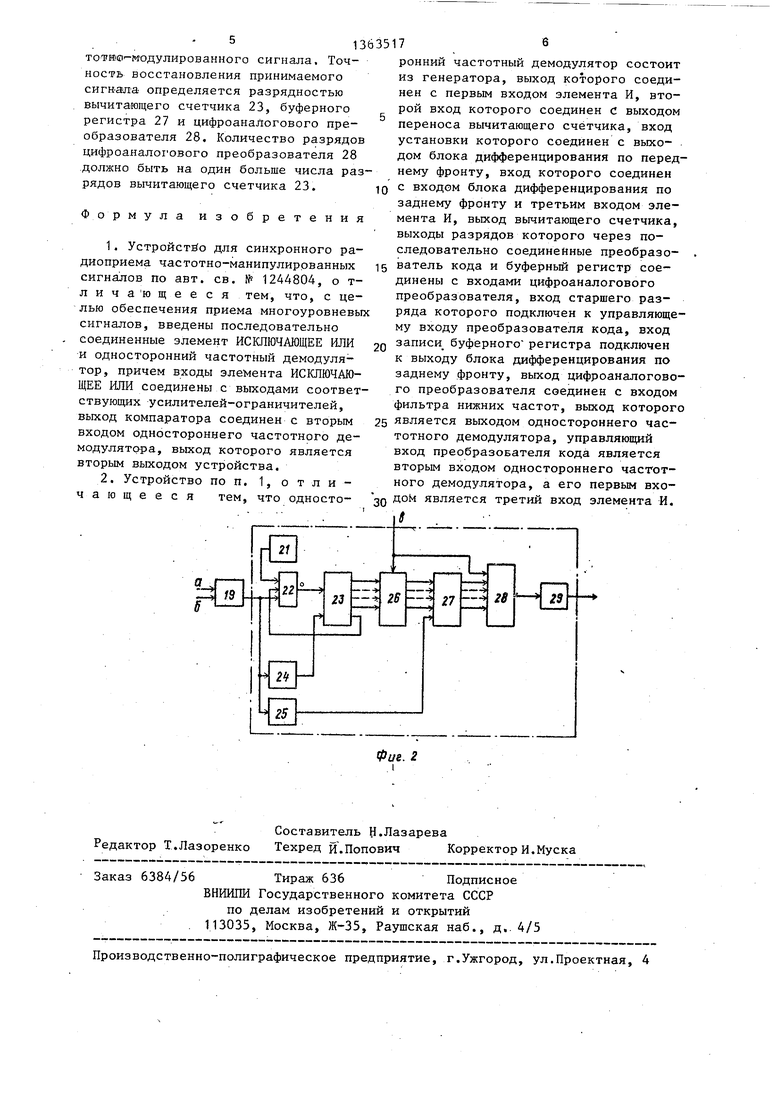

На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная .., схема одностороннего частотного демодулятора.

Устройство содержит входной усилитель 1, синхронный гетеродин 2, квад- ратурньй направленный ответвитель 3, ,с первый 4 и второй 5 смесители, первый 6 и второй 7 фильтры нижних частот, первый 8 и второй 9 усилители- ограничители, первый 10, второй 11 элементы НЕ, первый 12, второй 13, „ третий 14 и четвертый 15 триггеры, первый 16 и второй 17 сумматоры, компаратор 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, односторонний частотный демодулятор 20, состоящий из генератора 21, 25 элемента И 22, вычитающего счетчика 23, блока 24 дифференцирования по переднему фронту, блока 25 дифференцирования по заднему фронту, преобразователя 26 кода, буферного регист- pa 27, цифроаналогового преобразователя 28 и фильтра 29 нижних частот.

Устройство работает следующим образом. .

Частотно-манипулированный сигнал поступает через входной усилитель 1 одновременно на входы смесителей 4 и 5, на вторые входы которых через квадратурный направленный ответвитель 3 сигналы в квадратуре (со сдвигом п на 90 ) подаются от синхронного гетеродина 2. Частота синхронного гетеродина 2 устанавливается равной средней частоте спектра принимаемого сигнала (сигнала на входе устройства). В результате преобразования на выхо- ах-смесителей 4 и 5 образуются сигналы, поднесущие которых равны текуему значению частотного сдвига раиочастотной несущей от своего среднего значения, а взаимный сдвиг фаз авен 90 . При изменении знака модуирующего сигнала происходит взаимное инвертирование сигналов в квадратурных каналах при сохранении их вадратуры, т.е. взаимный фазовый сдвиг становится равным 270°. При изенении уровня сигнала на передаче зменяются значения частотного сдви45

50

55

.,

с 5 Q

п

5

0

5

172

га поднесущих. Фильтры 6 и 7 нижних частот обеспечивают частотную избирательность и формирование огибающих по квадратурным каналам. Ана/юговые сигналы с фильтров 6 и 7 нижних частот усилителями-ограничителями 8 и 9 усиливаются и ограничиваются и таким образом преобразуются в цифровую (импульсную форму). Сигнал с выхода усилителя-ограничителя 8 поступает на информационный D-вход триггера 12, синхронизации триггера 13, на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и на вход элемента НЕ 10, который инвертирует сигнал по полярности Сигнал с выхода элемента НЕ 10 подается на информационный D-вход триггера 15 и С-вход синхронизации триггера 14. Сигнал с выхода усилителя-ограничителя 9 поступает на информационный D-вход триггера 13, С-вход синхронизации триггера 12, вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и на элемент НЕ 11, который инвертирует сигнал по полярности. Сигнал с выхода элемента НЕ 11 подается на информационный D-вход триггера 14 и С-вход синхронизации триггера 15. На прямых выходах триггеров устанавливается сигнал, соответствующий по полярности сигналу на информационном D-входе в момент появления переднего фронта (или заднего в зависимости от типа микросхем) на его С-входе синхронизации. Сигналы с прямых выходов триггеров 12, 15 и с инверсных выходов триггеров 13, 14 подаются на входы сумматора 16, кото- рьй суммирует эти сигналы по напряжению. Сигналы с инверсных выходов триггеров 12, 15 и с прямых выходов триггеров 13, 14 подаются на входы сумматора 17. Сигналы с выходов сумматоров 16, 17 в противофазе подаются на входы компаратора 18, который преобразует ступенчатый сигнал с сумматоров в двоичньш сигнал 41. При поступлении на входы элемента ИСКПЮЧАЮЩЕЕ ИЛИ 19 сигналов одинаковой полярности на выходе появляется сигнал О, а при поступлении сигна- hoB разной полярности - сигнал 1. Длительность импульсов сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 обратно пропорциональна частотному сдвигу принимаемого радиосигнала, а частота их следования в два раза выше частоты следования сигналов с усилителей-ограничителей 8 и 9. Сигнал

313

с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 подается на информационный вход одностороннего частотного демодулятора 20, на управляющий вход которого подается сигнал с компаратора 18. Так как синхронный гетеродин 2 настраивается на среднюю частоту принимаемого сигнала, поло.жительному и отрицательному значениям частотных сдвигов радиочастот- ной несущей соответствует одно значение частоты поднесущих в квадратурных каналах (этим объясняется смысл термина односторонний, введенного в название частотного демодулятора). Односторонний частотный демодулятор 20,- используя удвоенное значение частотного сдвига по информационному входу и информацию о знаке, поступающую с выхода компаратора 18 на управ- ляющий вход, формирует сигнал, который идентичен информационному сигналу.

Односторонний частотный демодулятор работает следующим образом. Сиг- нал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 подается параллельно на третий вход элемента И 22 и входы блоков 24 и 25 дифференцирования. На второй вход элемента И 22 с выхода переноса вычитающего счетчика 23 подается сигнал 1 (О подается только в случаях переполнения счетчика для блокировки) . На первый вход элемента И 22 подается сигнал с генератора 21. Частота следования импульсов сигнала должна быть не менее удвоенного значения максимального частотного сдвига. В результате взаимодействия этих сигналов на выходе элемента И 22 по

является сигнал, в котором число импульсов в каждой пачке прямо пропорционально длительности импульсов сигнала с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и обратно пропорционально частотному сдвигу радиочастотной несущей. Блок 2А дифференцирования по переднему фронту вьщеляет передние фронты сигнала и образует на своем

выходе сигнал, который подается на вход установки вычитающего счетчика 23 и устанавливает его в состояние, соответствующее 1 во всех разрядах, в начале каждой пачки импульсов сигнала с выхода элемента И 22. Сигнал (каждая пачка) с выхода элемента И 22 подается на вьиитающий вход вычитающего счетчика 23 и производит вычитание. Двоичное число, ко

5 о

0

5

0

5

174

торое устанавливается в вычитающем счетчике 23 по окончании вычитания, обратно пропорционально количеству импульсов, поступивших на вычитающий вход вычитающего счетчика 23, т.е. прямо пропорционально частотному сдвигу. В случае достижения вычитающим счетчиком 23 состояния О по всем разрядам (переполнения) происходит блокировка его в этом состоянии до начала следующего информационного импульса. Блокировка осуществляется за счет поступления уровня О с выхода переноса вычитающего счетчика 23 на второй вход элемента И 22. Двоичное число с вычитающего счетчика 23 поразрядно через преобразователь 26 кода подается на информационные входы буферного регистра 27. При наличии 1 на управляющем входе преобразователя 26 кода- сигналы каждого разряда передаются без изменений, а при наличии О сигналы каждого разряда передаются с инверсией по символам, т.е. вместо 1 передается О и наоборот. Эти сигналы поразрядно записываются в буферный регистр 27 каждым импульсом сигнала, который поступает с блока 25 дифференцирования по заднему фронту на вход записи буферного регистра- 27. Эта информация хранится в памяти буферного регистра 27 в период времени между импульсами сигнала с блока 25 дифференцирования и одновременно поразрядно подаются на входы цифроаналого- вого преобразователя 28. При этом на вход ста;ршего разряда цифроаналогово- го преобразователя 28 подается сигнал, который совместно с преобразователем кода 26 обеспечивает на своем выходе формирование двухполярного сигнала, т.е. формирование двухполярного сигнала обеспечивается за счет кодирования в преобразователе 26 кода и в цифроаналоговом преобразователе 28 и смещения подаваемого на опорный вход операционного усилителя циф- роаналогового преобразователя 28. Абсолютное значение сигнала на выходе ци роаналогового преобразователя 28 соответствует сигналам двоичного числа, которые поразрядно подаются на его входы, а полярность его определяется сигналом с преобразователя 26 кода. Фильтр 29 нижних частот уменьшает уровень щумов квантования на выходе устройства при приеме частотмо модулированного сигнала. Точность восстановления принимаемого спгнгта определяется разрядностью вычитающего счетчика 23, буферного регистра 27 и цифроанаЛогового преобразователя 28, Количество разрядов цифроаналогового преобразователя 28 должно быть на один больше числа разрядов вычитающего счетчика 23.

Формула изобретения

1.Устройство для синхронного радиоприема частотно-манипулированных сигналов по авт. ев, № 1244804, о т- лича ющееся тем, что, с целью обеспечения приема многоуровневы сигналов, введены последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и односторонний частотный демодулятор, причем входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами соответствующих усилителей-ограничителей, выход компаратора соединен с вторым входом одностороннего частотного демодулятора, выход которого является вторым выходом устройства,

2,Устройство по п, 1, отличающееся тем, что односто

Составитель Н.Лазарева Редактор Т.Лазоренко Техред й.Попович Корректор И,Муска

Заказ 6384/56 Тираж 636Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий . 113035, Москва, Ж-35, Раушская наб., д.. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

ронний частотный демодулятор состоит из генератора, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом переноса вычитающего счётчика, вход установки которого соединен с выходом блока дифференцирования по переднему фронту, вход которого соединен с входом блока дифференцирования по заднему фронту и третьим входом элемента И, выход вычитающего счетчика, выходы разрядов которого через последовательно соединенные преобразователь кода и буферный регистр соединены с входами цифроаналогового преобразователя, вход старшего разряда которого подключен к управляющему входу преобразователя кода, вход записи буферного регистра подключен к выходу блока дифференцирования по заднему фронту, выход цифроаналогового преобразователя соединен с входом фильтра нижних частот, выход которого

является выходом одностороннего частотного демодулятора, управляющий вход преобразователя кода является вторым входом одностороннего частотного демодулятора, а его первым вхоДОМ является третий вход элемента И,

Фие. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| Устройство для измерения флуктуационной составляющей частоты сигналов с линейно-частотной модуляцией | 1988 |

|

SU1631456A1 |

| Манипулятор частоты без разрыва фазы | 1987 |

|

SU1515384A1 |

Изобретение относится к радиосвязи и обеспе1«1вает прием многоуровневых сигналов. Для достижения цели введены последовательно соединенные эл-т .ИСКЛЮЧАЮЩЕЕ или 19 и односторонний частотный модулятор 20. В п.2 ф-лы дано устр-во модулятора 20. 1 3.п. ф-лы. 2 ил. 22. ро С5 СдЭ СП ГО Фиг,1

| Устройство для синхронного радиоприема частотно-манипулированных сигналов | 1984 |

|

SU1244804A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-07—Подача