Изобретение относится к вычислительной технике и может быть исполь зовано в устройствах, требуюпщх решения большого числа сложных логических функций от многих переменнь1х, в частности в устройствах технической диагностики отказов функциональных систем, а также для решения задач в системах управления.

Целью изобретения/является сокращение оборудования при увеличении входных переменных вычисляемой логической функции.

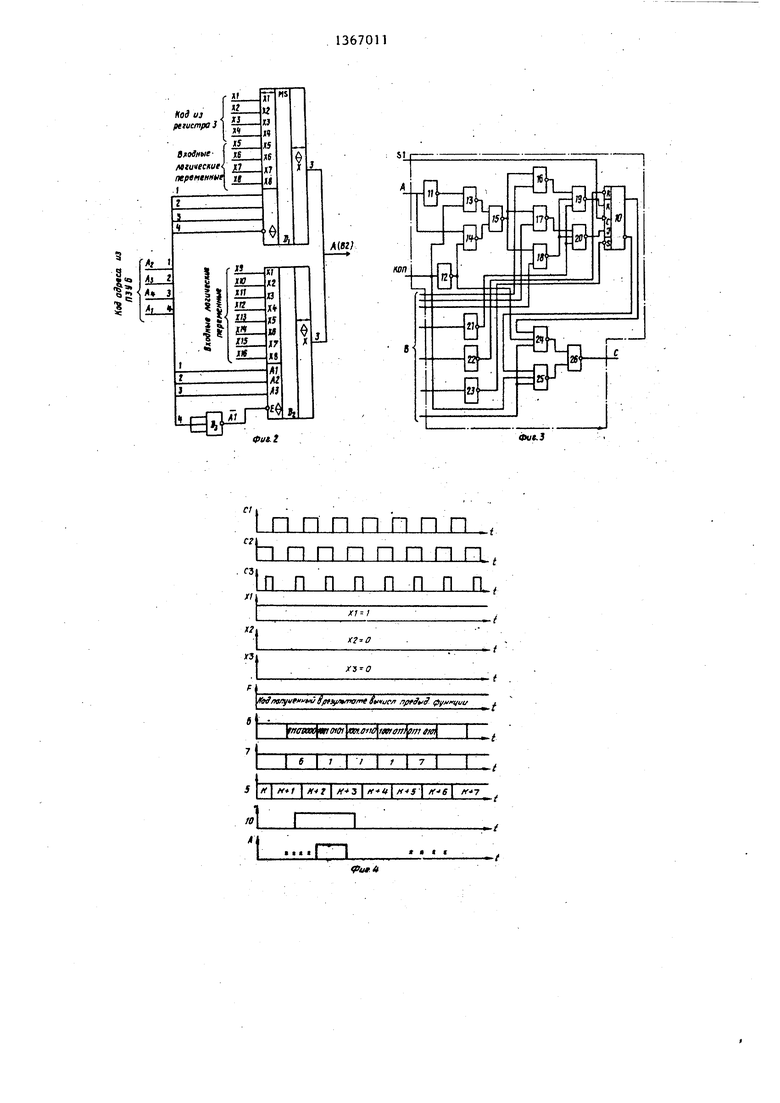

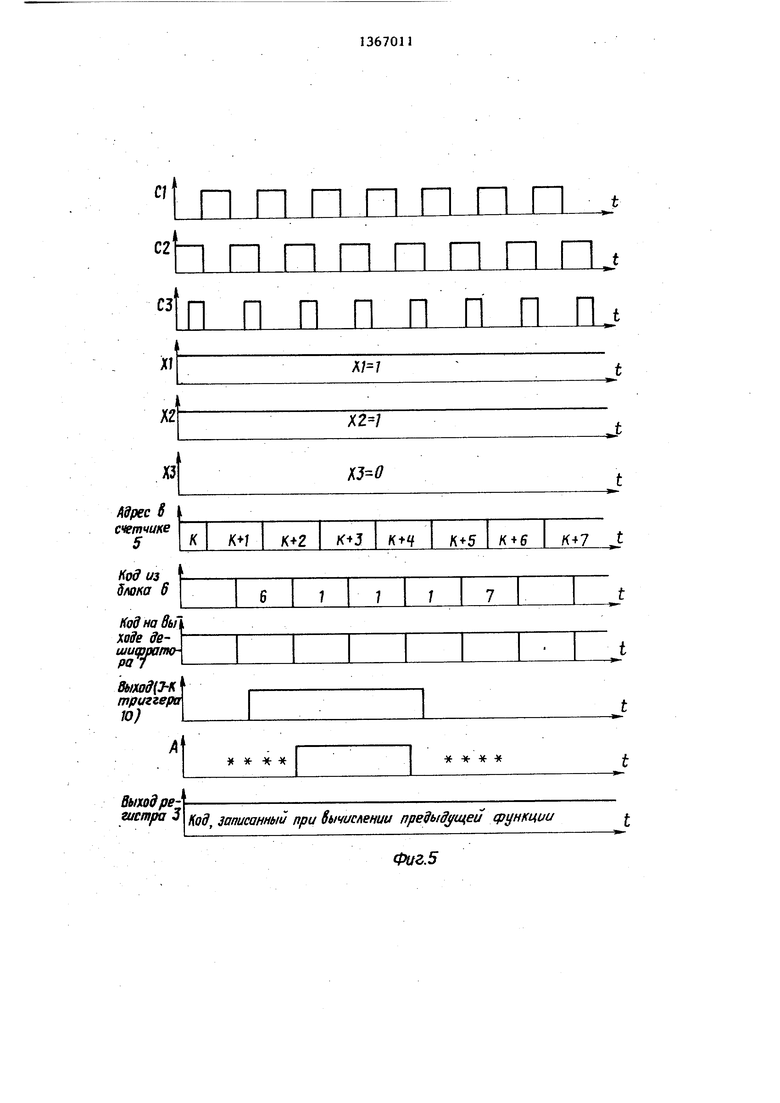

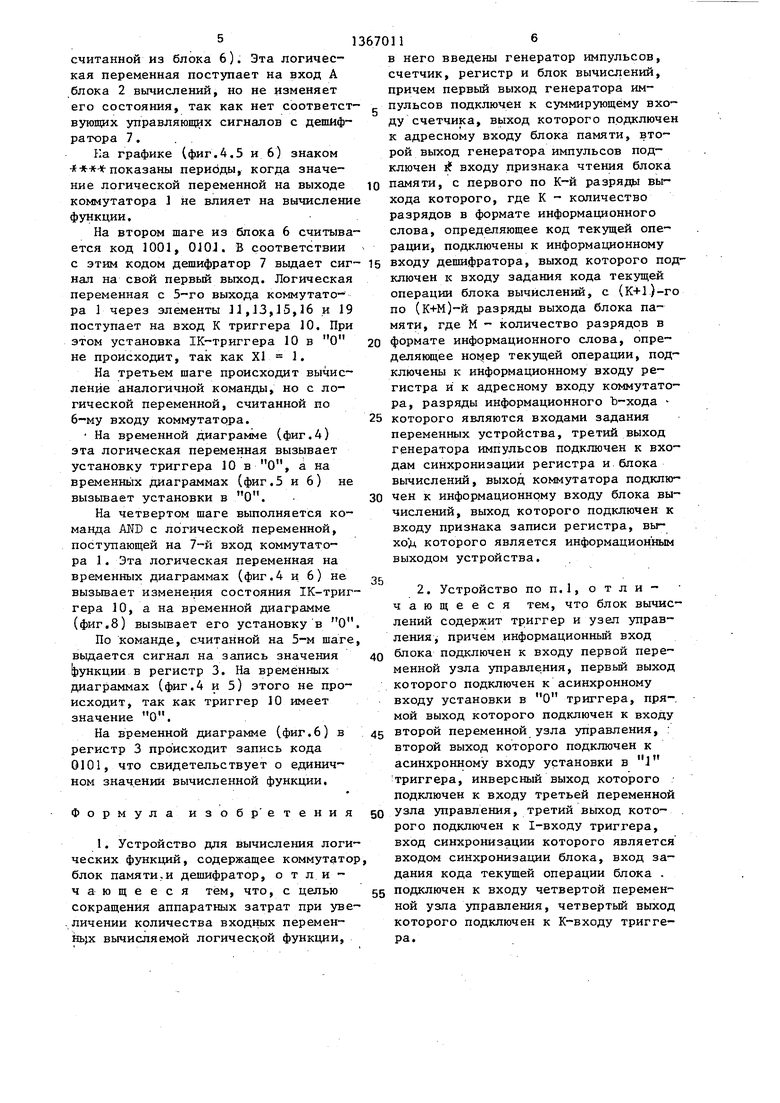

На фиг.1 изображена функциональ ная схема устройства; на фиг.2 - пример функциональной схемы коммутатора на фиг.З - пример функциональной схемы блока вычислений; на фиг,4 - временная диаграмма вычисления функции F Х1ЛХ2ЛХЗ при Х, , , где X - обозначение входной переменной; на фиг.З - временная диаграмма вычисления функции F при ,

5

0

Dn- сигнал А1 . Таким образом, при подаче любого кода адреса входной сигнал будет проходить только через одну микросхему D или D .

Микросхема, включенная разрядом А1, передает на выход в линию А входной сигнал в соответствии с кодом адреса А2, A3. А4. Таким образом, по линии А всегда будет проходить один из входных сигналов.

Блок 2 вычислений содержит триггер 10 и злементы И-НЕ U-26 узла управления.

Устройство, работает следующим образом.

Основу вычисления логических функций составляют операции, выполняемые 1К-триггером 10.

Логические переменные в порядке очереди, заданной программой вычисления функции, поступают на вход А блока 2 вычислений, который в соответствии с командой, поданной на его

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Управляющая логическая машина | 1974 |

|

SU539301A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для микропрограммного управления и контроля | 1987 |

|

SU1497621A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Управляющая логическая машина | 1975 |

|

SU532862A1 |

| Устройство для вычисления непрерывно-логических функций | 1989 |

|

SU1695289A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах, требующих вычис- ления большого количества сложных логических.функций от многих переменных, в частности в системах технической диагностики отказов, распознавания особых ситуаций на борту летательного аппарата, а также в системах управления технологическими процессами. Целью изобретения является сокращение оборудования при увеличении количества входных переменных вычисляемой логической функции.Устройство содержит коммутатор 1, блок 2 вычислений, регистр 3, генератор 4 импульсов, счетчик 5, блок 6 памяти, дешифратор 7, информационный вход 8, информационный выход 9. В блоке 6 хранятся команды и применено последовательное решение логических функций нескольких переменных. Основным узлом для вычисления логических функций является блок 2 вычислений, объем оборудования которого не зависит от количества входных логических переменных, что позволя-ет резко снизить необходимый объем блока 6 памяти при увеличении количества входных логических переменных. 1 з,п.ф-лы,2 табл. 6 ил. g (Л

и на фиг.6 - временная диаграм- 25 вход В из дешифратора 7, передает

ма вычисления функции F при .

Устройство содержит коммутатор 1, блок 2 вычислений, регистр 3, генератор 4 импульсов, счетчик 5, блок 6 памяти, дешифратор 7, информационный вход 8, информационный выход 9.

Пример исполнения коммутатора 1 для 16 логических переменных показан

Микросхе- типа

на микросхемах 1 , D,. мы D и D, - типа 564КП2, 564 ЛА9 или им подобные.

На входы XI,...Х4 коммутатора J подается 4-разрядньм код с выхода регистра 3.

На входы А1,;..А4 поступает 4-разрядный код адреса.с выхода блока 6 памяти, 12 входных логических переменных поступают на входы Х5,...Х16. Микросхемы D и D „ предназначены доя коммутации аналоговых и цифровых сигналов и имеют три состояния по выходу X: логический уровень сигнала логический уровень сигнала 0 высокое выходное сопротивление,

В состоянии высокого выходного сопротивления выход X заперт для про- текайия тока в любом направлении. Для приведения D или Б„ в третье состояние необходимо на вход Е микро схемы подать сигнал Р уровня логической единицы.

На вход F микросхемы D поступает сигнал А1, а на вход Е микросхемы

0

5

0

5

эти логические переменные в прямой :. или инверсном виде на входы I и (или) К триггера 10, При этом подача инверсного значения логической переменной на вход К соответствует операции логического умножения данной логической переменной на результат предыдущего вычисления, хранящихся в 1К-триггере 10. Подача прямого значения логической переменной на вход I соответствует операции ИЛИ между данной логической переменной и результатом вьшолнения предыдущей операции, хранящимся в 1К-триггере 10. Аналогично подача логической переменной на входы I и К одновременно соответствует операции сложения по mod.2.

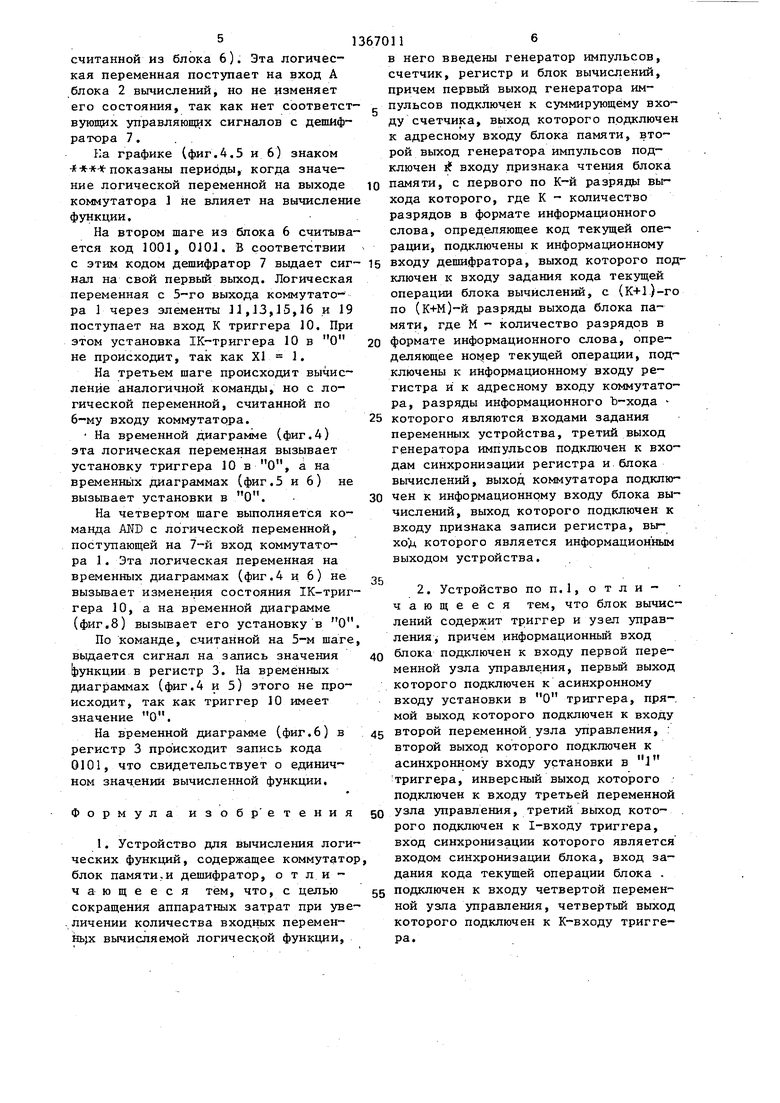

Операции, вьшолняемые триггером 2, описаны в табл.. Для удобства эти операции обозначены мнемокодами.

Сущность вычисления с помощью 1К-триггера JO заключается в том,что . при выполнении команды 10R с логической переменной, им еющей единичное значение, результат также примет . единичное значение. При выполнении.

команды MD результат будет сброшен,

если логическая переменная равна ную. Сложение по mod 2, в свою очередь, представляет из себя подачу логических переменных на счетный вход

и инверсию результата единичными значениями логических переменных.

Пример. Вычислить логичес- . кую функцию Fg . ,.ЛХ

Программа вычисления будет выгля-- деть следующим образом:

IOR 08;

Программа будет щим образом: SLE 00; XOR 08; XOR 05;

XOR

STI

п;

При решении более сложных функций регистр 3 можно использовать для хранения промежуточных результатов.

Например, решим функцию следукнце- го вида:

5

11

,.

. -(х ) ч. Xg .

в реальном случае решение можно упростить, но для иллюстрации метода оставим ее без изменения. Для составления программ примем, что регистр 3 имеет четыре разряда и они заведены на вход коммутатора 1 адресам 00, 01, 02 и 03 соответственно. В программе справа от операндов написаны следующие комментарии:

-обнуление управляющего триггера;

-обнуление управляющего регистра;

вычисление первого произведения;

запись в управляющий регистр промежуточного результата;

8ССЕ

9AND

10AND

11AND

12СМЕ

13IOR

14STI

вычисление второго произведения;

сложение результата; запись промежуточного результата;

вычисление треьего произведения;

0

5

0

5

0

5

0

5

-сложение результата;

-запись решения в управляющий регистр.

После вычисления функции регистр 3 принимает либо нулевое значение (если функдия логических переменных равна нулю/, либо значение равное номеру вычисленной функции. Код функции может быть использован в дальнейших алгоритмах вычисления, а также во внешних устройствах.

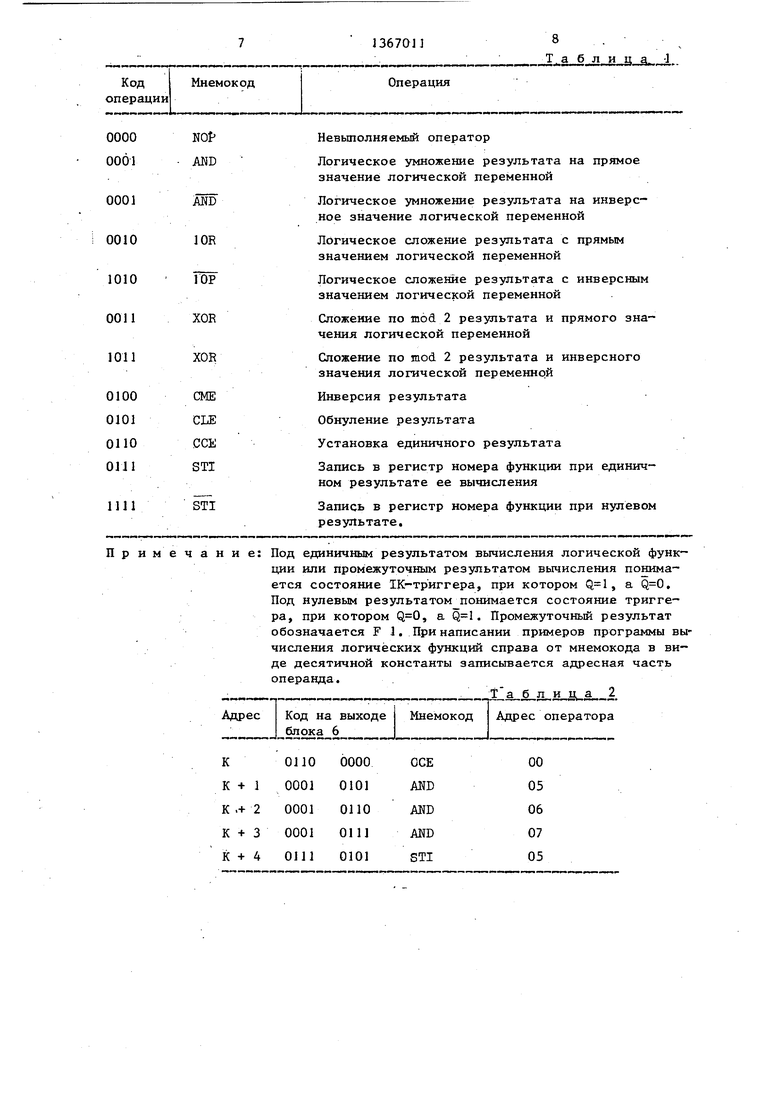

Проиллюстрируем работы предлагаемого устройства временной диаграммой.

Предположим,что логические переменные XI , Х2 и ХЗ поступают на выходы Х5, Хб и Х7 коммутатора 1 соответственно. Кроме того, предположим, что функция F XI Л Х2 Л ХЗ имеет произвольно взятый номер 5. Для вы-- числения этой функции необходимо выполнить программу, представленную в табл.2.

Результат вычисления первой, второй и третьей кодовых комбинаций приведены на фиг.7.8 и 9 соответственно .

Вычисление функции F начинается на шаге К, задаваемом счетчиком 5. В соответствии с адресом К из блока 6 считывается код первой команды 01JO 0000. По переднему фронту импульса С 2 этот код запоминается в буферном регистре блока 6 и сохраняется в нем до прихода следующего сигнала С 2. Код операции ОНО поступает в дешифратор 7. Последний в соответствии с кодом ПО вьщает еди- ницу 6-м разряде позиционного кода. Эта единица устанавливает триггер 10 в единичное состояние.

При выполнении команды на К-м шаге через коммутатор 1 приходит логи- ческая переменная с адресом 0000 согласно адресной части команды.

считанной из блока 6). Эта логическая переменная поступает на вход А блока 2 вычислений, но не изменяет его состояния, так как нет соответствующих управляющих сигналов с дешифратора 7.

На графике (фиг,4,5 и 6) знаком -)t- -K-показаны перибды, когда значение логической переменной на выходе коммутатора не влияет на вычисление функции.

На втором шаге из блока 6 считывается код 1001, OJOJ. В соответствии с этим кодом дешифратор 7 выдает сиг- нал на свой первый выход. Логическая переменная с 5-го выхода коммутато- ра 1 через элементы JJ,13,15,16 и 19 поступает на вход К триггера 10, При этом установка 1К-триггера 10 в О не происходит, так как XI 1,

На третьем шаге происходит вычисление аналогичной команды, но с логической переменной, считанной по 6-му входу коммутатора,

На временной диаграмме (фиг,4) эта логическая переменная вызывает установку триггера 10 в О, а на временнь1х диаграммах (фиг,5 и 6) не

вызьтает установки в О ,

На четвертом шаге выполняется команда МР с логической переменной, поступающей на 7-й вход коммутатора 1, Эта логическая переменная на временных диаграммах (фиг,4 и 6) не вызьшает изменения состояния 1К-триг гера 10, а на временной диаграмме (фиг,8) вызывает его установку в О

По команде, считанной на 5-м шаге вьщается сигнал на запись значения функции в регистр 3, На временных диаграммах (фиг,4 и 5) этого не происходит, так как триггер 10 имеет значение О,

На временной диаграмме (фиг,6) в регистр 3 происходит запись кода 0101, что свидетельствует о единичном значении вычисленной функции,

Формула изобр етения

5 0

5

0

г

в него введены генератор импульсов, счетчик, регистр и блок вычислений, причем первый выход генератора импульсов подключен к суммирующему входу счетчика, выход которого подключен к адресному входу блока памяти, второй выход генератора импульсов подключен if входу признака чтения блока памяти, с первого по К-й разряды выхода которого, где К - количество разрядов в формате информационного слова, определяющее код текущей операции, подключены к информационному входу дешифратора, выход которого подключен к входу задания кода текущей операции блока вычислений, с (К+1-)-го по (К+М)-й разряды выхода блока памяти, где М - количество разрядов в формате информационного слова, определяющее HObiep текущей операции, подключены к информационному входу регистра и к адресному входу коммутатора, разряды информационного Ъ-хода которого являются входами задания переменных устройства, третий выход генератора импульсов подключен к входам синхронизации регистра и блока вычислений, выход коммутатора подключен к информационному входу блока вычислений, выход которого подключен к входу признака записи регистра, выход которого является информационным выходом устройства.

2, Устройство поп,1, отличающееся тем, что блок вычислений содержит триггер и узел управления, причем информационньй вход блока подключен к входу первой переменной узла управления, первьй выход которого подключен к асинхронному входу установки в О триггера, пря-. мой выход которого подключен к входу второй переменной узла управления, : второй выход которого подключен к асинхронному входу установки в J триггера, инверсный выход которого подключен к входу третьей переменной узла управления, третий выход которого подключен к 1-входу триггера, вход синхронизации которого является входом синхронизации блока, вход задания кода текущей операции блока . подключен к входу четвертой переменной узла управления, четвертый выход которого подключен к К-входу триггера.

Невьшолняемьй оператор

Логическое умножение результата на прямое значение логической переменной

Логическое умножение результата на инверсное значение логической переменной

Логическое сложение результата с прямым значением логической переменной

Логическое сложение результата с инверсным значением логической переменной

Сложение по mod 2 результата и прямого значения логической переменной

Сложение по mod 2 результата и инверсного значения логической переменной

Инверсия результата

Обнуление результата

Установка единичного результата

Запись в регистр номера функции при единичном результате ее вычисления

Запись в регистр номера функции при нулево результате.

Примечание;

Под единичным результатом вычисления логической функции или промежуточным результатом вычисления понимается состояние 1К-триггера, при котором Q, а . Под нулевым результатом понимается состояние триггера, при котором , а Q. Промежуточный результат обозначается F J, При написании примеров программы вычисления логических функций справа от мнемокода в виде десятичной константы записывается адресная часть операнда. .

Т.а б лица, -J

Операция

In п п п п п п п t

XI

хз

Мрес S ситчике

Код из длока 6

Код новы xoffe дв- шишрап paf

Выхо9{3-К триггера

10)

# t

Выыдрештра 1{од записанный при вычислении пре ьгдущеи срункции

Х5

-х-

Фиг.5

Код на выходе deujugjpamopal

ч t -к

Выкод 3-К триггера Ю

Выкод регистра . 5

Код запас, при вычислении предыдущ. функции .в К(г2ко9Ш

#

| 0 |

|

SU189629A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-15—Публикация

1986-02-10—Подача