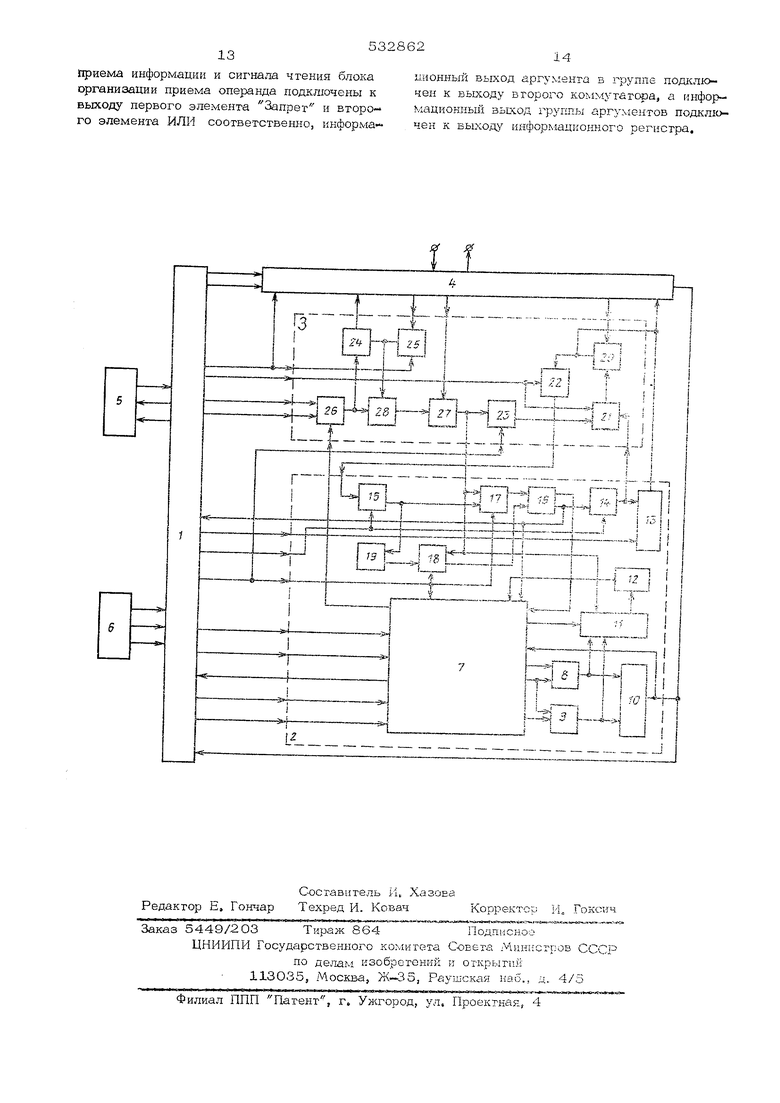

(54) УПРАВЛЯЮЩАЯ ЛОГИЧЕСКАЯ МАШИНА :менгы И, одна группа выходов которых соединена с адресными входами выводной накопительной секции блока ввода-вывода и вместе с шинами, по которым поступают входные сигналы, - с соответствующими входами логической схемы управляющего Наиболее близким техническим решением к данному изобретению является управляющая логическая машина, которая содержит, как и описанные выше блок управления, вы ходы импульсов рабочего цикла, числа скобок, вида скобок, вида логической операции, типа операции, вида аргумента и сигнала записи которого соединены с одновременнь{ми входами логического блока, выходы вычитания скобок, операнда и запрета которого соединены с одноименными входами бло ка управления, информадионпый выход группы аргументов которого соединен с одноименным входом блока сопряжения; а выход существенности этапа вычисления с одноименным входом блока организации приема операнда, информационный выход аргумента в группе и выход сигнала чтения которого соединены с одноименными входами логичес кого блока, входы сигнала приема информации, адреса аргуменх-а в группе и адреса требуемой группы аргументов которого подключены к одноименным выходам блока управления, а выход разрешения приема инфор мации соединен с одноименным входом бло ка сопряжения, входы передачи, воссганов ления и адреса требуемой группы аргументов которого подключены к одноименным вы ходам блока управления. Выход адреса принятой группы аргументов, окончания приема и информационный выход группы аргудменгов соединены с одноименными входами блока организации приема операнда, а выход запр та соединен с одноименным входом блока управления, входы запуска, ручного остан1 ва и задания адреса команды которого подключены к одноименным выходам пульта оператора. Выходы сигнала чтения и адреса команды и информационный вход блока уп равления соединены с одноименными входами и выходом блока памяти команд, а внеш ние входы и выходы блока сопряжения - с соотвегствуюашми входами и выходами уп равляющей логической машины, Во всех известных управгиюших логичес ких машинах, в том числе и в управляющей логической машине - прототипе, для сокращения объема передаваемой информации меж ду управляющей логической машиной, источриками и приемниками информации логической переменной ставится в соответс Ьие один двоичный разряд полноразрядного йнформационного слова. Поэтому во всех известных управляющих логических машинах для вычисления очередного значения логической переменной на оснсве ранее вычисленных значений логических переменных д также при передаче нового значения логического управляющего воздействия на устройство необходимо выполнять процедуры выделения заданного разряда в ин- формационном слове и запись нового значе- ния логической функции в определенный ра ряд информационного слова без изменения 0начений других разрядов. Во всех известных управляющих логических машинах, эти процедуры выполняются программно, на что расходуется значительная часть производительности управляющей логической машины и требуется определ.енный объем памяти команд, Цель изобретения - повышение производительности управляющей логической машины, уменьшение аппаратурных аатрат и эколлуатационных расходов. Для этого в управляющей логической Maшине выход типа операции блока управления соединен с одноименным входом блока организации приема операнда, вход сигнала перезаписи которого подключен к одноименному выходу блока управления, информади- онны-й выход группы аргументов соединен с одноименн.ым в :одом блока сопряжения, а информационный вход резулы ага вычисления подключен к одноименному выходу логического блока. Кроме того, логический блок содержит узел выделения несущественного этапа вычисления, регистр запоминания резульгатоБ, элементы Эквивалент- ность, логические элементы, триггер запоминания результата, дешифратор нулевого состояния, реверсивный счетчик скобок и тригтеры и правых скобок, единичные выходы которых соединены, соответственно, с первыми к вторыми входами элемента ИЛИ и реверсивного счетчика скобок. Выход последнего соединен с входом дешифратора нулевого состояния, выход первого элемента Эквивалентность соединен с первьтм входом первого элемента И непосредственно, а с первым входом второго элемента И -- через элемент НЕ, Выходы первого и вгорого элементов И соединены соогвегственно с единичным и нулевым входами триггера запоминания результата, единичный выход которого через второй аледменг Эквиваленгиость соединен с первым входом регистра запоминания результатов. Единичный и нулевой выходы триггера запоминания результата, выход дешифратора нулевого состояния и выход элемента ИЛИ соединены с соотвегствующими входам узла вьщеления несущественного этапа вы числения, соответствующие выходы которог соединены с третьим входом реверсивного счетчика скобок и единичными и нулевыми входами триггеров левых и правых скобок, Зходы импульсов рабочего цикла, числа ско бок, вида скобок и вида логической операции логического блока соединены с одноиме ными входами узла выделения несуществен- ного этапа вычисления. Вход типа операции соединен с одноименным входом узла вьщеления несущественного этапа вычисления и вторыми входами элементов И, Вход вида аргумента соединен с первым входом первого и с вторым входом второго элементов Эквивалентность. Вход сигнала записи соединен с вторым входом регистра запоминания результатов, информационный вход соединен с вторым входом первого элемента Эквивалентность а вход сигнала чтения соединен с третьими входами элементов И и четвертым входом реверсивного счетчика скобок. Выходы вычитания скобок и существенности этапа вычисления логичео кого блока подключены к одноименным выходам узла выделения несущественного этапа вычисления. Выход операнда подключен к единичному выходу триггера запоминания результата, информационный выход результата вычисления подключен к выходу второго элемента Эквивалентность, информационный выход группы аргументов подключен к выходу регистра запоминания результатов, а выход запрета подключен к выходу элемента ИЛИ, Кроме того, блок органи зации приема операндов содержит первый коммутатор, информационный регистр, второй коммутатор, узел сравнения адресов, элементы Запрет, элемент И и элементы ИЛИ. Выход первого из элементов ИЛИ соединен с первыми входами элемента И и первого элемента Запрет, подключенными вторыми входами к выходу узла сравнения адресов. Выход элемента И через последовательно соединенные второй элемент ИЛИ и второй элемент Запрет соединен с первым входом первого коммутатора, выход которого соединен с первым входом информационного регистра, а его выход соединен с первым входом второго коммутатора. Входы существенности этапа вычисления, сигнала перезаписи и сигнала приема информации блока организации приема операнда соединены с соответствук шими входами первого элемента ИЛИ. Вход адреса аргумента в группе соединен с вторым входами первого и второго коммутаторов, входы типа операции, адреса требуемой группы аргументов, адреса принятой группы аргументов и окончания приема соединены, соответственно, с другим входом второго элемента Запрет, первым входом узла сравнения адресов, вторым входом узла сравнения адресов и другим входом второго элемента ИЛИ. Информационный вход группы аргументов соединен с вторым входом информационного регистра, а информационный вход результата вычисления соединен с третьим входом первого коммутатора. Выходы разрешения приема информации и сигнала чтения блока организации приема операнда подключены к выходу первого элемента Запрет и второго элемента ИЛИ, соответственно, информационный выход аргумента в группе подключен к выходу второго коммутатора, а информационный выход группы аргументов подключен к выходу информационного регистра. На чертеже изображена функциональная схема управляющей логической мащины. Управляющая логическая мащина содержит блок управления 1, логический блок 2, блок организации приема операнда 3, блок сопряжения 4, блок памяти команд 5 и пульт оператора 6. Логический блок 2 содержит узел выделения несущественного этапа вычисления 7, триггер левых скобок 8, триггер правых скобок 9, элемент ИЛИ 1О, реверсивный счетчик скобок 11, дещифратор нулевого состояния 12, регистр запоминания результатов 13, элементы Эквивалентность 14 и 15, триггер запоминания результата 16, элементы И 17 и 18 и элемент НЕ 19. Блок организации приема операнда 3 содержит информационный регистр 20, первый коммутатор 21, второй коммутатор 22, элемент Запрет 23 и 24, узел сравнения адресов 25, элементы ИЛИ 26 и 27 и элемент И 28. Работа управляющей логической машины в режиме обновления значения логической переменной в некотором двоичном разряде многоразрядного информационного слоя. Управляющая логическая мащина имеет дополнительно две служебные команды: Перезапись и Восстановление. По команде Перезапись в информационный регистр 2О блока организации приема операнда 3 через внещний вход блока сопряжения 4 осуществляется ввод того многоразрядного информационного слова, адрес которого указан в первой адресной части команды Перезапись, По окончании ввода многоразрядного информационного слова в двоичный разряд, номер которого указан во второй адресной части команды Перезапись, записывается с выхода элемента Эквивалентность 14 новое (прямое или инверсное.

в соогвегсгвии с признаком в операционной части команды) вычисленное значение логи-ческой переменной.

По команде Воссгановление многоразрядное информационное слово с информациоцнего регистра 20 блока организации приема операнда 3 передается на внешний выход блока сопряжения 4. В адресной части команды Воссгановление указан адрес внеш него устройства (на чертеже не показано), которому это слово адресуется.

Например, требуется обновить значение логической переменной, находящееся в В-ом разряде многоразрядного информационного слова, расположенного во внешнем устройстве, имеющем адрес А , и передать это слово с обновленным значением В-го разряда во внешнее устройство, имеющее адрес А

Подпрограмма обновления значения логи- ческой переменной в В-ом двоичном разряде А многоразрядного информационного слова состоит из двух команд и записывается следующим образом:

Перезапись ,

Восстановление выполнении первой кома1щы поднрог ралммы с кодом операции Перезапись на выходе сигнала перезаписи блока управления 1, подключенном через одноименный вход блока организации приема onepatma 3 к входу элемента ИЛИ 26, формируется сигнал логической 1

Адрес А с выхода адреса требуемой группы аргументов блока управления 1 поступает на одноименные входы блока сопряжения 4 и блока организации приема операнда З, Вход адреса требуемой группы аргу-ментов блока организации приема операнда 3 подключен к первому входу узла сравне™ ния адресОВ 25, второй вход которого подключен к входу адреса принятой грунпы блока организации приема onepaiwa 3, подключенного к одноименному выходу блока сопряжения 4,

Если адрес А не совпадает с адресом С, принятым в информационный регистр 20 |при выполнении одной из предыдущих ко манд программы группы аргументов, то на выходе узла сравнения адресов 25 формируется сигнал логического О, Если же А S С, то на выходе узла сравнения адресов 25 формируется сигнал логической 1

Выход элемента ИЛИ 26 подключен к

первым входам элементов И 28, и Запрет 24, вторые входы которых подключены к выходу узла сравнения адресов 25.

Выход элемента И 28 подключен к вхо ду элемента ИЛИ 27, другой вход которо-

го подключен к выходу окончания приема блока сопряжения 4 через одноименный вход блока организации приема операнда 3.

Выход элемента Запрет 24 подключен к входу разрещения приема информации блока сопряжения 4 через одноименный блока организации приема операнда 3,

Если А, С, то на входе разрешения приема информации блока сопряжения 4, подключенном к одноименному выходу блока организации приема операнда 3, формируется сигнал Прием информации.

Если А С, то в блок сопряжения 4 по цепи: выход сигнала перезаписи блока управления 1 - вход сигнала перезаписи блока организации приема операнда 3 - эход и выход элемента ИЛИ 26 - вход и выход элемента Запрет 24 - выход разрешения приема информации блока организации приема операнда 3 - вход разрешения информации блока сопряжения 4, поступает сигнал Прием информации. По этому сигналу блок сопряжения 4 на внешней свой выход выдает адрес А, внешнего устройс ва (на чертеже не показано); а с внешнего входа принимает многоразрядное информационное слово, которое записывается в информационный регистр 20, Первый вход этого регистра подключен к информационному выходу группы аргументов блока сопряжения 4- через одноименный вход блока организации приема операнда 3. По окончании приема информации на выходе элемента ИЛИ 27 вход которого подключен к выходу окончания приема блока сопряжения 4 через од- роименный вход блока организации приема операнда 3, формируется сигнал Чтение.

На все время работы блока сопряжения 4 сигналом с его выхода запрета, подклю-г

ченного к одноименному входу блока управления 1. запрещается формирование после довательности управляюш;их импульсов на выходе импульсов рабочего цикла блока управления 1,

Если А. н С, то сигнал Чтение формируется по цепи: выход сигна.ла перезаписи блока управления 1 вход сигнала перезаписи блока организации приема операнда 3 - вход и выход элемента ИЛИ 26 - вход ,и выход элемента И 28 - вход и выход элемента ИЛИ 27, Выход элемента ИЛИ 27 с одной стороны подключен к входу элемента Запрет 23, а с другой через выход сигнаг ла чтения блока организации приема операн да 3 и одноименный вход логического блока 2 к входам элементов И 17 и 18

На другие входы элементов Запрет 23 и И 17, 18 поступает сигнал логического О с выхода типа операции бло.ка управления 1 через одноименные входы блока орга низации приема операнда 3 и логического блока 2, соотвегственно.

Таким образом, при выполнении команды с кодом операции Перезапись действие сигнала Чтение в логическом блоке 2 .блокируется подачей на один из входов эле-iМентов И 17, 18 сигнала логического О,

Выход элемента Запрет 23 подключен k первому входу коммутатора 21, на второ вход которого поступает адрес В с выхода адреса аргумента в группе блока управлени 1 через одноименный вход блока организации приема операнда 3, Единичный выход триггера запоминания результата 16 через последовательно соединенные элемент Эквивалентность 14, информационный выход результата вычисления логического блока 2 и одноименный вход блока организации приема операнда 3 соединен с третьим входом коммутатора 21 Другой вход элемента Эквиваленгность 14 через вход вида аргумента логического блока 2 подключен к одноименному выходу блока управления 1, Логическое значение сигнала на выходе Ьида аргумента определяется информацией, записанной в операционной части выполняемой команды, и равно 1, если в В-ый раэряд информационного регистра 20 надо записать прямое значение результата вычисления, хранящегося в триггере запоминания результата 16, в противном случае оно равно О. Выход коммутатора 21 подключен к вхо ду информациоидого регистра 20, Таким образом, по сигналу Чтение прямое или инверсное значение результата вычисления, хранящееся в триггере запоминания результата 16, запишется в разряд информационного регистра 2О, При выполнении второй команды подпрог раммы с кодом операции Восстановление с выхода восстановления блока управления 1 через одноименный, вход в блок сопряжения 4 поступает сигнал Передача из информационного регистра 20, По этому сигналу на внешний выход блока сопряжения 4 передается следующая информация:-адрес А внешнего устройства (на чертеже не показа.но), -многоразрядное информационное слово, хранящееся в информационном регистре 20. С этой целью выход адреса требуемой группы аргументов блока управления 1 соединен с одноименным входом блока сопряжения 4, а выход информационного регист°ра 20 через информационный выход группы

аргументов блока организации приема операнда 3 соединен с одноименным входом блока сопряжения 4.

На время работы блока сопряжения 4 блокируется выход импульсов рабочего цик ла блока управления 1. С этой целью выход запрета блока сопряжения 4 соединен с одноименным входом блока управления 1,

Использование новых элементов в струк туре управляющей логической машины введение дополнительных управ тяющих и информационных связей между входящими в ее состав функциональными блоками - элементами структуры, выгодно отличает предлагаемую управляющую логическую мащину от известных, гак как повышается проиэводдятелькосгь при одиоЕременном уменьшении аппаратурных затрат и экспллатационных расходов. 3 о о р о р м у л е н и я 1, Управляющая логическая машина, содерл ащая блок управления, выходы импульсов рабочего циклЗ; числа скобок, вида CKo6oKj вида логической операции, типа операции, вида аргзмента и сигнала записи которого соединены с одноименными входами логического блока, выходы вычитания скобок, операнда и запрета которого соединены с одноименными входами блока управления, информационный выход группы аргументов которого соединен с одноименным входом блока сопряжения, а выход суш.ественности этапа вычисления - с одно- яменны ч входом блока организации приема операнда, информацконный выход аргумента р группе и выход сигнала чтения которого соединены с одноименными входами логического блока, входы сигнала приема информации, адреса аргумента в группе и адреса требуемой группы аргументов которого подключены к oднoимeнны.I выходам блока управления, а выход разрешения приема информации соединен с одноименным входом блока сопряжения, входы передачи, восстановления и адреса требуемой группы аргументов которого подключены к одноименным выходам блока управления, выходы адреса принятой группы аргументов, окончания приема и информацконнь й выход группы аргументов соединены с одноименными входами блока организации приема операнда, а выход запрета соединен с одноименным входом блока управления, входы запуска, ручного останова и задания адреса команды которого подк.лючены к одноименным выходам пульта оператора, вььчоды сигнала чтения и адреса команды и информационный

вход блока управления соединены с одноименными входами и выходом блока намяги команд, а внешние входы и выходы блока сопряжения - с соответствующими входами и выходами управляющей логической, машины, отличающаяся тем, ч го, с целью повышения производительности, уменшения аппаратурных затрат и эксплуатационных расходов, в ней выход типа операции блока управления соединен с одноименным входом блока организации приема операнда вход сигнала перезаписи которого подключе к одноименному выходу блока управления, информационный выход группы аргументов соединен с одноименным входом блока со- пряжения, а информационный вход результата вычисления подключен к одноименному выходу логического блока.

2, Машина по п, 1, отличаю- щ а я с я тем, что логический блок содержит узел выделения несущественного этапа вычисления, регистр запоминания результатов, элементы Эквивалентность логические элементы, триггер запоминания результата, дешифратор нулевого состояния реверсивный счетчик скобок и триггеры левых и правых скобок, единичные выходы которых соединены, соответственно, с первыми и вторыми входами элемента ИЛИ и реверсивного счетчика скобок, выход которого соединен с входом дешифратора нулевого состояния, выход нервого элемента Эквивалентность соединен с первым входом первого элемента И непосредственно, а с первым входом второго элемента И - через элемент НЕ, выход первого и второго элементов И соединены соответственно с единичным и нулевым входами триггера запоминания результата, единичный выход которого через второй элемент Эквивалентность соединен с первым входом регистра запоминания результатов, единичный и нулевой выходы триггера запоминания результата, выход дешифратора нулевого состояния и выход элемента ИЛИ соединены с соответствующими входами узла выделения несущественного этапа вычисления соответствующие выходы которого соединены с третьим входом реверсивного счетчика скобок и единичными и нулевыми входами три1 геров левых и правых скобок, входы импульсов рабочего цикла, числО скобок вида скобок и вида логической операции логического блока соединены с одноиме ными входами узла вы деления несуществен Ноге этапа вычисления, вход типа операции соединен с одноименным входом узла вьще- дения несущественного этапа вычисления и вторыми входами элементов И, вход ви-

да аргумента соединен с первым входом первого и со вторым входом второго элемента Эквивалентность, вход сигнала записи соединен со вторым входом регистра запоминания результатов, информационный вход соединен со вторым входом первого элемента Эквивалентность, а вход сигнала чтения соединен с третьими входами элементов И и четвертым входом реверсив кого счетчика скобок, выходы вычитания скобок и существенности этапа вычисления логического блока подключены к одноименным выходам узла выделения несущественного этапа вычисления, выход операнда подключен к единичному выходу триггера запоминания результата, информационный выход результата вычисления подключен к выходу второго элемента Эквивалентность информационный выход группы аргументов подключен к выходу регистра запоминания результатов, а выход запрета подключен к выходу элемента ИЛИ.

3, Машина по п. 1, отличающаяся тем, что блок организации приема операндов содержит первый коммутатор, информационный регистр, второй коммутатор, узел сравнения адресов, элементы Запрет, элемент И и элементы ИЛИ, выход первого из которых соединен с первыми входами элемента И и первого элемента Запрет, подключенными вторыми входами к выходу узла сравнения адресов, выход элемента И через последовательно соедине ные второй элемент ИЛИ и второй элемент Запретсоединен с первым входом первого коммутатора, выход которого соединен с первым входом информационного регистра, выход которого соединен с первым входом второго коммутатора, входы существенности этапа вычисления, сигналл перезаписи и сигнала приема информации блока организации приема операнда соединены с соответствующими входами первого элемента ИЛИ, вход адреса аргумен та в группе соединен со вторыми входами первого и второго коммутаторов, входы типа операции, адреса требуемой группы аргументов, адреса принятой группы аргументов и око1гчания приема соединены соответстве нс с другим входом второго элемента Запрет, первым входом узла сравнения адресов, вторым входом узла сравнения адресов и другим входом второго элемента ИЛИ, информационный вход группы аргументов соединен со вторым входом информационного регистра, а информационный вход результата вычисления соединен с третьим входом первого коммутатора, выходы разрешения

Приема информации и сигнала чтения блока организации приема операнда подключены к выходу первого элемента Запрет и второго элемента ИЛИ соответственно, кнформаиионный выход аргумента в группе подключен к выходу второго коммутатора, а информационный выход группы аргументов подключен к выходу информационного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая логическая машина | 1974 |

|

SU539301A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Адаптивное вычислительное устройство | 1984 |

|

SU1203506A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Устройство для табличной реализации многоместных логических функций | 1982 |

|

SU1019455A1 |

Авторы

Даты

1976-10-25—Публикация

1975-05-13—Подача