0-

7 ./

.н-и

00 05

|

ел

1367

5 и 8 импульсов, элемент ИЛИ 6, элемент 2ИЛИ-И-НЕ 7 и блок 9 управления. Введение в параллельно-последовательный аналого-цифровой преобразователь перечисленных выше узлов с соответствующими связями обеспечивает такое функционирование устройства, при ко

тором сигнал с вычитающего устройства не выходит за пределы рабочего . диапазона второго аналого-цифрового преобразователя, что позволяет полностью исключить грубые ошибки измерений на участках стыковки грубой и точной шкал. 1 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательно-параллельный аналого-цифровой преобразователь | 1981 |

|

SU972658A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907795A1 |

| Устройство для измерения дрейфа аналого-цифровых преобразователей | 1981 |

|

SU991599A1 |

| Устройство задержки | 1984 |

|

SU1233270A2 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1003331A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Устройство для аналого-цифрового преобразования | 1984 |

|

SU1226663A1 |

| Измеритель характеристик аналого- цифРОВыХ пРЕОбРАзОВАТЕлЕй | 1978 |

|

SU819950A1 |

Изобретение относится.к информационно-измерительной технике и может использоваться в радиолокации, экспериментальной физике, автоматике и телемеханике. В устройство, содержащее первый и второй аналого-цифровые преобразователи 1 и 2, цифроана- логовый преобразователь 3 и блок 4 вычитания, с целью устранения грубых погрешностей измерений в областях стыковки точной и грубой шкал двух- шкапьного аналого-цифрового преобразователя при одновременном снижении требований к точности первого аналого-цифрового преобразователя, введены первый и второй двоичные счетчики с S (Л

1

Изобретение относится к контроль-, но-измерительной технике и может ис-, пользоваться в радиолокации, тгелеви- дении, экспериментальной физике, автоматике и телемеханике.

Цель изобретения - устранение грубых погрешностей измерений в областях стыковки точной и грубой шкап двухшкального аналого-цифрового преобразователя при одновременном снижении требований к точности первого аналого-цифрового преобразователя.

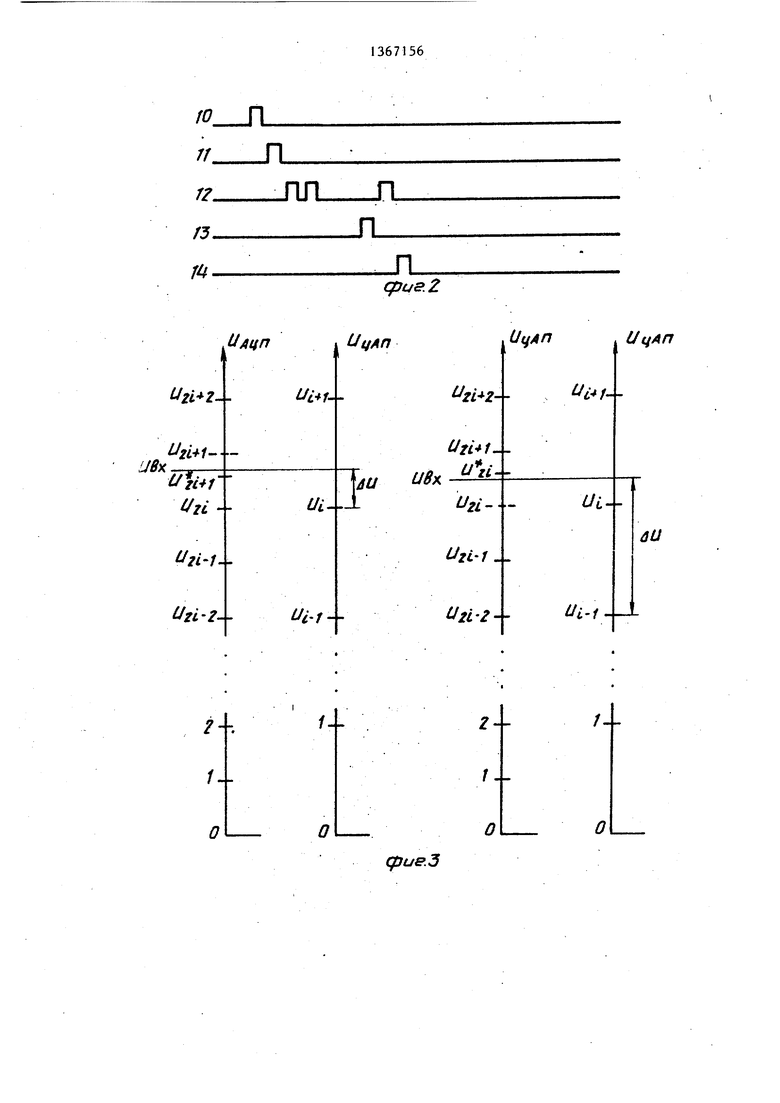

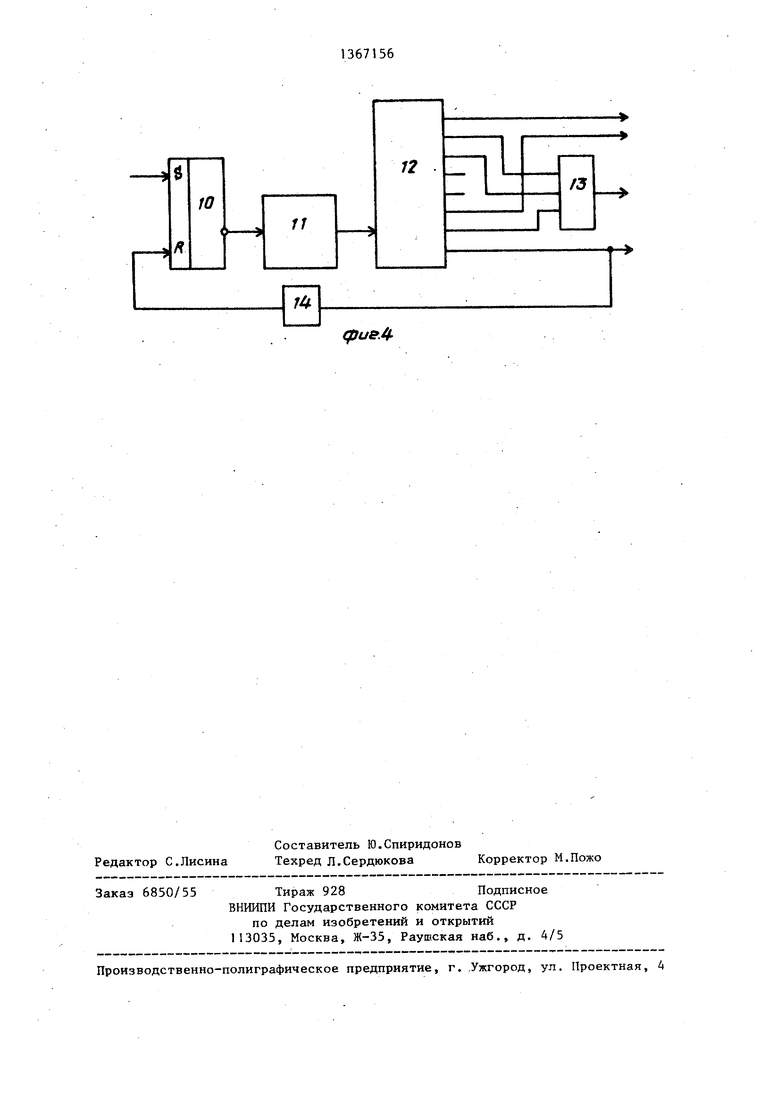

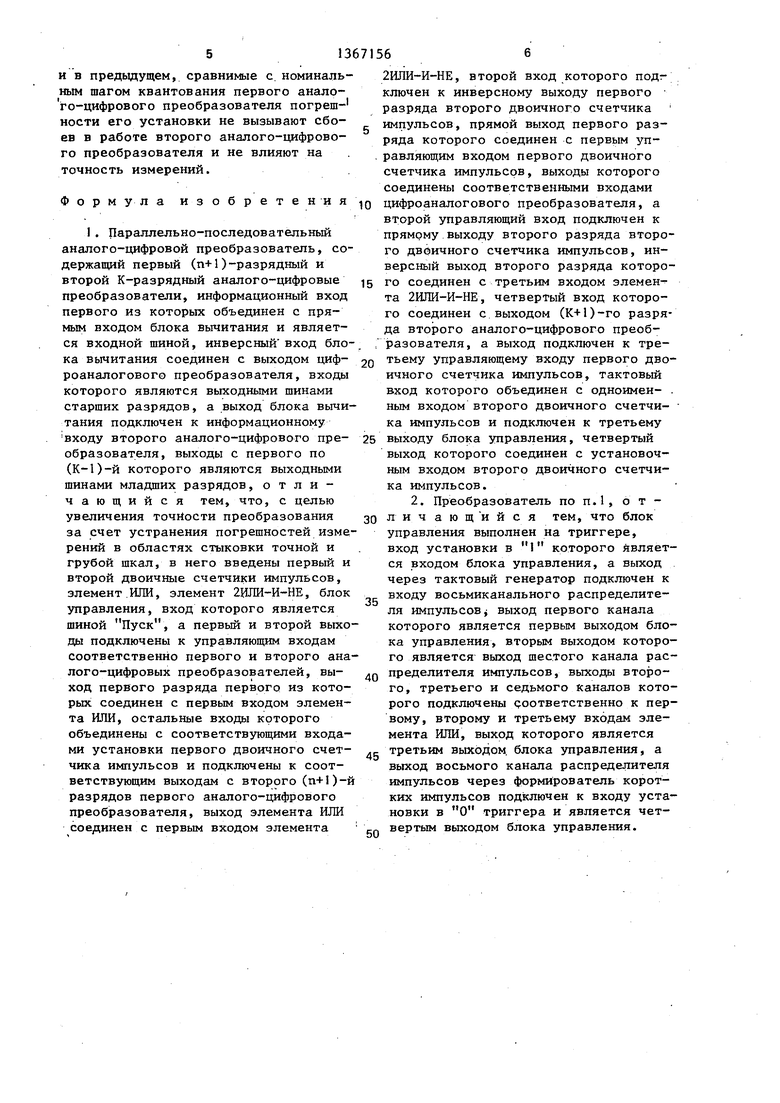

На фиг.1 изображена структурная схема двухшкального аналого-цифрового преобразователя; на фиг.2 и 3 - диаграммы, поясняюш;ие работу устройства; на фиг.4 - структурная схема блока управления.

Преобразователь содержит первый и второй аналого-цифровые преобразователи 1 и 2, цифроаналоговый преобразователь 3, блок 4 вычитания, первый двоичный счетчик 5, логический элемент ИЛИ 6,,логический элемент 2ИЛИ-И-НЕ 7, второй двоичный счетчик 8, блок 9 управления. Блок управления выполнен на триггере 10, тактовом генераторе 11, восьмиканальном распределителе 12 импульсов, элементе ИЛИ 13, формирователе 14 коротких импульсов.

Процесс кодирования входного напряжения начинается по сигналу Пуск 10, поступающему на вход блока 9 уп- равления. По этому сигналу блок управления вырабатывает серию управляющих сигналов 11-14. Сигналом 11 с его первого выхода осуществляется стробирование первого аналого-цифрового преобразователя 1, и на выходе последнего появляется пропорциональный входному напряжению двоичный код все разряды которого, кроме младшегб

подаются на информационные входы двоичного счетчика 5. По окончании цикла работы первого аналого-цифрового

преобразователя первым сигналом 12 с третьего выхода блока 9 управления происходит занесение полученного кода в счетчик 5 и переключение в единичное состояние двухразрядного двоичного счетчика 8, который прямым выходом первого разряда переводит первый двоичный счетчик 5 в режим вьпитания, а инверсным выходом первого разряда разблокирует первую половину логического элемента 7. Если выходной сигнал элемента 6 имеет низкий уровень, что соответствует нулевому коду первого аналого-цифрового преобразователя, сигнал высокого

уровня с элемента 7 блокирует операцию счета в счетчике 5. Если код аналого-цифрового преобразователя 1 не нулевой, вторым сигналом 12 с третьего выхода блока управления из кода, записанного в счетчик 5, вычитается единица. .Этим же сигналом в счетчик 8 добавляется единица и он устанавливает код, равный двум. В результате на управляющих входах

счетчика 5 устанавливаются потенциалы, соответствующие режиму сложения .(нуль - на первом управляющем входе и единица - на втором).

Через определенное время, необходимое дпя завершения переходных процессов, в цифроаналоговом преобразователе 3 и блоке 4 вычитания по сигналу 13 с второго выхода блока управления осуществляется запуск второго аналого-цифрового преобразователя.2, на выходе которого появляется код, представляющий собой точные разряды выходного кода устройства. Если результат преобразования аналого-цифрового преобразователя 2 содержит в старшем (К+1)-м разряде единицу, зле- мент 7 переводит счетчик 5 в режим сложения и третьим сигналом 12 с третьего выхода блока 9 управления осуществляется операция добавления единицы в грубый код, записанный ранее в счетчик 5. При нулевом состоянии старшего разряда аналого-цифрового преобразователя 2 сигналом высокого уровня с выхода элемента 7 эта операция по первому управляющему входу

счетчика 5 блокируется. Указанный ал- 15 но пр актически, в отличие от требовагоритм фактически осуществляет операцию суммирования содержимого старшего разряда второго аналого-цифрового преобразователя с грубым кодом, полученным на первом этапе измерений.

Введение в двухшкальный аналого- цифровой преобразователь перечисленных узлов с соответствующими связями позволяет исключить грубые ошибки измерений на участках стыковки грубей и точной шкал и значительно снизить требования к точности первого из входящих в него одношкальных аналого- цифровых преобразователей. С их помощью обеспечивается такое функциони- 30 чие систематических аддитивных пог- рование устройства, при котором уро- решностей в цифроаналоговом преобравень сигнала вычитающего устройства не выходит за пределы рабочего диапазона второго аналого-цифрового преобразователя, соответствующего двум единицам младшего разряда грубой шкалы, даже при больших отклонениях от Номинальных параметров основных узлов устройства.

Предположим, что цифроаналоговый преобразователь, вычитающее устройство и второй аналого-цифровой преобразователь являются идеальными и не вносят погрешностей. Пусть ()-й

зователе и суммирующем устройстве проявляется в смещении порога cjrMM ной функции преобразования, которо

35 может быть легко скорректировано и вестными методами.

Рассмотрим вторую крайнюю ситуа цию, в которой в известном устройс ве возможно нарушение нормального

40 функционирования второго аналого-ц рового преобразователя и появление грубых погрешностей. Для нее 21-й уровень квантования первого аналог . цифрового преобразователя имеет по

нечетный уровень квантования первого 45 ложительнре смещение, а Ug лежит

между 2i-M и (21-1)-м уровнями. Пу при этом выходной код первого анал го-цифрового преобразователя превы шает единицу. Тогда в соответствии с алгоритмом работы устройства сод жимое счетчика по сигналу блока ун равления уменьшается на единицу и разностный сигнал на входе вычитаю щего устройства равен ли UB

аналого-цифрового преобразователя установлен с отрицательной погрешностью uU2; (фиг.4), а измеряемый уровень напряжения Ug лежит между его (21+1)-й и (2i+2)-M уровнями 50 квантования. Тогда в соответствии с рассмотренным алгоритмом работы устройства в результате отбрасывания Мпадшего разряда в выходном коде пермежду 2i-M и (21-1)-м уровнями. Пу при этом выходной код первого анал го-цифрового преобразователя превы шает единицу. Тогда в соответствии с алгоритмом работы устройства сод жимое счетчика по сигналу блока ун равления уменьшается на единицу и разностный сигнал на входе вычитаю щего устройства равен ли UB

вого аналого-цифрового преобразовате- 55 -х Абсолютная величина u,U при

ля на вход вычитающего устройства поступает разностный сигнал i U

и

вх

- U;, где U; - уровень напрядискретизации U,- и U

Z-i Я

Таким о бжения цифроаналогового преобразовате- разом в рассматриваемом случае, как

титься и.;., и.;

ля, соответствующий идеальному положению 2i-ro узла шкалы первого аналого-цифрового преобразователя. Очевидно & и в этом случае может обра- в нуль только тогда, когда

, т.е. абсолютная погрешность установки шага квантования первого аналого-цифрового преобразователя в пределе может быть сравнима с его номинальным значением или с половиной грубого шага квантования всего устройства. Очевидно ,также, что это условие легко может быть удовлетворения к абсолютной погрешности первого аналого-цифрового преобразователя в прототипе, где она должна быть меньше шага квантования по точной шкале.

Аналогично указанному малые отклонения от номинала положений узлов шкапы цифроаналогового преобразователя, а также небольшие систематические погрешности обоих знаков устройства вычитания и второго аналого-цифрового преобразователя не нарушают нормальной работы предлагаемого устройства и не вызывают грубых погрешностей в результате измерений. Нализователе и суммирующем устройстве проявляется в смещении порога cjrMMap- ной функции преобразования, которое

может быть легко скорректировано известными методами.

Рассмотрим вторую крайнюю ситуацию, в которой в известном устройстве возможно нарушение нормального

функционирования второго аналого-цифрового преобразователя и появление . грубых погрешностей. Для нее 21-й уровень квантования первого аналого- . цифрового преобразователя имеет положительнре смещение, а Ug лежит

между 2i-M и (21-1)-м уровнями. Пусть при этом выходной код первого аналого-цифрового преобразователя превышает единицу. Тогда в соответствии с алгоритмом работы устройства содержимое счетчика по сигналу блока ун- равления уменьшается на единицу и разностный сигнал на входе вычитающего устройства равен ли UB

этом не превосходит двух квантов грубой шкалы даже при совпадении уровня

дискретизации U,- и U

Z-i Я

Таким о би в предыдущем, сравнимые с номинальным шагом квантования первого анало- го-цифрового преобразователя погреш- ности его установки не вызывают сбоев в работе второго аналого-цифрового преобразователя и не влияют на точность измерений.

Формула изобретения

2ИЛИ-И-НЕ, второй вход которого подг ключен к инверсному выходу первого разряда второго двоичного счетчика импульсов, прямой выход первого разряда которого соединен с первьгм уп- равляющим входом первого двоичного счетчика импульсов, выходы которого соединены соответственными входами цифроаналогового преобразователя, а второй управляющий вход подключен к прямому выходу второго разряда второго двоичного счетчика импульсов, инверсный выход второго разряда которо- го соединен с третьим входом элемен- та 2Ш1И-И-НЕ, четвертый вход которого соединен с выходом (К+О-го разряда второго аналого-цифрового преоб- разователя, а выход подключен к тре- тьему управляющему входу первого двоичного счетчика импульсов, тактовый вход которого объединен с одноимен- . ным входом второго двоичного счетчика импульсов и подключен к третьему выходу блоиса управления, четвертый выход которого соединен с установочным входом второго двоичного счетчика импульсов.

п п

.-

пп п

л

qp

л

qpLfff.Z

Cjpue.3

10

(ри&Л

12

/5

| Гольденберг Л.М., Бутыльский Ю.Т | |||

| Поляк | |||

| М.Н | |||

| Цифровые устройства на интегральных схемах в технике связи | |||

| М.: Связь, 1979, с | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Бахтиаров Г.Д., Малинин В.В., Школин В.П | |||

| Аналого-цифровые преобразователи | |||

| М.: Сов | |||

| радио, 1980, с | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1988-01-15—Публикация

1986-04-03—Подача