/

со с:)

МиА

О5

at)

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах с кодами Фибоначчи и кодами золотой пропорции.

Цель изобретения - расширение области применения путем преобразования прямого кода в дополнительной.

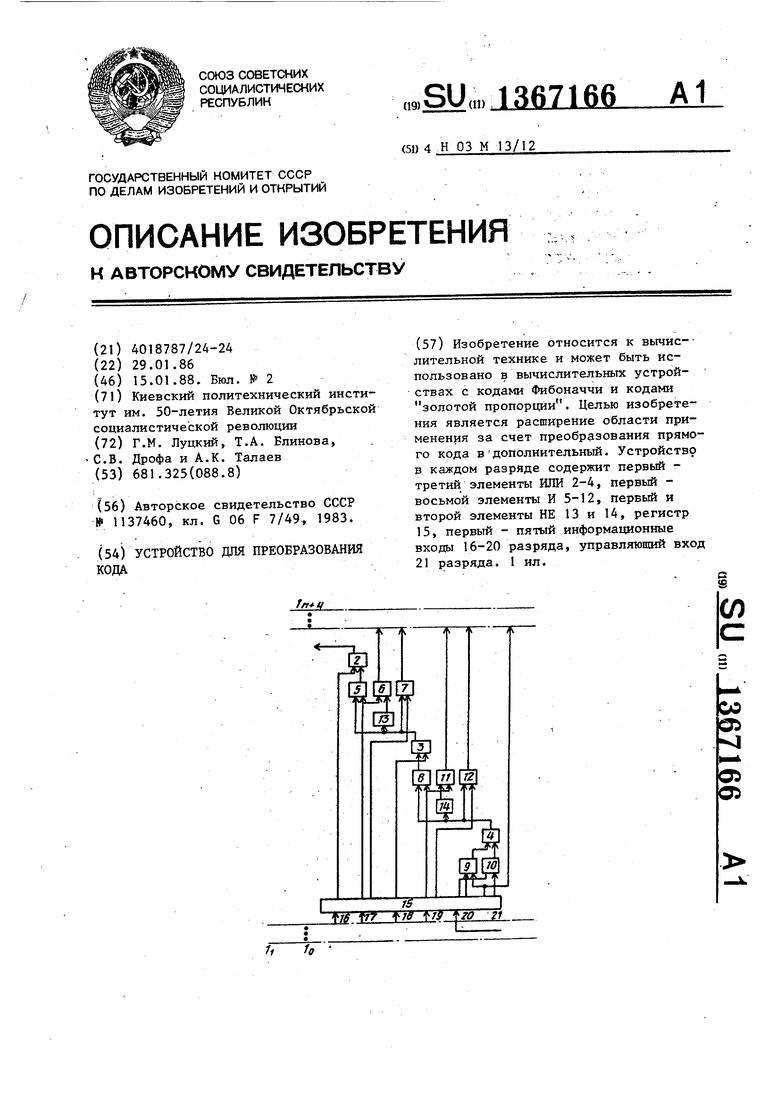

На чертеже представлена схема предлагаемого устройства.

Устройство в каждом разряде lo--- l;...lf,4 содержит первый - третий элементы ИЛИ 2-4, первый - восьмой элементы И 5-12, первый и второй элементы НЕ 13 и 14, регистр 15, первый - пятый информационные входы 16-20 разряда, управляющий вход 21 разряда. .

Устройство работает следующим образом.

Устройство выполняет перевод из прямого кода в дополнительный код чисел, представленных или в золотом 1-коде, или в 1-коде Фибоначчи. При этом операнды представлены в минимизированной форме, содержащей не более двух единиц подряд. Операция выполняется в неавтономном режиме вычислений, т.е. операнды и результаты поступают поразрядно со старших раз- рядов. Разряды результата можно использовать по мере их вычисления, не дожидаясь завершения операции перевода. Для получения дополнительного кода все разряды операнда инвестируются (если число отрицательное) и производится последовательная свертка разрядов, начиная со свертки разрядов С весом (i.° и в разряд с весом oi i ) вместо прибавления единицы в разряд с весом учитьшая 4Tooi-t - -; ц. (6i / 4- -(«47) -tn+i) Производится приписывание единиц к записи кода с последующей сверткой. После приписывания единиц и вб ; и свертки

в разряде с весом 6i ,

должен быть

нуль, поэтому к коду может быть приписана вторая единица «С, I,

Устройство работает следующим образом.

Пусть необходимо представить в дополнительном коде число А„., ZI .

1,ц К«О

Устройство содержит п + 5 разрядов с номерами К 0,1,2,..., п + 4. На управляющий вход нулевого разряда устройства подается знаковый разряд операнда а,, на остальные входы зтого разряда подаются нули. На вход 20 К-го разряда устройства (,2,... ,п) подается, соответствующий разряд операнда а. На входы 20 (п+1)-го и (п+2)-го разрядов устройства подается О, на входы 18 (п+3)-го и (п+4)-го разрядов устройства подается знаковый разряд операнда а. Знаковый разряд а подается также на вход 18 (п+3)-го разряда устройства.

Пример. Рассмотрим работу К-го (,1,2,..., п+4) разряда. Пусть на К-м такте осуществляется прием К-го разряда операнда а на вход 18 пятого разряда регистра 15. Одновременно из предыдущего (k-l)-ro разряда устройства на входы первого и второго разряда регистра 15 посту

пает соответственно два разряда результата 5.4 и S.j нэ .входы третьего и четвертого разрядов регистра 15 поступают соответственно два разряда промежуточного результата S г и S ... {в зависимости от нижнего

индекса обозначения определяется вес разряда: верхний индекс означает номер разряда устройства, в котором был вычислен разряд промежуточного

результата), на вход шестого разряда регистра 1 поступает управляющий сигнал. Если управляющий сигнал имеет единичное значение элементов И 9 и 10 и элемента ИЛИ 4, производится инвертирование разряда операнда ai/j, если .управляющий сигнал имеет . значение, инвертирование не .:. происходит. С помощью элемента НЕ 14 элементов И 8, 11, 12 и элемента ИЛИ

3 производится, если это возможно, свертка разряда операнда и разрядов промежуточного результата и S k-z (т.е. замена единиц с весами и oi- единицей с весом ).

После первой свертки производится вторая свертка полученного разряда с весом oi. и разрядов результата S к-э к-4 помощью элемента НЕ 13, элементов И 5-7 и элемента ИЛИ 2.

При этом с выхода элемента ШШ 2 снимается (k-4)-й разряд дополнительного кода числа А.

На следующем (k+l)-M разряде сигналы с выходов соответствующих элементов К-го разряда устройства передаются на соответствующие входы (k+l)-ro разряда устройства.

Указанные преобразования повторяются для каждого разряда конвейерно 3

го преобразователя. С информационного выхода третьего разряда устройства снимается старший знаковый разряд, с информационного выхода четвертого разряда снимается maдший знаковый разряд дополнительного кода, с информационного выхода пятого разряда снимается старшая цифра результата и т.д., с информационного выхода (п+4)-го разряда устройства снимается последний п-й разряд дополнительного кода числа А. Таким образом, дополнительный код п-разрядного (не считая знака) числа формируется за п+5 тактов. При этом на каждом такте может начинаться обработка нового операнда. Положительное число в конвейерном преобразователе прямого кода в дополнительный не подвергается никаким операциям, кроме свертки.

Формула изобретения

Устройство для преобразования кода, содержащее в каждом разряде регистр, первый - седьмой элементы И, элементы ИЛИ, входы первого - пятого разрядов регистра являются соответственно первым - пятым информационными входами данного разряда, вход шестого разряда -регистра является управляющим входом разряда, прямой выход первого разряда регистра соединен с первым входом первого элемента ИЛИ, прямой выход второго разряда регистра соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, выход второго элемента И соединен с информационным входом следующего разряда устройства, инверсный выход второго разряда регистра соединен с первым входом третьего элемента И, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, пря671664

мой выход шестого разряда регистра соединен с управляющим входом следующего разряда устройства и с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, инверсный выход щестого разряда регистра соединен с первым входом шестого элемента И, 10 выход которого соединен с вторым входом третьего элемента ИЛИ, о т- личающееся тем, что, с целью расширения области применения за счет преобразования прямого кода 15 в дополнительный, в него введены элементы НЕ и восьмой элемент И, прямой выход третьего разряда регистра соединен с вторым входом второго элемента ИЛИ, выход которого сое- 20 динен с вторыми входами первого и третьего элементов И и входом первого элемента НЕ, выход которого соединен с вторым входом второго элемента И, прямой выход четвертого 25 разряда регистра соединен с первыми входами четвертого и седьмого элементов И, инверсный выход четвертого разряда регистра соединен с первым входом восьмого элемента И, выход 20 третьего элемента ИПИ соединен с вторым входом четвертого и восьмого элементов И и входом второго элемента НЕ, выход которого соединен с вторым входом седьмого элемента И, выход первого элемента ИЛИ является соответствующим информационным выходом устройства, выходы третьего и восьмого элементов И соединены соответственно с вторым и четвертым ин- .формационными входами следующего разряда, выход седьмого элемента И каждого разряда, кроме предпоследнего, соединен с третьим информационным входом следующего разряда, третий информационный вход последнего разряда объединен с его управляющим входом.

40

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кода | 1990 |

|

SU1725401A2 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для приведения р-кодов фибоначчи к минимальной форме | 1978 |

|

SU779997A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

Изобретение относится к вычис- лительной технике и может быть использовано в вычислительных устройствах с кодами Фибоначчи и кодами золотой пропорции. Целью изобретения является расширение области применения за счет преобразования прямого кода в дополнительный. Устройств9 в каждом разряде содержит первый - третий элементы ИЛИ 2-4, первый - восьмой элементы И 5-12, первый и второй элементы НЕ 13 и 14, регистр 1Ь, первый - пятый информационные входы 16-20 разряда, управляющий вход 21 разряда. 1 ил. (Я

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-15—Публикация

1986-01-29—Подача