Изобретение относится к вычислительной технике, в частности к вычислительным устройствам с кодами Фибоначчи и кодами золотой пропорции, и является усовершенствованием изобретения по авт.св. № 1367166.

Известно устройство для преобразования числа, представленного в коде классической золотой пропорции, содержащее в каждом разряде регистр, первый - восьмой элементы И, первый - третий элементы ИЛИ, первый и второй элементы НЕ, входы первого-пятого разрядов регистра являются соответственно первым-пятым информационными входами данного разряда, вход шестого разряда регистра является управляющим входом разряда, прямой выход первого разряда регистра соединен с первым входом первого элемента ИЛИ, прямой выход второго разряда регистра соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, выход второго элемента И соединен с первым информационным входом следую- щего разряда устройства, инверсный выход второго разряда регистра соединен с первым входом третьего элемента И, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, прямой вы- ход шестого разряда регистра соединен с управляющим входом следующего разряда устройства и с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, инверсный выход шестого разряда регистра соединен с первым входом шестого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, прямой выход третьего разряда регистра соединен с вто- рым входом второго элемента ИЛИ, выход которого соединен с вторыми входами первого и третьего элементов И и входом первого элемента НЕ, выход которого соединен с вторым входом второго элемента И, пря- мой выход четвертого разряда регистра соединен с первыми входами четвертого и седьмого элементов И, инверсный выход четвертого разряда регистра соединен с первым входом восьмого элемента И, выход третьего элемента ИЛИ соединен с вторым входом четвертого и восьмого элементов И и входом второго элемента НЕ, выход которого соединен с вторым входом седьмого элемента И, выход первого элемента ИЛИ является соответствующим информационным выходом устройства, выходы третьего и восьмого элементов И соединены соответственно с вторым и четвертым информационными входами следующего разряда,

выход седьмого элемента И каждого разряда, кроме предпоследнего, соединен с третьим информационным входом следующего разряда, третий информационный вход последнего разряда объединен с его управляющим входом.

Недостатком известного устройства является то, что в нем не осуществляется проверка правильности перевода чисел из прямого кода в дополнительный.

Целью изобретения является расширение функциональных возможностей за счет контроля процесса преобразования кода.

Поставленная цель достигается тем, что устройство для преобразования кода содержит в каждом разряде девятый и десятый элементы И, четвертый элемент ИЛИ, причем выход четвертого элемента ИЛ И каждого разряда устройства является контрольным выходом соответствующего разряда устройства, прямой выход первого разряда регистра каждого разряда устройства соединен с первым входом девятого элемента И того же разряда устройства, выход первого элемента И каждого разряда устройства соединен с вторым входом девятого элемента И того же разряда устройства, выходы девятого и десятого элементов И каждого разряда устройства соединены соответственно с первым и вторым входами четвертого элемента ИЛИ того же разряда устройства, выход четвертого элемента И и прямой выход третьего разряда регистра каждого разряда устройства соединены соответственно с первым и вторым входами десятого элемента И того же разряда устройства.

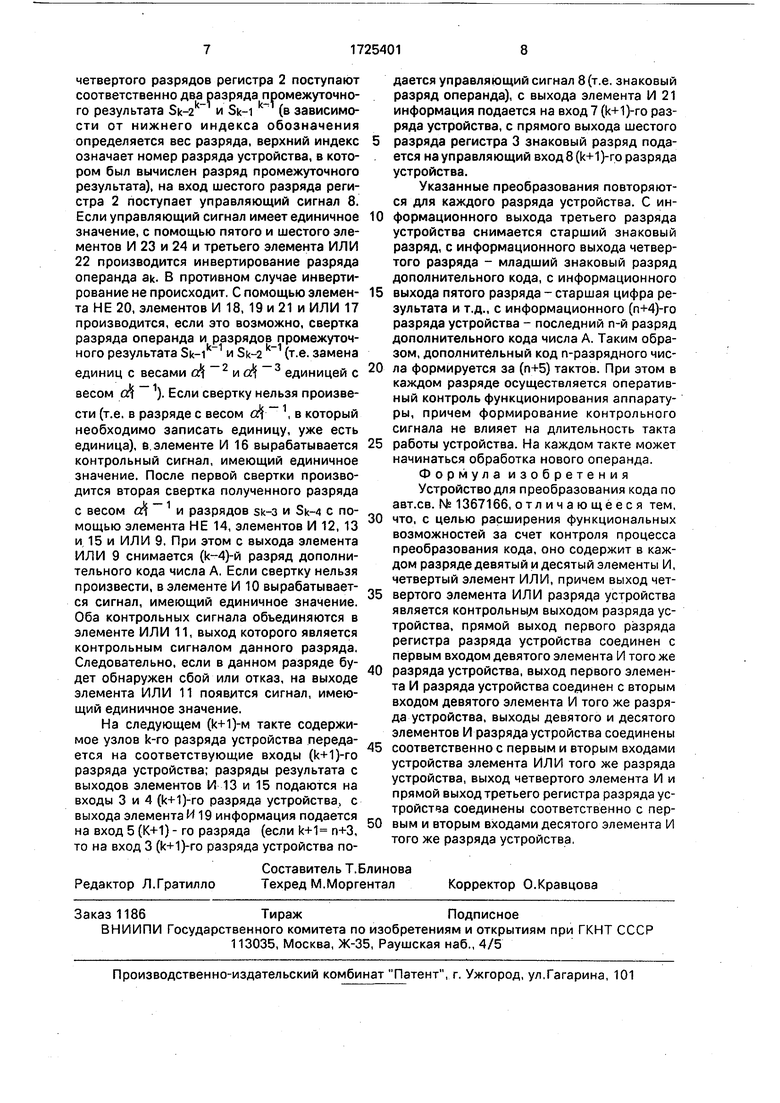

На чертеже представлена функциональная схема устройства для преобразования кода.

Устройство в каждом разряде 1о...1|...1п-и содержит регистр 2, входы первого-пятого разрядов которого являются соответственно первым-пятым информационными входами 3-7 данного разряда, вход шестого разряда регистра 2 является управляющим входом 8 разряда. Прямой выход первого разряда регистра 2 соединен с первыми входами первого элемента ИЛИ 9 и девятого элемента И 10, выход девятого элемента И 10 соединен с первым входом четвертого элемента ИЛИ 11, выход которого является контрольным выходом разряда, выход первого элемента ИЛИ 9 является выходом результата разряда. Прямой выход второго разряда регистра 2 соединен с первыми входами первого и второго элементов И 12 и 13. Выход первого элемента И 12 соединен с вторыми входами первого элемента ИЛИ 9 и девятого элемента И 10. Выход второго элемента И 13 соединен с

первым информационным входом следующего разряда устройства, второй вход второго элемента И 13 соединен с выходом первого элемента НЕ 14. Инверсный выход второго разряда регистра 2 соединен с первым входом третьего элемента И 15, выход которого соединен с вторым информационным входом следующего разряда. Второй вход четвертого элемента ИЛИ 11 соединен с выходом десятого элемента И 16. Второй вход первого элемента И 12 соединен с входом первого элемента НЕ 14, вторым входом третьего элемента И 15 и с выходом второго элемента ИЛИ 17, первый вход которого соединен с входом десятого элемента И 16 и с выходом четвертого элемента И

18,первый вход которого соединен с прямым выходом четвертого разряда регистра 2 и с первым входом седьмого элемента И

19,выход которого соединен, с третьим информационным входом следующего разряда. Второй вход седьмого элемента И 19 соединен с выходом второго элемента НЕ

20,Инверсный выход четвертого разряда регистра 2 соединен с первым входом восьмого элемента И 21, выход которого соединен с четвертым информационным входом следующего разряда. Вторые входы четвертого и восьмого элементов И 18 и 21 соединены с входом второго элемента НЕ 20 и с выходом третьего элемента ИЛ И 22, первый и второй входы которого соединены соответственно с выходами пятого и шестого элементов И 23 и 24. Прямой выход шестого разряда регистра 2 соединен с пятым информационным входом следующего разряда и с первым входом пятого элемента И 23, второй вход которого соединен с инверсным выходом пятого разряда регистра 2, инверсный выход шестого разряда которого соединен с первым входом шестого элемента И 24, второй вход которого соединен с прямым выходом пятого разряда регистра 1.

Устройство выполняет перевод из прямого кода в дополнительный код чисел, представленных либо в золотом 1-коде, либо в 1-коде Фибоначчи, а также контроль процесса преобразования кода. При этом операнды представлены в минимизированной фо.рме, содержащей не более двух единиц подряд, Операция выполняется в неавтономном режиме вычислений, т.е. операнды и результаты поступают поразрядно со старших разрядов. Разряды результата можно использовать по мере их вычислений, не дожидаясь завершения операции перевода. Для получения дополнительного кода все разряды операнда инвертируются (если число отрицательное), и производится последовательная свертка разрядов, начиная со свертки разрядов с весом о и «Г1 в разряды с весом «ь вместо прибавления единицы

в разряд с весом Ч учитывая, что аГ(п О аГг + аТ(п +1) («г(п +1) + -f а(п 2))1 + + Ч производится приписывание единиц к записи кода с последующей сверткой. После приписывания единиц а-(п +1) и а-(п +2) и свертки в разряде свесом ai п должен быть нуль, поэтому к коду приписывается вторая единица

1А Таким образом, формирование дополнительного кода осуществляется посредством выполнения последовательно двух сверток. Для устройства при правильной его работе выполняется следующее контрольное соотношение. При проведении операции свертки, начиная со старших разрядов, никогда не может встретиться ситуация, когда в 1-й разряд, где уже есть единица, должна быть записана еще

одна единица, являющаяся результатом свертки последующих единиц с весами

оГ1иоГ2.

Следовательно, возникновение такой ситуации свидетельствует о сбое или отказе аппаратуры устройства, при этом обнаруживается только сбой или отказ, приводящий к переходу .

Устройство работает следующим образом. Пусть необходимо представить в дополп

нительном коде число ARk Ј ак см к . Устк о

ройство содержит п+5 разрядов с номерами

к 0,1,2п+4. На управляющий вход 8 нулевого разряда устройства подается знаковый разряд операнда ао, на остальные входы этого разряда подаются нули. На вход 7 k-ro разряда устройства (,2п)

подается соответствующий разряд операнда ak. На входы 7(п+1)-го и (п+3)-го разрядов устройства подается О, на входы 5 (п+3)-го и (п+ 4)-го разрядов устройства подается знаковый разряд операнда ао. Знаковый

разряд а„ подается также на вход 5 (п+3)-го разряда устройства.

Пример. Рассмотрим работу k-ro

(,1,2п+4) разряда.

Пусть на k-м такте осуществляется прием k-ro разряда операнда ak на вход 5 пятого разряда регистра 2. Одновременно из предыдущего (k-1)-ro разряда устройства на входы первого и второго разрядов регистра 2 поступают соответственно два разряда результата Sk-4 и Sk-з, на входы третьего и

четвертого разрядов регистра 2 поступают соответственно два разряда промежуточного результата Sk-2k и Sk-1 k (в зависимости от нижнего индекса обозначения определяется вес разряда, верхний индекс означает номер разряда устройства, в котором был вычислен разряд промежуточного результата), на вход шестого разряда регистра 2 поступает управляющий сигнал 8. Если управляющий сигнал имеет единичное значение, с помощью пятого и шестого элементов И 23 и 24 и третьего элемента ИЛИ 22 производится инвертирование разряда операнда ai. В противном случае инвертирование не происходит. С помощью элемента НЕ 20, элементов И 18, 19 и 21 и ИЛИ 17 производится, если это возможно, свертка разряда операнда и разрядов промежуточ- ного результата Sk-ik 1 и Sk-2 (т.е. замена

- з

единиц с весами eft 2 и eft единицей с весом eft ). Если свертку нельзя произвести (т.е. в разряде с весом cft, в который необходимо записать единицу, уже есть единица), в элементе И 16 вырабатывается контрольный сигнал, имеющий единичное значение. После первой свертки производится вторая свертка полученного разряда

с весом eft 1 и разрядов sk-з и Sk-4 с помощью элемента НЕ 14, элементов И 12, 13 и 15 и ИЛИ 9. При этом с выхода элемента ИЛИ 9 снимается (к-4)-й разряд дополнительного кода числа А. Если свертку нельзя произвести, в элементе И 10 вырабатывается сигнал, имеющий единичное значение. Оба контрольных сигнала объединяются в элементе ИЛИ 11, выход которого является контрольным сигналом данного разряда. Следовательно, если в данном разряде будет обнаружен сбой или отказ, на выходе элемента ИЛИ 11 появится сигнал, имеющий единичное значение.

На следующем (к+1)-м такте содержимое узлов k-го разряда устройства передается на соответствующие входы (k+1)-ro разряда устройства; разряды результата с выходов элементов И 13 и 15 подаются на входы 3 и 4 (к-И)-го разряда устройства, с выхода элементам 19 информация подается на вход 5 (К+1) - го разряда (если к+1 п+3, то на вход 3 (к+1)-го разряда устройства поСоставитель Т. Редактор Л.ГратиллоТехред М.Морг

дается управляющий сигнал 8 (т.е. знаковый разряд операнда), с выхода элемента И 21 информация подается на вход 7 (к+1)-го разряда устройства, с прямого выхода шестого

разряда регистра 3 знаковый разряд пода- . ется на управляющий вход8(к+1)-го разряда устройства.

Указанные преобразования повторяются для каждого разряда устройства. С ин0 формационного выхода третьего разряда устройства снимается старший знаковый разряд, с информационного выхода четвертого разряда - младший знаковый разряд дополнительного кода, с информационного

5 выхода пятого разряда - старшая цифра результата и т.д., с информационного (п+4)-го разряда устройства - последний n-й разряд дополнительного кода числа А. Таким образом, дополнительный код n-разрядного чис0 ла формируется за (п+5) тактов. При этом в каждом разряде осуществляется оперативный контроль функционирования аппаратуры, причем формирование контрольного сигнала не влияет на длительность такта работы устройства. На каждом такте может начинаться обработка нового операнда. Формула изобретения Устройство для преобразования кода по авт.св. № 1367166, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля процесса преобразования кода, оно содержит в каждом разряде девятый и десятый элементы И, четвертый элемент ИЛИ, причем выход четвертого элемента ИЛИ разряда устройства является контрольны/и выходом разряда устройства, прямой выход первого разряда регистра разряда устройства соединен с первым входом девятого элемента И того же разряда устройства, выход первого элемента И разряда устройства соединен с вторым входом девятого элемента И того же разряда устройства, выходы девятого и десятого элементов И разряда устройства соединены соответственно с первым и вторым входами устройства элемента ИЛИ того же разряда устройства, выход четвертого элемента И и прямой выход третьего регистра разряда устройства соединены соответственно с первым и вторым входами десятого элемента И того же разряда устройства,

5

0

5

0

5

0

Корректор О.Кравцова

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Устройство для преобразования кода | 1986 |

|

SU1367166A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1397904A1 |

| Устройство для выравнивания порядков чисел | 1982 |

|

SU1030798A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Арифметическое устройство | 1976 |

|

SU664171A1 |

Изобретение касается выполнения арифметических операций в высокопроизводительных многорегистровых вычислительных устройствах с (-кодами Фибоначчи и золотой пропорции и является усовершенствованием устройства для преобразования кода поавт.свид, № 1367166. Целью изобретения является расширение функциональных возможностей за счет контроля процесса преобразования кода. Устройство содержит в каждом разряде регистр 2, элементы ИЛИ 9, 11, 17, 22, элементы И 10,12,13,15,16,18,19.21,23,24 и элементы НЕ 14,20. 1 ил.

| Устройство для преобразования кода | 1986 |

|

SU1367166A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-07—Публикация

1990-04-16—Подача