Изобретение относится к цифровым системам передачи информации и может быть использовано для обнаружения ошибок цифровой информации, битовый состав кадровой синхронизации которой априорно известен.

Цель изобретения - повышение быстродействия устройства за счет оперативного обнаружения ошибок.

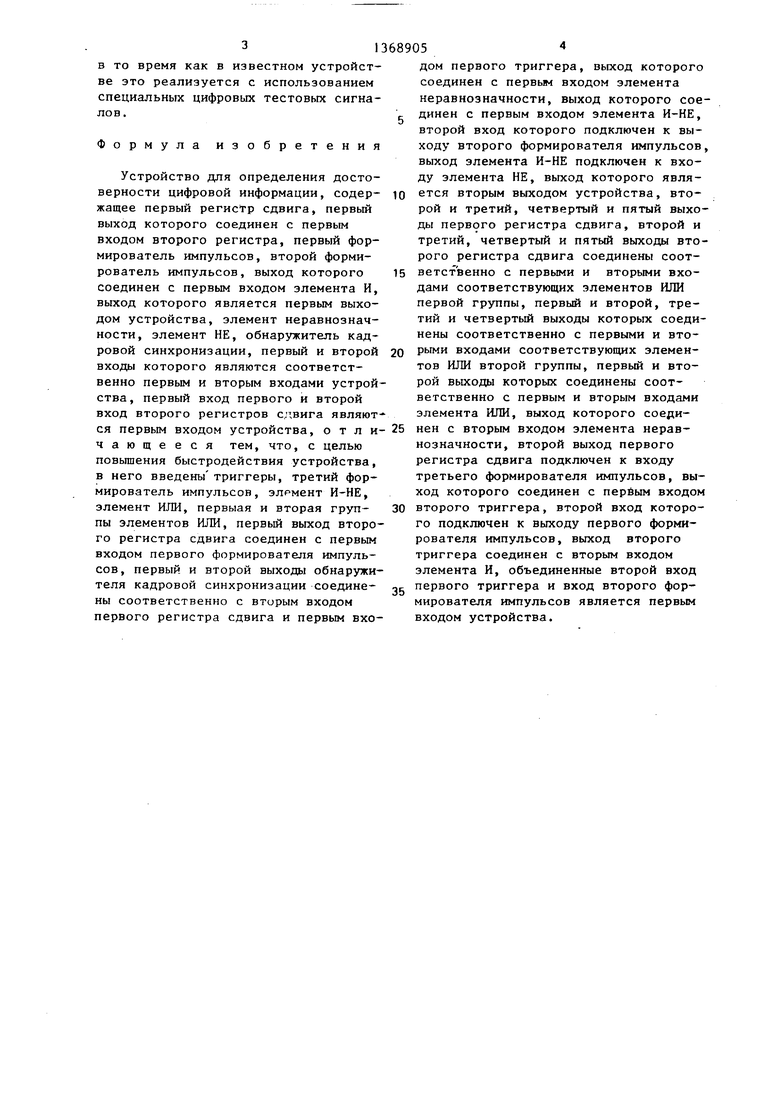

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит обнаружитель 1 кадровой синхронизации, первый 2 и второй 3 регистры сдвига первый 4, второй 5 и третий 6 формирователи импульсов, первый 7 и второй 8 триггеры, первую 9 и вторую LO группы элементов ИЛИ, элемент ИЛИ 1 элемент 12 неравнозначности, элемент И 13, элемент И-НЕ 14 и элемент НЕ 15

Устройство работает следующим образом.

Регенерированный последовательный цифровой поток (сигнал А на фиг.2) , содержащий данные и кадрову синхронизацию, поступает на обнаружитель 1 кадровой синхронизации, на первый вход этого обнаружителя поступают сигналы битовой синхронизации (сигнал Б на фиг. 2). Под воздействием шумов канала имеют место ошибки (ложные вставки и ложные выпадения битов) в цифровом потоке как в составе данных, так и в составе кадровой синхронизации (на фиг. 2 показаны ошибки в составе кадровой синхронизации).

Сигнал Г появляется на выходе обнаружителя кадровой синхронизации (допускающего, например, до двух ошибочных битов в кадровой синхронизации вида 100110101111000) в интервале времени, соответствующем последнему биту в кадровой синхронизации. Сигнал Г поступают на вход сдвиг вправр последовательного 8-разрядного регистра 2 сдвига, выход последнего разряда которого соединен с входом DR второго регистра 3. На вход С обоих регистров сдвига (КС) 2 и 3 поступает сигнал битового ритма. Соответствующие выходы обоих НС.соедине- ны с входами четырех 2-входовых элементов ИЛИ 9, четыре выхода которых соединены с входами двух 2-входовых элементов Ш1И 10, два выхода которых

соединены мента ИЛИ разуется

с входами 2-входового эле- 11, на выходе которой об- копия кадровой синхронизации (сигнал Ж на фиг. 2).

Задержанный на 15 битов выходной последовательный поток с обнаружителя 1 кадровой синхронизации (сигнал В на фиг. 2) поступает на D-триггер 7, на выходе которого осуществляется фазирование кадровой синхронизации потока и копии кадровой синхронизации с точностью до бита (сигнал Е на фиг. 2). На выходе элемента 12 неравнозначности появляются сигналы обнаруженных ошибок в кадровой синхронизации потока (сигнал Л нафиг.2).

RS-триггер 8 формирует сигнал стробирования, длительность которого равняется длительности кадровой синхронизации (по входу R этот триггер запускается с помощью формирователя 6, работающего по возрастающему фронту сигнала с выхода QО регистра 2; по входу S этот триггер запускается формирователь 4, работающему по ниспадающему фронту сигнала с выхода Q 6 регистра З). Выходной сигнал с триггера В поступает нЗ один из вхо- дов 2-входового элемента И 13 и 3- входового элемента И-НЕ 14,. на входы этих элементов поступают выходные сигналы (м на фиг. 2) формирователя 5, который срабатывает от ниспадаю- щих фронтов битового ритма. На пер- вый вход элемента 14 поступают обнаруженные ошибочные биты в кадровой синхрониз ации.

Выходные сигналы элемента 13 (сигналы Н на фиг. 2) являются синхросигналами, которые поступают на счетчик показателя степени, а выходные сигналы элемента 14 через элемент НЕ 15 (сигналы П на фиг. 2} - на счетчик количества ошибок. После

5

0

подсчета выбран}1ого показателя степени, например 10 отсчетов, выходной сигнал счетчика показателя степени осуществляет запись содержимого чика количества ошибок в память и . далее сбрасывает в нуль содержимое счетчика количества ошибок; таким образом, обеспечивается измерение достоверности цифрового потока, принимаемого в реальном времени.

Предлагаемое устройство позволяет обеспечить измерение достоверности в режиме приема реальных цифровых потоков, содержащих научные данные,

31

в то время как в известном устройстве это реализуется с использованием специальных цифровых тестовых сигналов .

Формула изобретения

Устройство для определения достоверности цифровой информации, содержащее первый регистр сдвига, первый выход которого соединен с первым входом второго регистра, первый формирователь импульсов, второй формирователь импульсов, выход которого соединен с первым входом элемента И, выход которого является первым выходом устройства, элемент неравнозначности, элемент НЕ, обнаружитель кадровой синхронизации, первый и второй входы которого являются соответственно первым и вторым входами устрой ства, первый вход первого и второй вход второго регистров с;твига являются первым входом устройства, о т л и чающееся тем, что, с целью повьшения быстродействия устройства, в него введены триггеры, третий формирователь импульсов, элрмент И-НЕ, элемент ИЛИ, первыая и вторая группы элементов ИЛИ, первый выход второ го регистра сдвига соединен с первым входом первого формирователя импульсов, первый и второй выходы обнаружителя кадровой синхронизации соединены соответственно с вторым входом первого регистра сдвига и первым вхо68905

дом первого триггера, выход которого соединен с первым входом элемента неравнозначности, выход которого сое- V динен с первым входом элемента И-НЕ,

О

второй вход которого подключен к выходу второго формирователя импульсов, выход элемента И-НЕ подключен к входу элемента НЕ, выход которого явля10 ется вторым выходом устройства, второй и третий, четвертый и пятый выходы первого регистра сдвига, второй и третий, четвертый и пятый выходы второго регистра сдвига соединены соот15 ветственно с первыми и вторыми входами соответствующих элементов ИЛИ первой группы, первый и второй, третий и четвертый выходы которых соединены соответственно с первыми и вто20 рыми входами соответствующих элементов ИЛИ второй группы, первый и второй выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соеди- 25 нен с вторым входом элемента неравнозначности, второй выход первого регистра сдвига подключен к входу третьего формирователя импульсов, выход которого соединен с пербын входом

30 второго триггера, второй вход которого подключен к выходу первого формирователя импульсов, выход второго триггера соединен с вторым входом элемента И, объединенные второй вход

og первого триггера и вход второго формирователя импульсов является первым входом устройства.

Оши5ки

100110101/11000 ппннмр1 00 J 1 О 1 О J

0П , Г-1 П П ГП , , : П ,

(|)1п;шллпллл1и1пя1шл1и1плл

П

-УЬ

-УЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения достоверности цифровой информации | 1989 |

|

SU1674211A2 |

| Устройство для выделения маркера кадровой синхронизации | 1987 |

|

SU1518903A2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Обнаружитель битовой ошибки в последовательном цифровом тестовом потоке | 1990 |

|

SU1758657A2 |

Изобретение относится к цифровым системам передачи информации и может быть использовано для обнаружения ошибок цифровой информации, битоад/./ вый состав кадровой синхронизации которой априорно известен. Цель изобретения - повышение быстродействия устройства за счет оперативного обнаружения ошибок. Устройство содержит обнаружитель 1 кадровой синхронизации, регистры 2, 3 сдвига, формирователи 4-6 импульсов, триггеры 7,8, элементы ИЛИ 9, 10, элемент ИЛИ II, элемент 12 неравнозначности, элемент И 13, элемент И-НЕ 14, элемент НЕ 15. Работа устройства основана на срав- неии элементом 12 сигнала кадровой синхронизации и его копии, поступающей с выходов регистров сдвига. Элемент 12 фиксирует ошибки синхронизации, которые через элемент НЕ 15 поступают на выход устройства. 2 ил. W ,5К (Л OuiuSiui

I I I I I I I I I I I I I I I I I I I I I и I I I I I I и

Данные

Данные ®

ruj-njTj

I I I

-«-«I I I I I и I I и I I I I

Фиг. 2

| IEEE | |||

| TrEuis on com | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Обнаружитель битовой ошибки в последовательном цифровом тестовом потоке | 1985 |

|

SU1322355A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-01-23—Публикация

1986-07-14—Подача