сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для обращения матриц | 1988 |

|

SU1647591A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Устройство для определения динамической нестабильности переходного сопротивления контакта | 1987 |

|

SU1418661A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

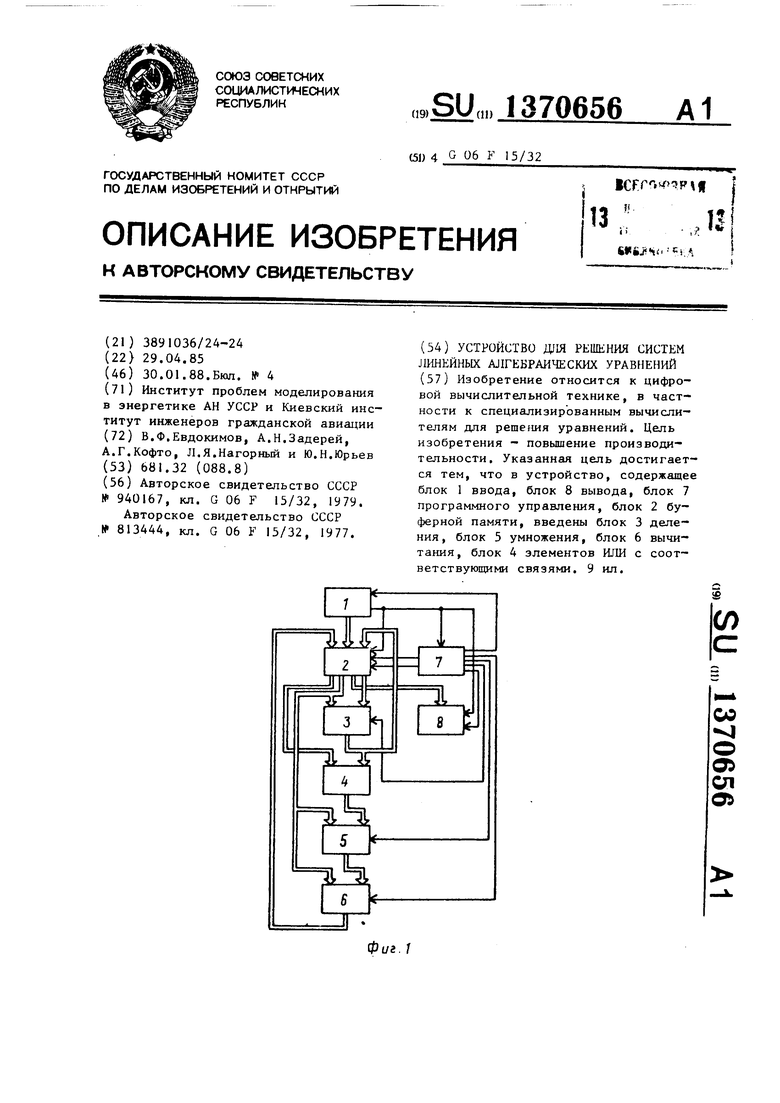

Изобретение относится к цифровой вычислительной технике, в частности к специализированным вычислителям для уравнений. Цель изобретения - повышение производительности. Указанная цель достигается тем, что в устройство, содержащее блок 1 ввода, блок 8 вывода, блок 7 программного управления, блок 2 буферной памяти, введены блок 3 деления , блок 5 умножения, блок 6 вычитания, блок 4 элементов ИЛИ с соответствующими связями. 9 ил.

со

о

О)

ел

Од

Фиг. 1

Изобретение относится к цифровой вычислительной технике, в частности к специализированным вычислителям для решения уравнений.

Цель изобретения - увеличение производительности.

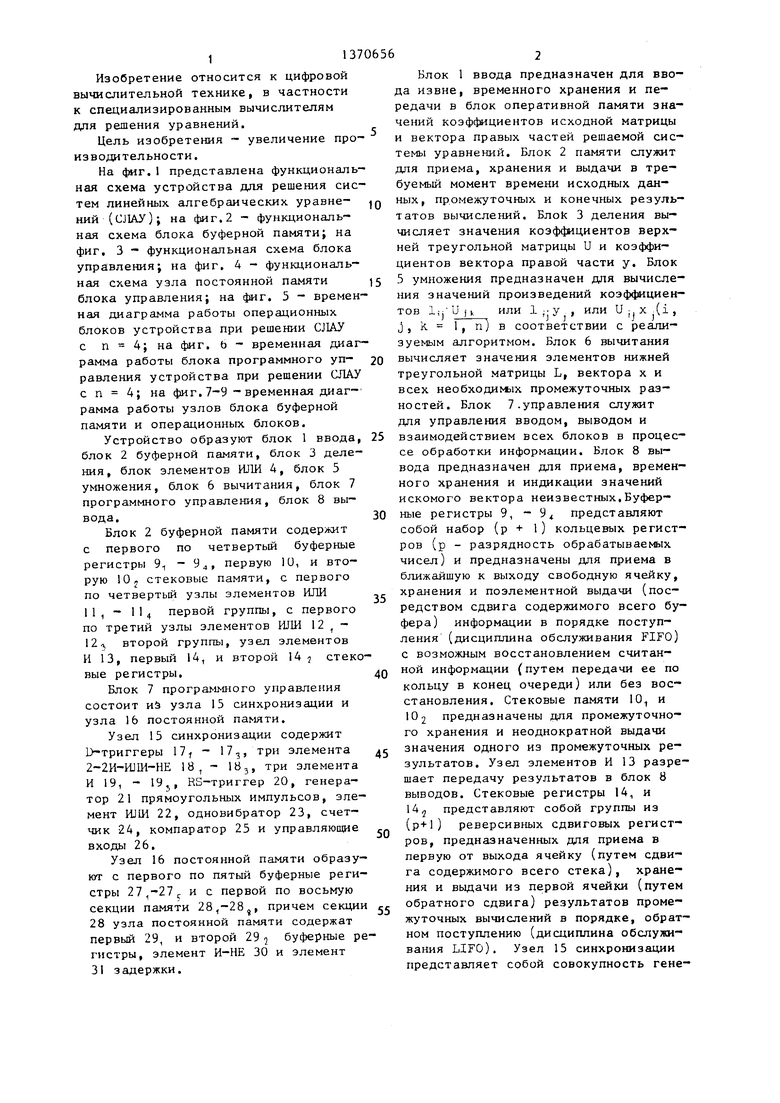

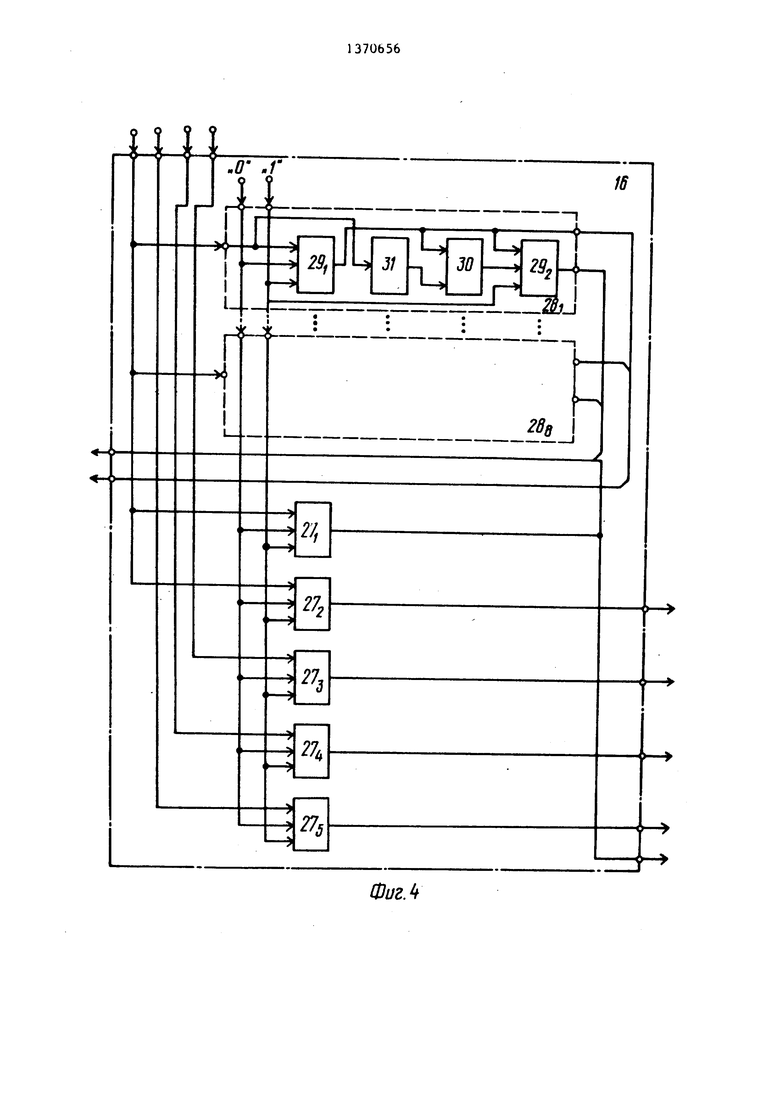

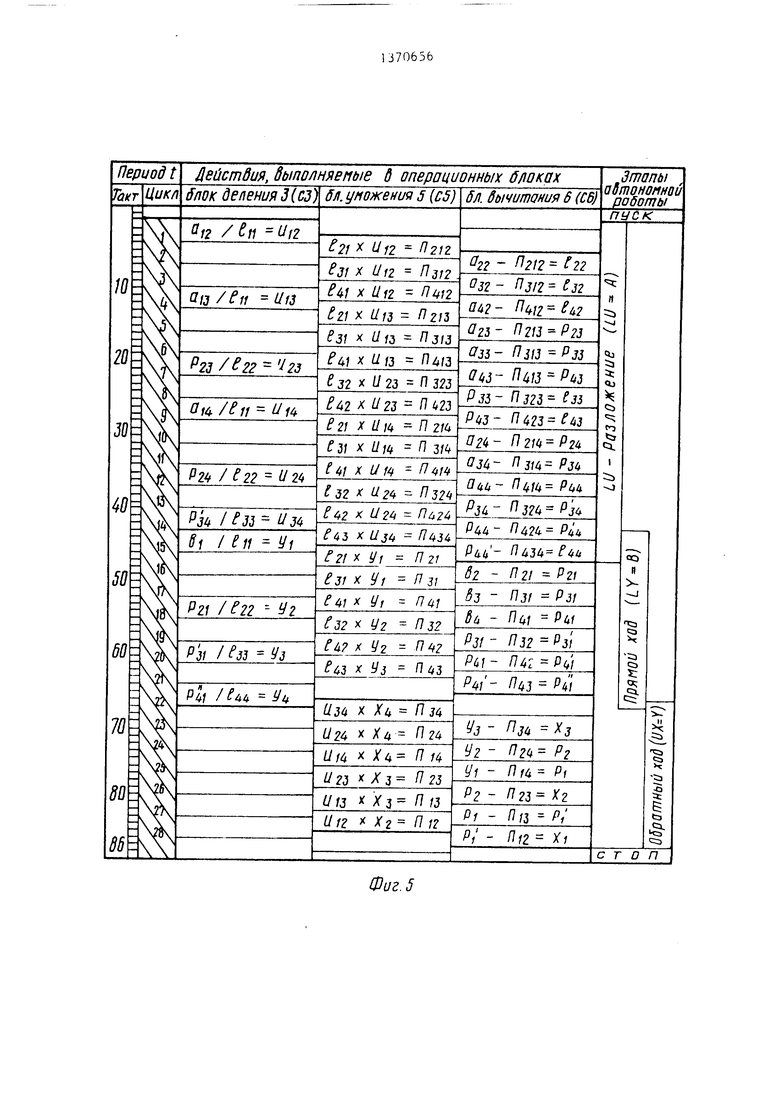

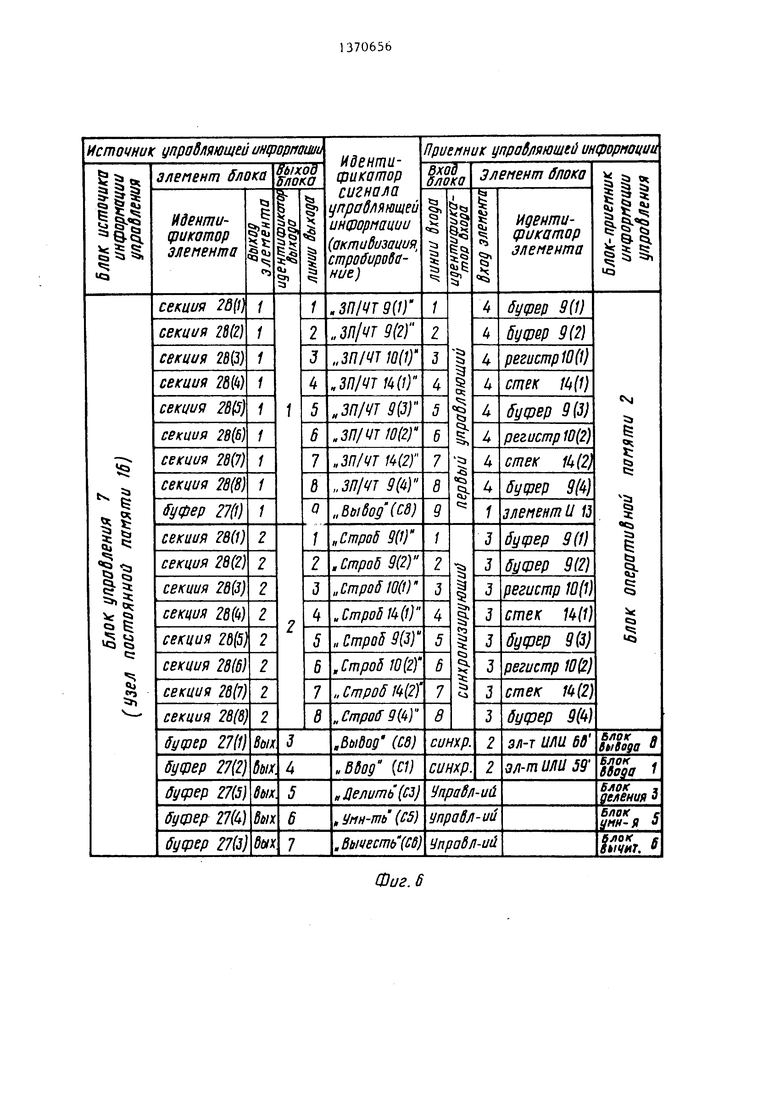

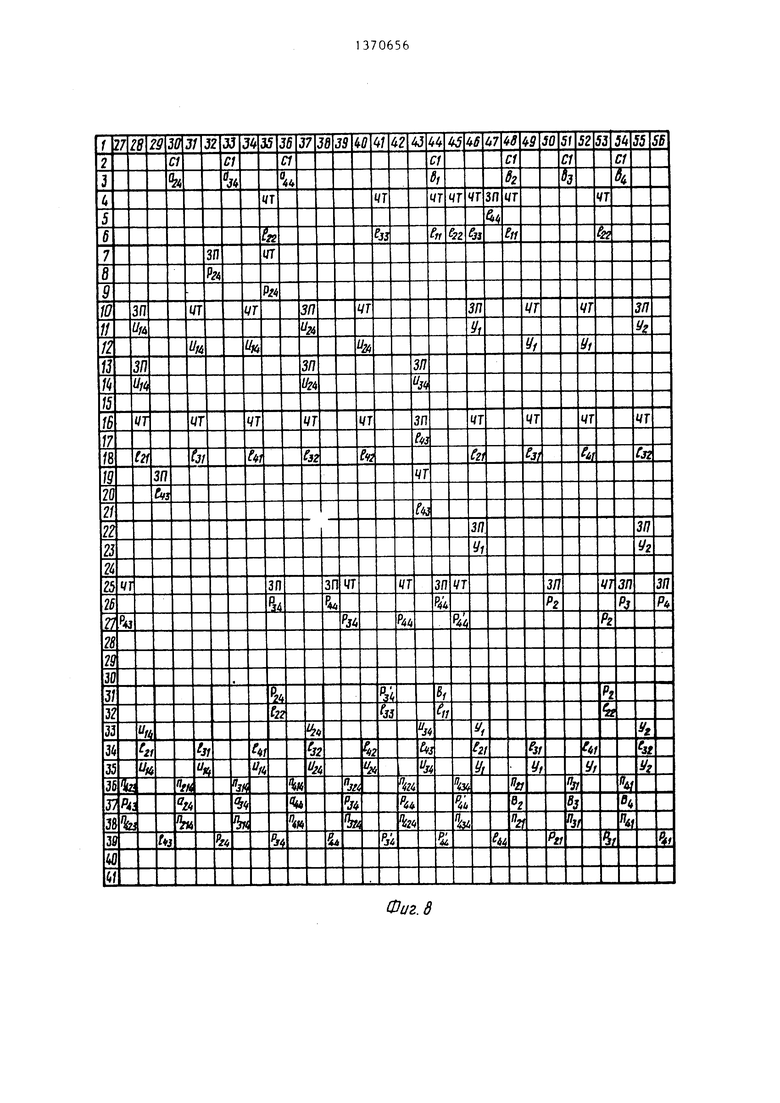

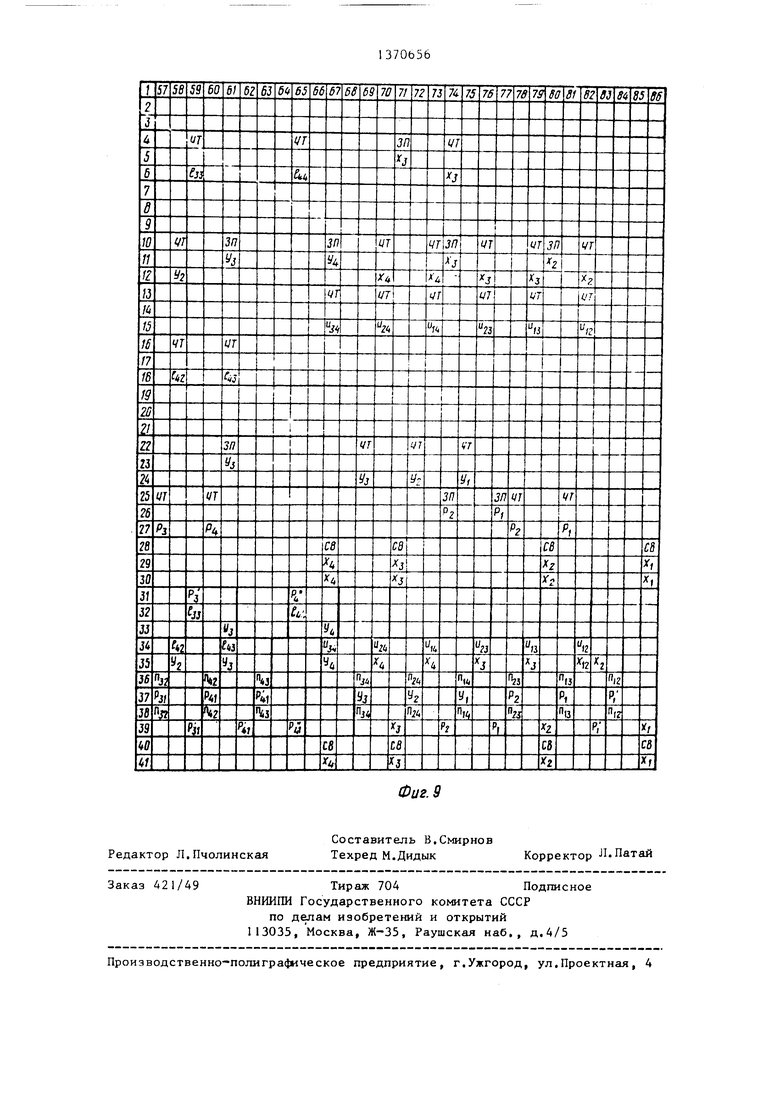

На фиг.1 представлена функциональная схема устройства для решения систем линейных алгебраических уравне- кий (СЛАУ); на фиг.2 - функциональная схема блока буферной памяти; на фиг, 3 функциональная схема блока упра;вления; на фиг. 4 - функциональная схема узла постоянной памяти блока управления; на фиг. 5 - временная диаграмма работы операционных блоков устройства при решении СЛАУ с п 4; на фиг. Ь - временная диаграмма работы блока программного уп- равления устройства при решении СЛАУ с п 4; на фиг. 7-9 -временная диаг-- рамма работы узлов блока буферной памяти и операционных блоков.

Устройство образуют блок 1 ввода, блок 2 буферной памяти, блок 3 деления, блок элементов ШШ 4, блок 5 умножения, блок 6 вычитания, блок 7 программного управления, блок 8 вывода.

Блок 2 буферной памяти содержит с первого по четвертый буферные регистры 9, - 94, первую 10, и вторую 102 стековые памяти, с первого по четвертый узлы элементов ИЛИ

11, - 114 первой группы, с первого по третий узлы элементов ШШ 12 ,- 12- второй группы, узел элементов И 13, первый 14, и второй 14 стековые регистры.

Блок 7 nporpa u-ffloro управления состоит иЗ узла 15 синхронизации и узла 16 постоянной памяти.

Узел 15 синхронизации содержит 1 триггеры 17 - 17з, три элемента

2-2И-И Ш-НЕ

18, 1В3, три элемента

И 19, - 19j, RS-триггер 20, генератор 21 прямоугольных импульсов, элемент ИЛИ 22, одновибратор 23, счетчик 24, компаратор 25 и управляющие входы 26.

Узел 16 постоянной памяти образуют с первого по пятый буферные регистры и с первой по восьмую

50

го хранения и неоднократной выдачи значения одного из промежуточных результатов. Узел элементов И 13 разрешает передачу результатов в блок 8 выводов. Стековые регистры 14, и 14,2 представляют собой группы из (р+1) реверсивных сдвиговых регистров, предназначенных для приема в первую от выхода ячейку (путем сдвига содержимого всего стека), хранения и выдачи из первой ячейки (путем

секции памяти 28,-28,, причем секции ее обратного сдвига) результатов проме28 узла постоянной памяти содержат первый 29, и второй 29 буферные регистры, элемент И-НЕ 30 и элемент 31 задержки.

жуточных вычислений в порядке, обратном поступлению (дисциплина обслуживания LIFO). Узел 15 синхронизации представляет собой совокупность генеБлок 1 ввода предназначен для ввода извне, временного хранения и передачи в блок оперативной памяти значений коэфе ициентов исходной матрицы и вектора правых частей решаемой системы уравнений. Блок 2 памяти служит для приема, хранения и выдачи в требуемый момент времени исходных данных, промежуточных и конечных результатов вычислений. Блок 3 деления вычисляет значения коэффициентов верхней треугольной матрицы U и коэффициентов вектора правой части у. Блок 5 умножения предназначен для вычисления значений произведений коэффициентов lij Ujk или 1 ;j у , или Uj хД1, j, К 1, п) в соответствии с реализуемым алгоритмом. Блок 6 вычитания вычисляет значения элементов нижней треугольной матрицы L, вектора х и всех необходимз1х промежуточных разностей. Блок 7.управления служит для управления вводом, выводом и взаимодействием всех блоков в процессе обработки информации. Блок 8 вывода предназначен для приема, временного хранения и индикации значений искомого вектора неизвестных.Буферные регистры 9, - 9 представляют собой набор (р + 1) кольцевых регистров (р - разрядность обрабатываемых чисел) и предназначены для приема в ближайшую к выходу свободную ячейку, хранения и поэлементной выдачи (посредством сдвига содержимого всего буфера) информации в порядке поступления (дисциплина обслуживания FIFO) с возможным восстановлением считанной информации (путем передачи ее по кольцу в конец очереди) или без восстановления. Стековые памяти 10- и

10

2 предназначены для промежуточно

го хранения и неоднократной выдачи значения одного из промежуточных результатов. Узел элементов И 13 разрешает передачу результатов в блок 8 выводов. Стековые регистры 14, и 14,2 представляют собой группы из (р+1) реверсивных сдвиговых регистров, предназначенных для приема в первую от выхода ячейку (путем сдвига содержимого всего стека), хранения и выдачи из первой ячейки (путем

обратного сдвига) результатов промежуточных вычислений в порядке, обратном поступлению (дисциплина обслуживания LIFO). Узел 15 синхронизации представляет собой совокупность генератора тактовых сигналов, схемы старт-стопного управления генератором и схемы распределения синхронизирующих сигналов на основе кольцевого сдвигового регистра и предназначен для выборки тактовых серий, обеспечивающих взаимодействие во времени основных блоков устройства.Узел 16 постоянной памяти представляет собой набор запоминающих модулей,содержащий информацию о необходимости функционирования любого блока в течение любого такта работы всего устройства, а также информацию о режиме работы (Запись или Чтение) блока 2. D-триггеры 17 - 17 являются запоминающими элементами кольцевого сдвигового регистра. Схемы 2- 2И-ИЛИ-НЕ 18, - 18j предназначены для обеспечения необходимых логических функций на входах D-триггеров кольцевого сдвигового регистра. Элементы И 19, - 19 разрешают выдачу тактовых импульсов на синхронизирую- 1цие входы буферов узла постоянной памяти с целью считывания информации об инициации (или запрете) функционирования соответственно блока 3 деления, блока 5 умножения и блока 6 вычитания. Одновибратор 23 предназначен для формирования задержанного сигнала Сброс для счетчика 24 и для узла 16 постоянной памяти, сигнала начальной установки бегающей единицы в D-триггере 17 и О в триггерах 177 и 17з и сигнала Пуск для старт-стопного элемента (КЗ-триггера 2U), управляющего работой генератора 21 прямоугольных импульсов. Счетчик 24 предназначен для фиксации порядкового номера каждого тактового импульса. Компаратор 25 служит для определения момента завершения функционирования устройства (выработка сигнала Стоп). В секциях 28, - 28 g хранится информация о необходимости функционирования и режиме работы (Запись - Чтение) элементов блока 2 памяти буферных регистров 9

вычитания, блока 5 умножения и блока 3 деления, буферный регистр 29, - дл хранения информации об инициации (или запрете) в текущем такте работы соответствующего элемента блока буферной памяти 2, буферный регистр

Ь

10

15

20

29,- для хранения информации о режиме (Запись - Чтение) работы соответствующего элемента блока 2 буферной памяти в текущем такте работы Элемент 31 задержки служит для согласования во времени работы буферных регистров 29, и 29,. Элемент И-НЕ 30 вырабатывает сигнал Чтение, поступающий в буферный регистр 29,

Работа устройства может быть пояснена на примере решения системы четырех (п 4) линейных алгебраических уравнений с четырьмя неизвестными вида Лд в с использованием метода прямого треугольного разложения. Этот метод состоит в последовательности преобрании матрицы коэффициентов А размерности (п X п) в виде произведения нижней L и верхней U треугольных матриц (А LU), решении системы уравнений L у в (прямой ход) и решении системы уравнений U ,, у (обратный ход).

Работу устройства можно описать с помощью представленной на фиг.5 временной диаграмг., поясняющей парал- лельно-Конвейерное функционирование блоков деления 3, умножения 5 и вычитания 6. Работа всего устройства синхронизирована тактовой последовательностью Ф с периодом i , работа операционных блоков синхронизирована тремя тактовыми последовательностя-

30

40

ми Ф

А

.

И

(соответственно

для блоков деления, умножения и вычи-

1

45

т г памяти 10,, стекового регистра

буферного регистра 9j, стековой

ти 10J, стекового регистра 14 и буферного регистра 9 4. Буферные регистры 27, - 27 предназначены для хранения информации об инициации (или запрете) в текущем такте работы соответственно блока 8 вывода, блока 6

тания с периодом w. - 1.4, 3 t причем эти последовательности сдвинуты друг относительно друга на время 2 С. За время 3 в каждом операционном блоке выполняются следующие действия: прием операндов, собстсоответственно Q венно обработка, выдача результата.

и 9,, стековой Выдача результата из одного опера- 14,, ционного блока совпадает с приемом результата в следующем по конвейеру операционном блоке, что определяет смещение на время 2 С. Работа всего

1 памя-

55

устройства разделена на циклы длительностью 7 С, каждый из которых составляют последовательно выполняеьые действия в блоке 3 деления, блоке 5

706561

вычитания, блока 5 умножения и блока 3 деления, буферный регистр 29, - для хранения информации об инициации (или запрете) в текущем такте работы соответствующего элемента блока буферной памяти 2, буферный регистр

Ь

29,- для хранения информации о режиме (Запись - Чтение) работы соответствующего элемента блока 2 буферной памяти в текущем такте работы. Элемент 31 задержки служит для согласования во времени работы буферных регистров 29, и 29,. Элемент И-НЕ 30 вырабатывает сигнал Чтение, поступающий в буферный регистр 29,

Работа устройства может быть пояснена на примере решения системы четырех (п 4) линейных алгебраических уравнений с четырьмя неизвестными вида Лд в с использованием метода прямого треугольного разложения. Этот метод состоит в последовательности преобрании матрицы коэффициентов А размерности (п X п) в виде произведения нижней L и верхней U треугольных матриц (А LU), решении системы уравнений L у в (прямой ход) и решении системы уравнений U ,, у (обратный ход).

Работу устройства можно описать с помощью представленной на фиг.5 временной диаграмг., поясняющей парал- лельно-Конвейерное функционирование блоков деления 3, умножения 5 и вычитания 6. Работа всего устройства синхронизирована тактовой последовательностью Ф с периодом i , работа операционных блоков синхронизирована тремя тактовыми последовательностя-

ми Ф

А

.

И

(соответственно

для блоков деления, умножения и вычи-

1

тания с периодом w. - 1.4, 3 t причем эти последовательности сдвинуты друг относительно друга на время 2 С. За время 3 в каждом операционном блоке выполняются следующие действия: прием операндов, собст45

Выдача результата из одного опера- ционного блока совпадает с приемом результата в следующем по конвейеру операционном блоке, что определяет смещение на время 2 С. Работа всего

5

устройства разделена на циклы длительностью 7 С, каждый из которых составляют последовательно выполняеьые действия в блоке 3 деления, блоке 5

5-1

умножения и блоке 6 вычитания, т.е. на протяжении всего операционного конвейера. Длительность серии определяется временем выполнения операции в блоке 3 деления, так как операция деления является самой длительной.

Автоматическая работа устройства начинается при поступлении сигнала Пуск с второго выхода блока 1 ввода на вход блока 7 управления, на второй управляющий вход блока 2 оперативной памяти и на управляющий вход блока b вывода. При этом в начальном (нулевом) такте по сигналу Пуск происходит следующее:

-буферный регистр блока 1 ввода переводится в режим Чтение ;

-буферный регистр блока вывода 8 переводится в режим Запись ;

-сигнал Пуск с второго управляющего входа блока 2 буферной памяти поступает как сигнал Сброс н первые входы всех буферных регистро 9, - 9 (и стековых регистров 14, и 14 7) и устанавливает в их указателя свободных ячеек коды 00-01, подготавливая для приема информации первые ячейки этих узлов

-задерживаясь на время переходных процессов в других блоках, сигнал Пуск с выхода одновибратора 23 узла 15 синхронизации поступает на В-вход RS-триггера 20, который потенциалом 1 со своего прямого в хода запускает генератор 21 прямоугольных импульсов, на установочный вход счетчика 24, сбрасывая его в

О, на сдвиговьй кольцевой регистр узла синхронизации, подготавливая установку, в нем кода 100 (т.е.

D-трнггер 17i - в состоянии 1

17,17.

- в состоянии о

буется функционирование блока 3 деления в данном такте) или об отсутствии сигнала

О

если не требует-

т1 иV,., У / ПОД Г О

тавливая к работе элемент И 19,, с

которого снимается серия P(c эле- 45 выполнение операции деления в дан- ментов И 19, и 193 снимаются соответ- ° такте). В данном случае в пер- ственно серии Ф,), на второй вход элемента ИЛИ 22, с выхода которого в качестве сигнала Строб 7

считывается код U, на третьи входы всех секций 28, - 28 и буферных регистров 27, и 27J поступает сигнал, стробирующий считывание информации

поступает на синхронизирующие входы D-триггеров 17 - 17 кольцевого регистра, устанавливая в нем код 100 (бегающая единица в начале кольца).

Далее первьш импульс с выхода генератора 21 прямоугольных импульсов выполняет следующее:

- поступая на первый вход элемента И 19.,, формирует и выдает перво-

ном такте; ном такте работы устройства блок 3 деления не должен быть активизирован, так как он еще не принял операнды. Поэтому из буферного регистра 27 j О,

55

из буферных регистров сигналов активизации (буферных регистров 29., всех секций, буферных регистров 27., и 272) и буферных регистров режимов (буферные регистры 29 всех секций

5

го импульса серии ф на первый выход узла 15 синхронизации;

-поступая на четвертый вход элементов 2-2И-ИЛИ-НЕ 18,-18, подготавливается сдвиг вправо бегающей единицы в кольцевом регистре;

-поступая на счетный вход счетчика 24, добавляет единицу к содержимому счетчика;

-поступает через четвертый выход узла 15 синхронизации и четвертый вход узла 16 постоянной памяти на третьи входы секций 28, - 28, и на третьи входы буферных регистров 27 и 27 как стробируюш 1й сигнал счи

тывания управляющей информации из узла постоянной памяти 16 блока 7 управления.

Проходя через элемент ИЛИ 22,этот

импульс

- поступая на синхронизирующие входы D-триггеров 17, и 17,, производит сдвиг вправо бегающей единицы в кольцевом регистре, с выхода эле-

мента И 19j снимается серия fj;

- поступая на управляющий вход компаратора 25, производит сравнение содержимого счетчика 24 с состоянием блока клавишного набора 26, на котором занесена информация о количестве тактов, необходимых для решения данной задачи.

В первом такте работы устройства в узел 16 постоянной памяти блока 7 управления поступают стробирующие сигналы. На первый вход узла постоянной памяти поступает импульс серии Ф , по которому считывается информация о сигналах Строб 3 с выхода бу-

ферного регистра 27, (1, если тре-

буется функционирование блока 3 деления в данном такте) или об отсутствии сигнала

О

если не требует-

выполнение операции деления в дан- ° такте). В данном случае в пер-

считывается код U, на третьи входы всех секций 28, - 28 и буферных регистров 27, и 27J поступает сигнал, стробирующий считывание информации

ном такте; ном такте работы устройства блок 3 деления не должен быть активизирован, так как он еще не принял операнды. Поэтому из буферного регистра 27 j О,

55

из буферных регистров сигналов активизации (буферных регистров 29., всех секций, буферных регистров 27., и 272) и буферных регистров режимов (буферные регистры 29 всех секций

28, - 28j). Так как в первом такте рабо ы устройства необходима активизация только блока 1 ввода и буфер™ ного регистра 9, блока 2 (для пере- дачи коэффициента „ 1„ из блока 1 ввода Б буферный регистр 9,), код | считывается из буфера 27 (сигнал Строб 1 для блока 1 ввода в режиме Чтение на синхронизирую- щий вход блока 1 ввода с четвертого вьтода блока 7 управления) и из буферного регистра 29, секции 28 (сигнал Строб 9.1), который через второй выход секции 28,, соответст- вующую (первую) линию второго выхода узла 16 постоянной памяти и второго выхода блока 7 управления и синхронизирующий вход 2 блока поступает на третий (синхронизирующий) вход буферного регистра 9. Кроме того, сигнал с выхода буферного регистра 29, , стробирует работу буферного регистра 29;. Задержанный на время переходных процессов в буфер- ном регистре 29, сигнал Строб 28.1 с выхода линии 31 задержки разрешает установку кода О (режим Чтение для буферного регистра 297) на первом входе буферного регистра 29 с выхода элемента И-НЕ 30 секции 28, Так как буферный регистр 9, блока 2 должен работать в режиме Запись для приема коэффициента а, , с выхода буферного регистра 29j считывает- ся код 1 через первый выход секции 28 и соответствующую (первую) линию первого выхода узла 16 постоянной памяти, первого выхода блока 7 управления, первого управляющего входа блока 2 на четвертый вход (вход режима) буферного регистра 9,. При этом информация (коэффициента d } с первого выхода блока 1 ввода через третий вход блока 2 по второму входу блока 1Ц поступает на пятые входы буферных регистров 9,, 9j, 9 и сте- ковой памяти 10,, второй вход узла П., второй вход узла 12 и далее на первый вход узла II7. Но из всего множества входов открытым является только пятый вход буферного регистра, в первую ячейку которого записывается коэффициент а 1, На этом все действия первого такта работы пред- лагаемого устройства завершаются. Назначение всех выходов блока 7 управления приведены на фиг.6. Диаграмма работы устройства с указанием состояний входов и выходов основных блоков приведены на фиг,7-9.

На втором такте работы по сигналу Строб 1, поступающему с четвертого выхода блока 7 управления на синхронизирующий вход блока 1 ввода, происходит, выдача коэффициента а, с первого выхода блока 1 ввода через третий вход блока 2 буферной памяти, узлы 1Ц и 11,, узел 12J и третий выход блока 2 буферной памяти на первый вход блока 3 деления. Одновременно по сигналу Чтение 9.1, поступающему с первого выхода через первый управляющий вход блока 2 буферной памяти на четвертый вход буферного регистра 9,, и по сигналу Строб 9.1, поступающему с второго выхода блока 7 управления через синхронизирующий вход блока 2 на третий вход буферного регистра 9,, происходит выдача элемента 1 , (с рециркуляцией) с выхода буферного регистра 9 через первый информационный выход блока 2 на второй информационный вход блока 3 деления. По сигналу Делитель,поступающему с пятого выхода блока 7 управления на управляющий вход блока 3 деления, происходит прием делимого делителя 1,, на регистры операндов блока 3 деления.

I

На третьем шаге по сигналу, поступающему с четвертого выхода блока 7 управления на синхронизирующий вход блока 1 ввода, происходит выдача коэффициента а J, 1 , с первого выхода блока I ввода через третий вход блока 2 и узел I13 на первый вход стековой памяти 10,, одновременно по сигналу Запись, поступающему с первого выхода блока 7 управления через первый управляющий вход блока 2 на второй вход стековой памяти 10, , и стробирующему сигналу, поступающему с второго выхода блока 7 управления через синхронизирующий вход блока 2 на третий вход стековой памяти lOj, происходит занесение коэффициента lji UJ1 в стековую память 10,.Одновременно в блоке деления происходит вычисление элемента верхней треугольной матрицы и ,, по формуле

и

и

VI// .

На четвертом шаге с первого выхода блока 7 управления через первый

управляющий вход блока буферной памяти поступает код, один разряд которого, поступая на четвертый вход буферного регистра 9,, , определяет для него режим Запись, следующий разряд, поступая на второй вход стековой памяти 10,, определяет для него режим Запись, следующий разряд, поступая на четвертый вход стекового регистра 14 определяет для него режим Запись, следующий разряд, поступая на второй вход стековой памяти 10, определяет для него режим Чтение. По стробу, поступающему с второго выхода блока управления через синхронизирующий вход блока 2 на третьи входы буферных регистров 9, стековых регистров стековой памяти 10, подтверждаются режимы работающих в данный момент узлов блока 2, Одновременно по сигналу, поступающему с четвертого выхода блока 7 управления на синхронизирующий вход блока 1 ввода, происходит передача коэффициен- та с первого выхода блока 1 ввода через третий вход блока 2 и узел

элементов ИЛИ 11, на пятый вход буферного регистра 9,, где элементй запоминается. Одновременно вычис

13

ш-

ный элемент U

11

с выхода блока 3

деления через блок 4 поступает на второй вход блока 5 умножения, а через первый вход блока 2 и группу элементов ИЛИ 11. элемент U,,, поступает на первый вход стековой памяти 10,, где запоминается, да блока 2 элемент U

t

С первого вхо поступает

1

на пятый вход стекового регистра 14 где запоминается. Одновременно считывается коэффициент 1 ,;, и 5, с выхода стековой памяти 10 на пятый вход буферного регистра 9, , а через узлы 12 и 12J с третьего выхода блока 2 поступает на первый вход бло ка 5 умножения. Одновременно по сигналу Умножить, поступающему с шестого выхода блока 7 управления на управляющий вход блока 5 умноже1шя, происходит прием на входные регистры блока 5 умножения сомножителей 1,, и и , , На пятом шаге по сигналу, поступающему с четвертого выхода блока 7 управления на синхронизирующий вход блока 1 ввода, вводится элемент сЯ j, 1 , с первого выхода блока 1 ввода через третий вход блока 2 и узел 1 1J на первьш вход стековой памяти Юг, где запоминается

ю15 20 25

30

35

-

40

- д5 50

по сигналу Запись, поступающему с первого выхода блока 7 управления через первьш управляющий вход блока 2 на второй вход стековой памяти 10, и сигналу Строб, поступающему с второго выхода блока 7 управления через синхронизирующий вход блока 2 на третий вход стековой памяти 10. Одновременно в блоке умножения 5 . производится операция вычисления произведения П j,, 1,и,.

На шестом шаге по сигналу Ввод, поступающему с четвертого выхода блока 7 управления на синхронизирующий вход блока 1 ввода, происходит передача коэффициента а ii с первого выхода блока 1 ввода через третий вход блока 2, узлы 12, и 12 и третий выход блока 2 на первый вход блока 6 вычитания, на второй вход которого подается произведение П с выхода блока 5 умножения. Одновременно по сигналу Вычесть, приходящему с седьмого выхода блока 7 управления на управляюш й вход блока 6 вычитания, осуществляется прием уменьшаемого а j и вычитаемого П,, на входные регистры.

Таким образом заполняется вычислительный конвейер. Дальнейшая обработка информации осуществляется в соответствии с пошаговой временной диаграммой работы основных узлов устройства для решения СЛАУ, представленной на фиг. 7-9. В конце вычислений основные узлы устройства для решения СЛАУ находятся в состоянии,при котором во входном буфере блока 1 ввода хранятся коэффициенты исход- расширенной матрицы ГА I в,в бу- 9 , - диагональные

НОИ

ферном регистре элементы { 1 , ,

ЧЭ 44J ИЖ-

ней треугольной матрицы L, в буферном регистре 9 - остальные элементы этой матрицы в такой последовательности: 1,,, 1,,, 1,, 1,, 1,, ,

Т.е. по столбцам, в стековом регистре 14 , - недиагональные элементы верхней треугольной матрицы U в такой последовательности: f J . U,

и,.

и

з

и

2

и „ (по столбцам

обратном порядке), в стековом регист

ре

14, элементы у , у , у

выходном буфере блока 8 вывода - век-

У

3

2

тор результата x,j.

Автоматический этап работы устройства заканчивается после того,как

и

счетчик 24 узла 13 синхронизации блока 7 управления пересчитает 86 тактов (дпя выбранного примера), при этом состояние счетчика 24 соответствует состоянию блока клавишного набора 26 и с выхода компаратора 25 на R-вход RS-триггера 20 поступает сигнал Стоп, который останавливает работу генератора 21 прямоугольных импульсов.

Устройство для решения СЛАУ является конвейерным, синхронным вычислителем, так как при выборе основных принципов структурной организации устройства учтено, что решающим фактором повышения быстродействия является совмещение процессов обработки.

Формула изобретения

Устройство для решения систем линейных алгебраических уравнений, содержащее блок ввода, блок вывода, блок программного управления, блок буферной памяти, первый информационный выход блока ввода подключен к первому информационному входу блока буферной памяти, первый выход блока программного управления подключен к входу задания режима блока буферной памяти, отличающееся тем что, с целью увеличения производительности, оно содержит блок деле-

ния, блок умножения, блок вычитания, ной памяти, синхровходы буферных реблок элементов ЮШ, второй выход блока программного управления подключен к синхронизирующему входу блока буферной памяти, выход готовности блока ввода подключен к входам запуска 40 блока буферной памяти, блока пpoгpa г- много управления н блока вывода,третий выход блока программного управления подключен к синхронизирующему входу блока вывода, четвертый выход д блока программного управления подключен к синхронизирующему входу блока ввода, пятый, щестой и седьмой выходы блока программного управления подключены соответственно к синхро- ,.. низирующим входам блоков деления,yir- ножения и вычитания, первый информационный выход блока буферной памяти подключен к первому информационному входу блока деления, второй информа- ционный выход - к первому в;соду блока элементов ШШ, третий информгщион- ный выход - к второму информационному входу блока деления и первым ин

гистров с первого по четвертый, а также первого и второго стековых регистров подключены поразрядно к синхронизирующему входу блока буферной памяти, входы задания режима буферных регистров с первого по четвертый первой и второй стековых памятей, первого и второго стековых регистров и первый вход узла элементов И поразрядно подключены к входу задания режима блока буферной памяти,информационные входы первого, второго и третьего буферных регистров,первого стекового регистра первый вход первого узла элементов ИЛИ первой группы, первый вход второго узла элементов ИЛИ первой группы и первый вход первого узла элементов ИЛИ второй группы поразрядно подключены к выходу третьего узла элементов ИЛИ первой группы, первый вход которого подключен к второму информационному входу блока буферной памяти, а второй вход - к первому информационному

U656

ю

15

20

2530 ,

12

формационным входам блока умножения и блока вычитания, четвертый информационный выход - к информационному входу блока вывода, выход результата блока деления подключен к второму входу блока элементов ИЛИ и третьему информационному входу блока буферной памяти, выход блока элементов ИЛИ подключен к второму информационному входу блока умножения, выход результата которого подключен к второму информационному входу блока вычитания, выход результата которого подключен к второму информационному входу блока буферной памяти, причем блок буферной памяти содержит четыре буферных регистра, две стековые памяти, два стековых регистра, четыре узла .элементов ИЛИ первой группы, три узла элементов ИЛИ второй группы и узел элементов И, входы запуска с первого по четвертый буферных регистров и первого н второго стековых регистров подключены поразрядно к входу запуска блока буферной памяти, первые установочные входы первого и четвертого буферных регистров, первой и второй стековых памятей подключены к первому установочному входу блока буферной памяти, вторые установочные входы второго и третьего буферных регистров подключены к второму установочному входу блока буфергистров с первого по четвертый, а также первого и второго стековых регистров подключены поразрядно к синхронизирующему входу блока буферной памяти, входы задания режима буферных регистров с первого по четвертый первой и второй стековых памятей, первого и второго стековых регистров и первый вход узла элементов И поразрядно подключены к входу задания режима блока буферной памяти,информационные входы первого, второго и третьего буферных регистров,первого стекового регистра первый вход первого узла элементов ИЛИ первой группы, первый вход второго узла элементов ИЛИ первой группы и первый вход первого узла элементов ИЛИ второй группы поразрядно подключены к выходу третьего узла элементов ИЛИ первой группы, первый вход которого подключен к второму информационному входу блока буферной памяти, а второй вход - к первому информационному

313

входу блока буферной памяти, первый вход четвертого узла элементов ИЛИ первой группы, второй вход первого узла элементов ИЛИ первой группы,ин формационный вход первой стековой памяти, информационный вход второй стековой памяти подключены к третьему информационному входу блока буферной памяти, первый, второй, третий и четвертый информационные выходы блока буферной памяти подключены соответственно к выходу первого буферного регистра, выходу второго стекового регистра, выходу второго узла элементов второй группы, к выходу узла элементов И, второй вход которого подключен к выходу первого узла элементов ИЛИ первой группы, выход второго буферного регистра подключен к вторым входам второго и четвертого узлов элементов И)Ш первой группы, информационный вход второго стеково

14

го регистра подключен к выходу чет- вертого узла элементов ИЛИ первой группы, первый, второй входы третьего узла элементов ИЛИ второй группы подключены соответственно к выходам первой стековой памяти и четвертого буферного регистра, третий вход третьего узла элементов ИЛИ второй группы и информационный вход «leTвертого буферного регистра подключены к выходу первого стекового регистра, второй и третий выходы первого узла элементов ИЛИ второй группы подключены к выходам соответственно третьего буферного регистра и второго стекового регистра, первый, второй и третий входы второго узла элементов ИЛИ второй группы подключены соответственно к выходу второго узла элементов ИЛИ первой группы, выходу третьего узла элементов ИЛИ второй группы и к выходу первого узла элементов ИЛИ второй группы.

Фиг.д

Фиг Л

Фиг. 5

Фиг. 6

Фиг. 7

Фиг. 8

| Устройство для решения систем линейных алгебраических уравнений | 1980 |

|

SU940167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий C РАзРЕжЕННОйМАТРицЕй | 1978 |

|

SU813444A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-30—Публикация

1985-04-29—Подача